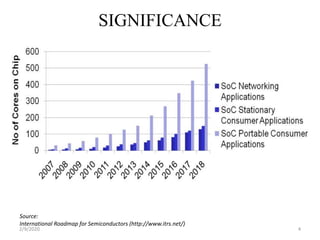

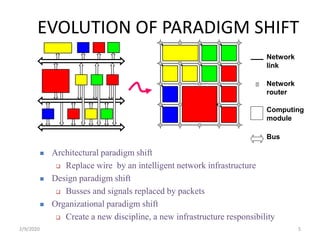

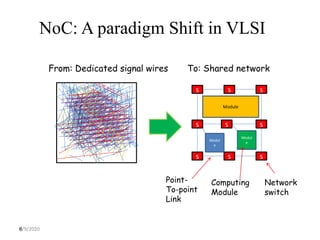

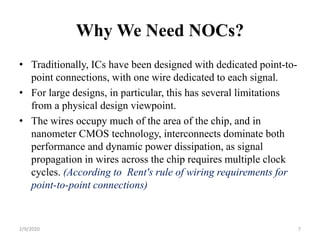

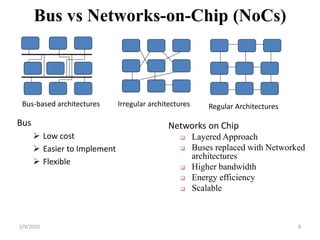

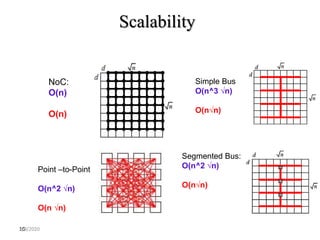

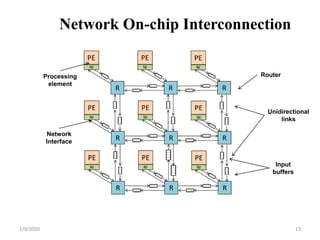

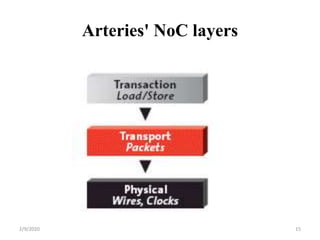

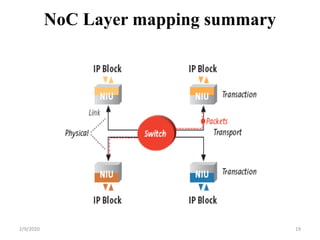

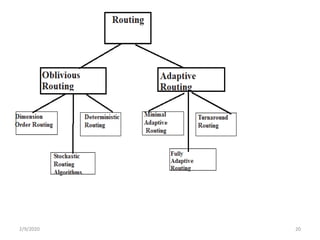

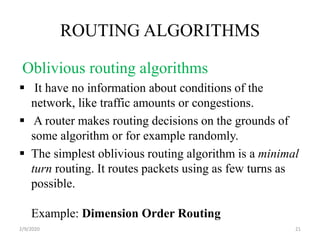

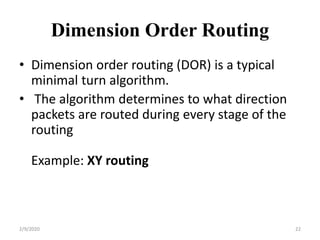

The document discusses network-on-chip (NoC) technology. NoC uses a packet switched network approach to connect intellectual property cores on a chip. It provides advantages over traditional bus-based interconnects like higher bandwidth, energy efficiency, and scalability. NoCs operate using a layered approach with physical, transport, and transaction layers. Common routing algorithms for NoCs include dimension order routing, XY routing, fully adaptive routing, and minimal adaptive routing. NoCs allow for modular and reconfigurable integration of IP cores from different vendors.