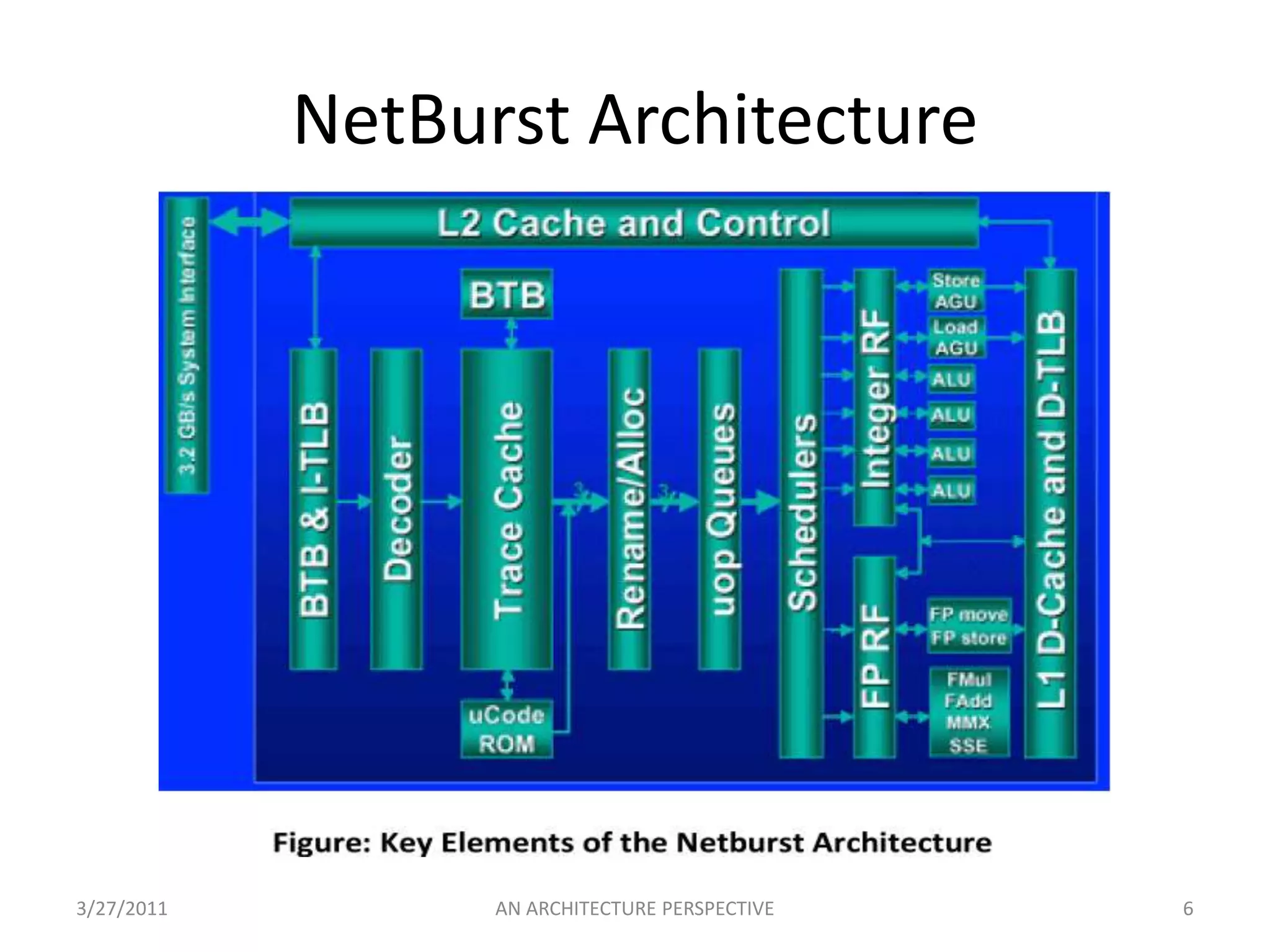

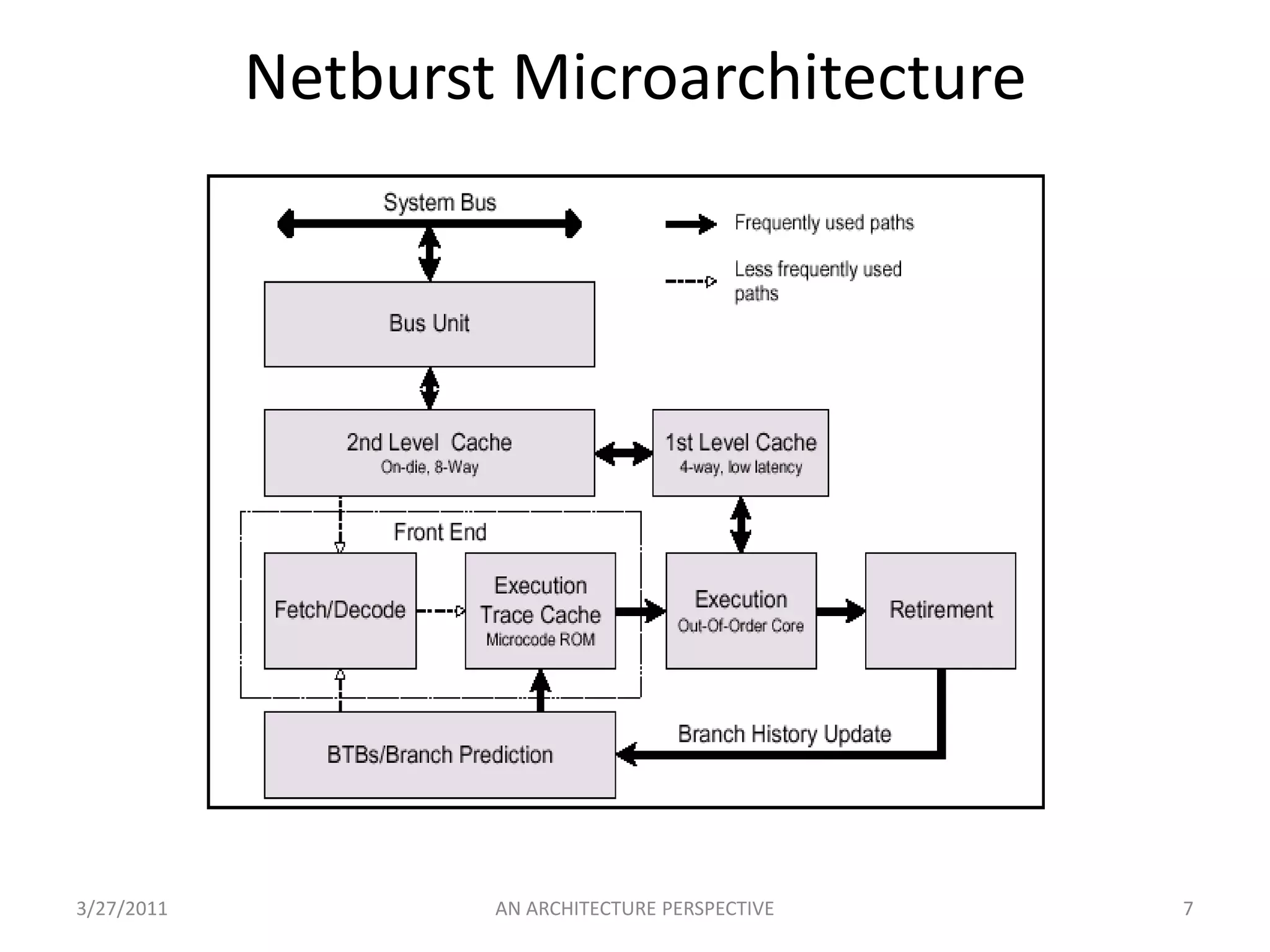

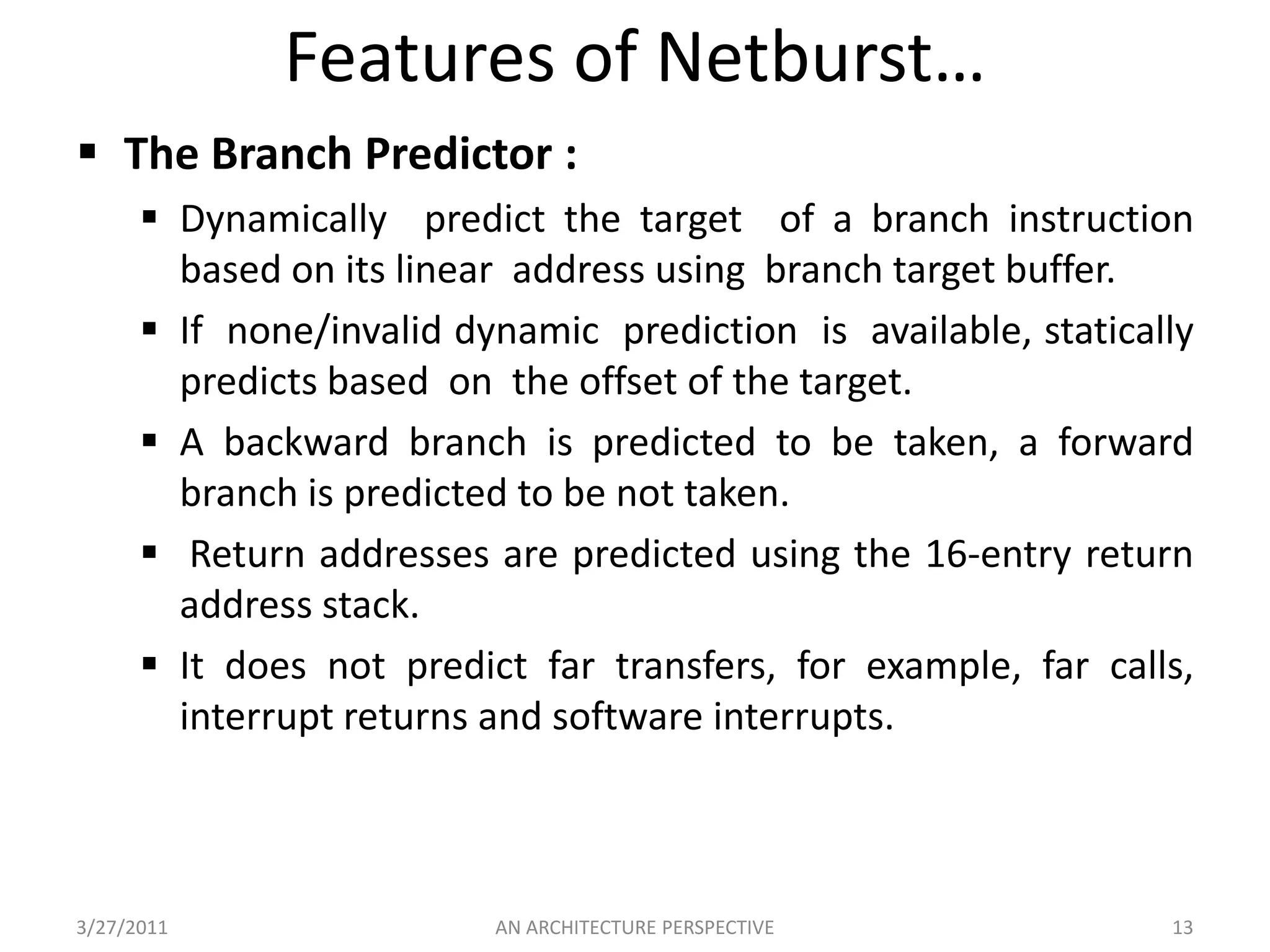

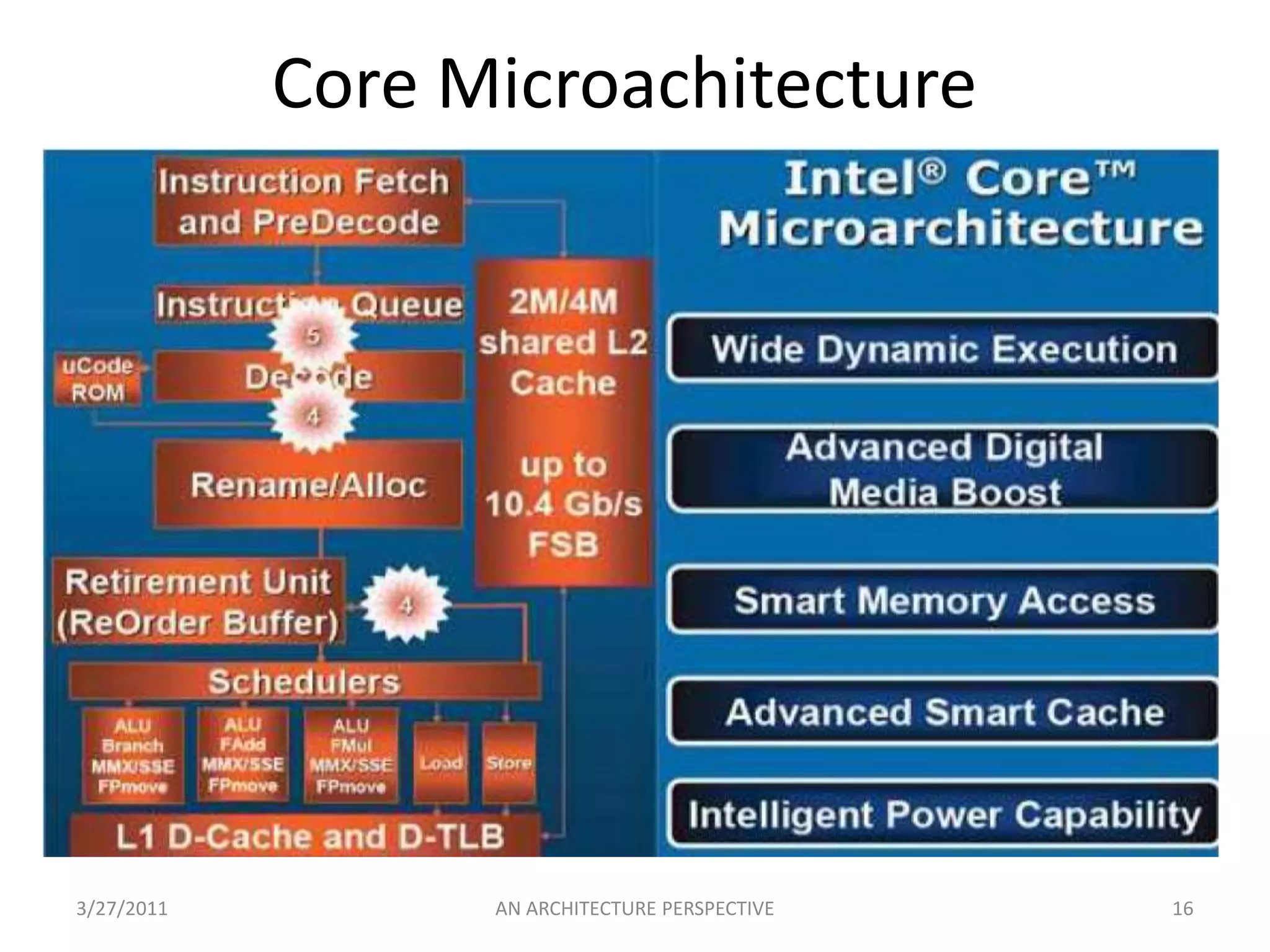

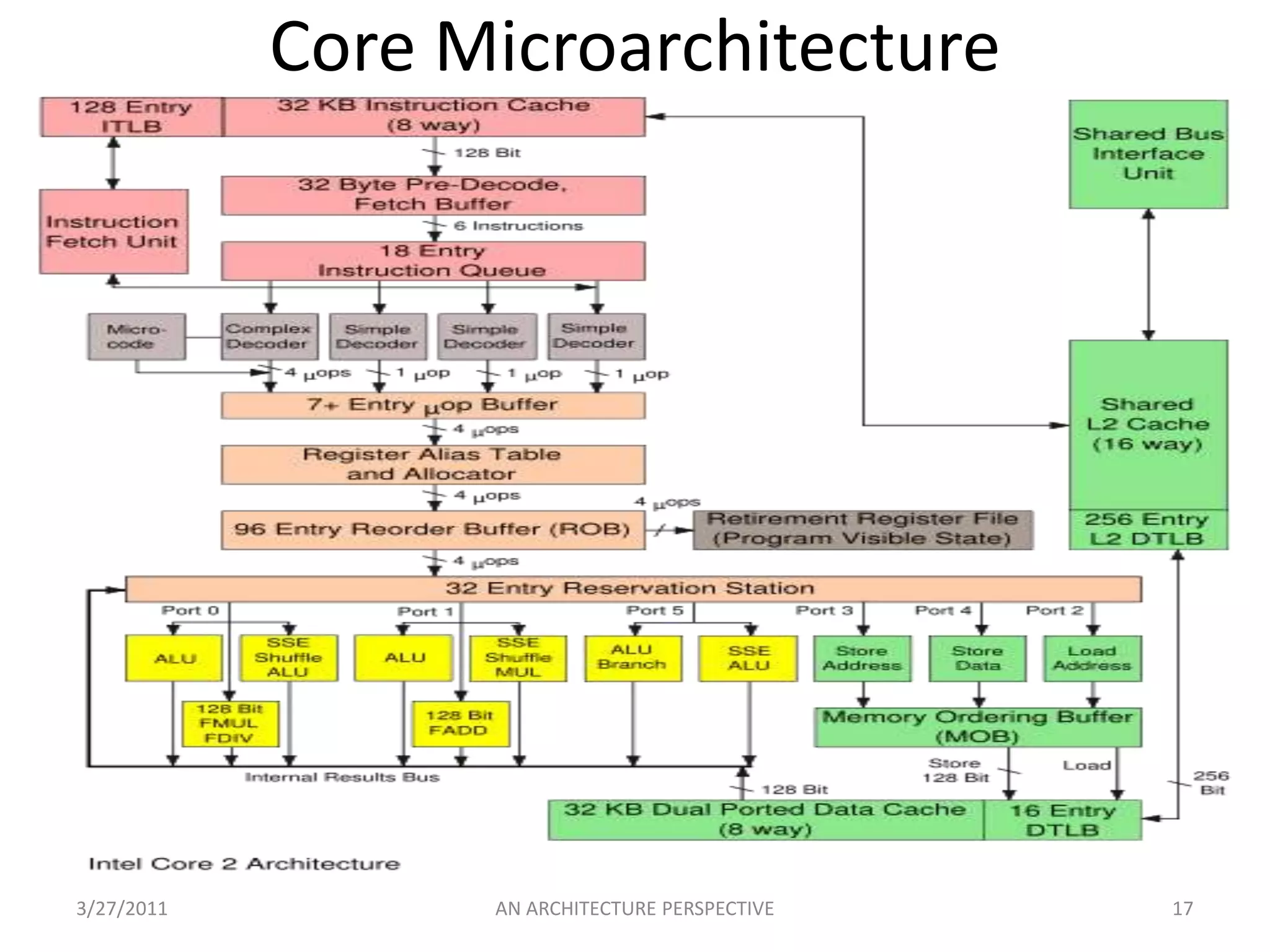

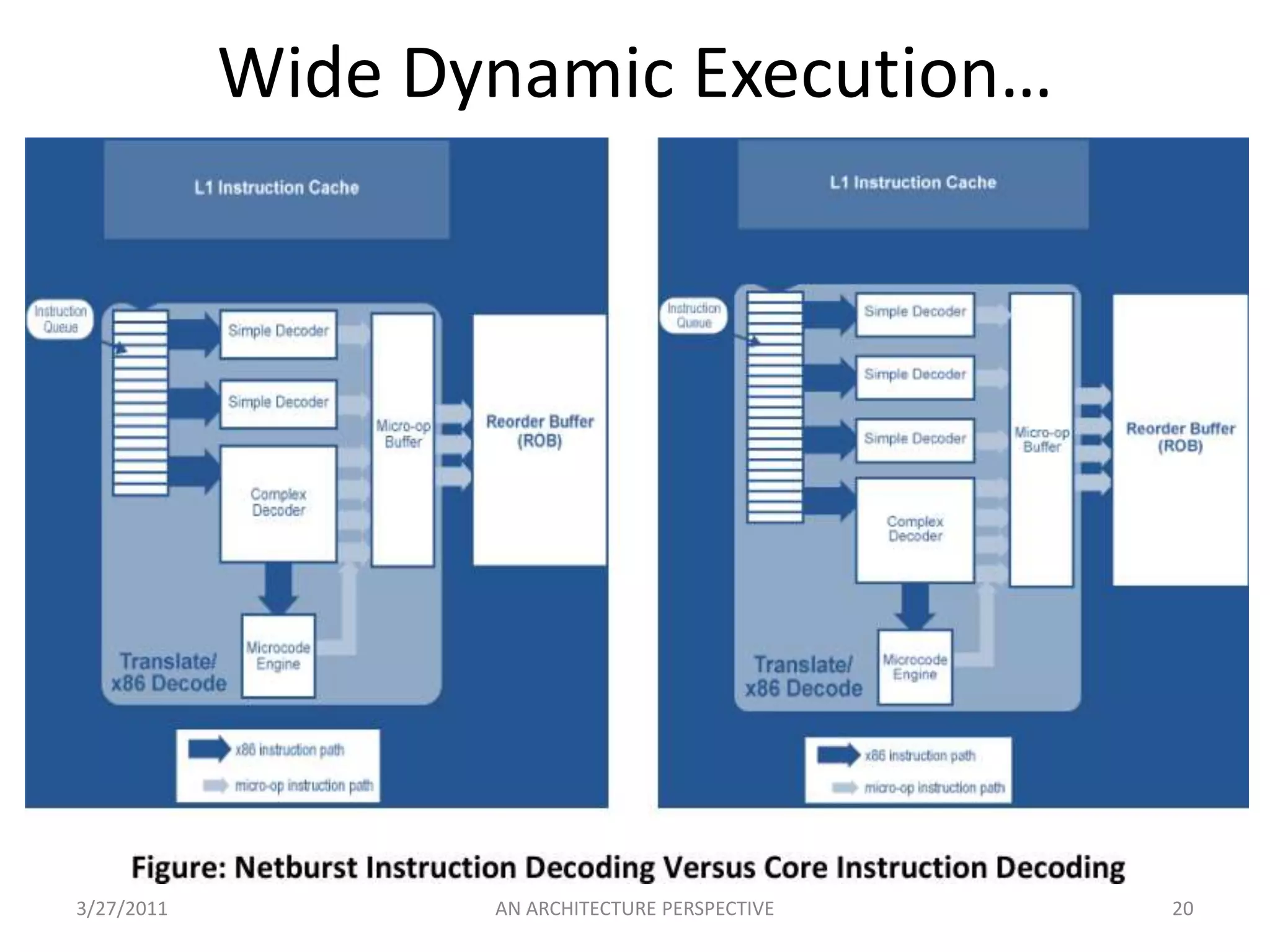

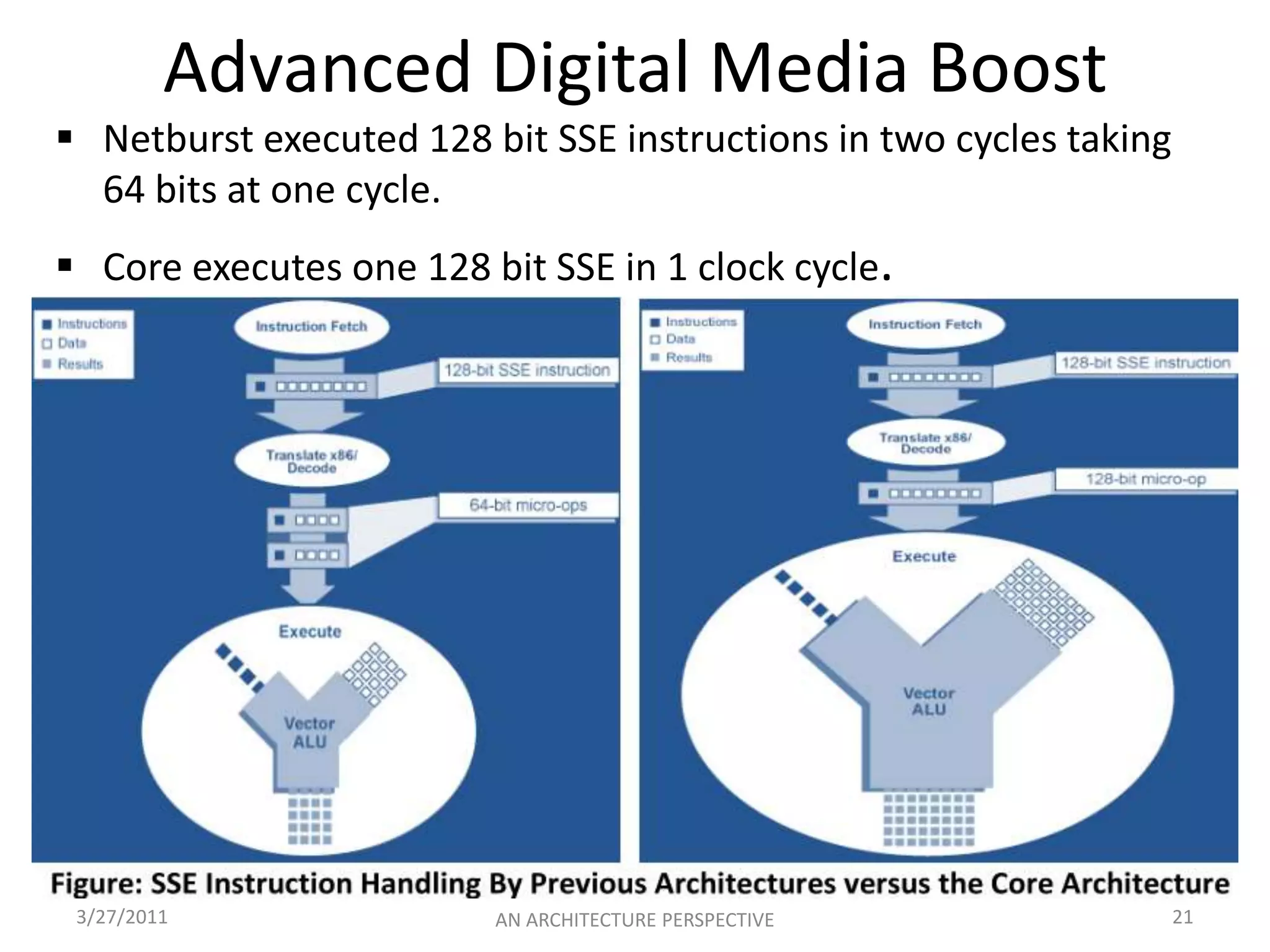

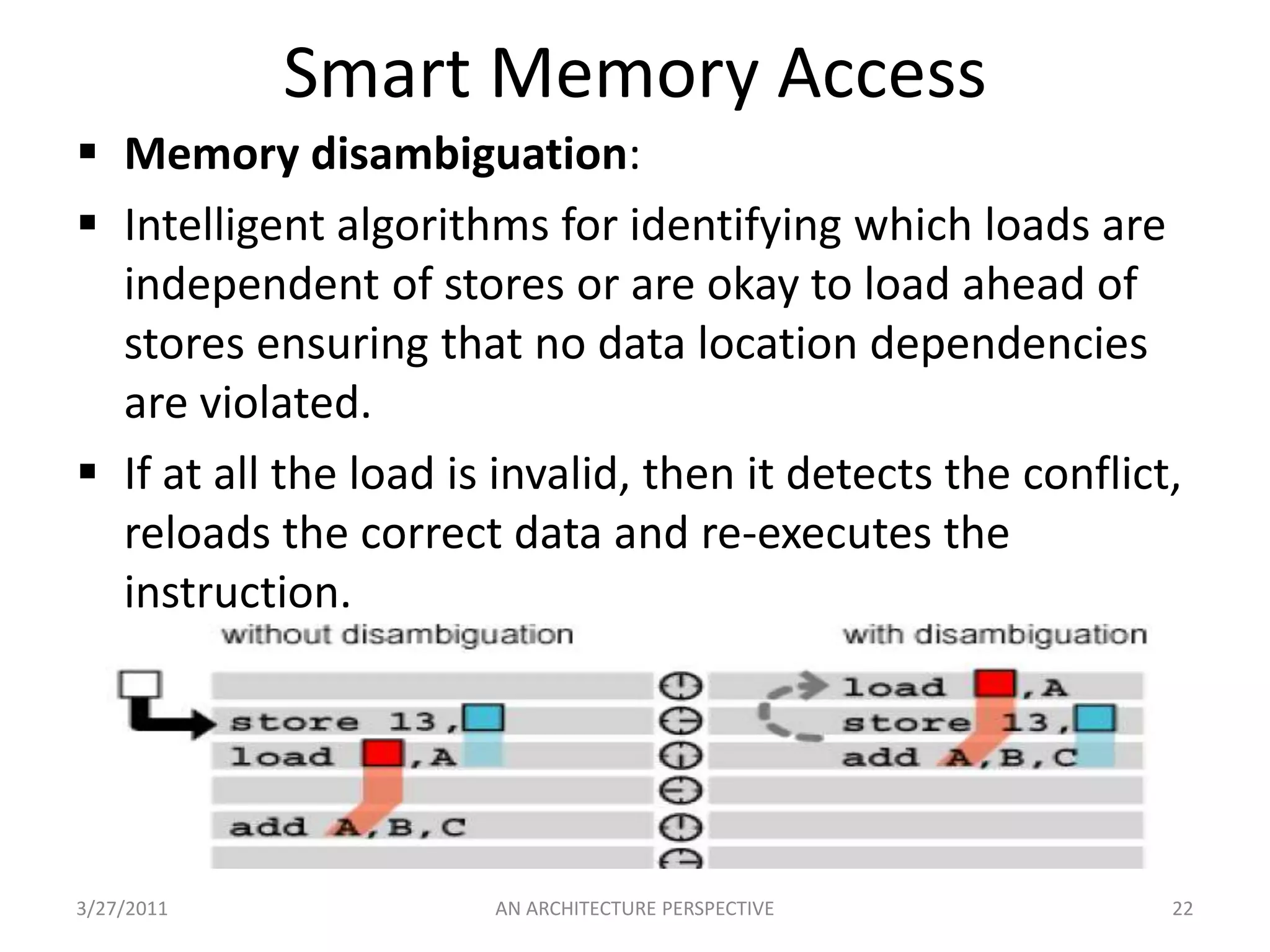

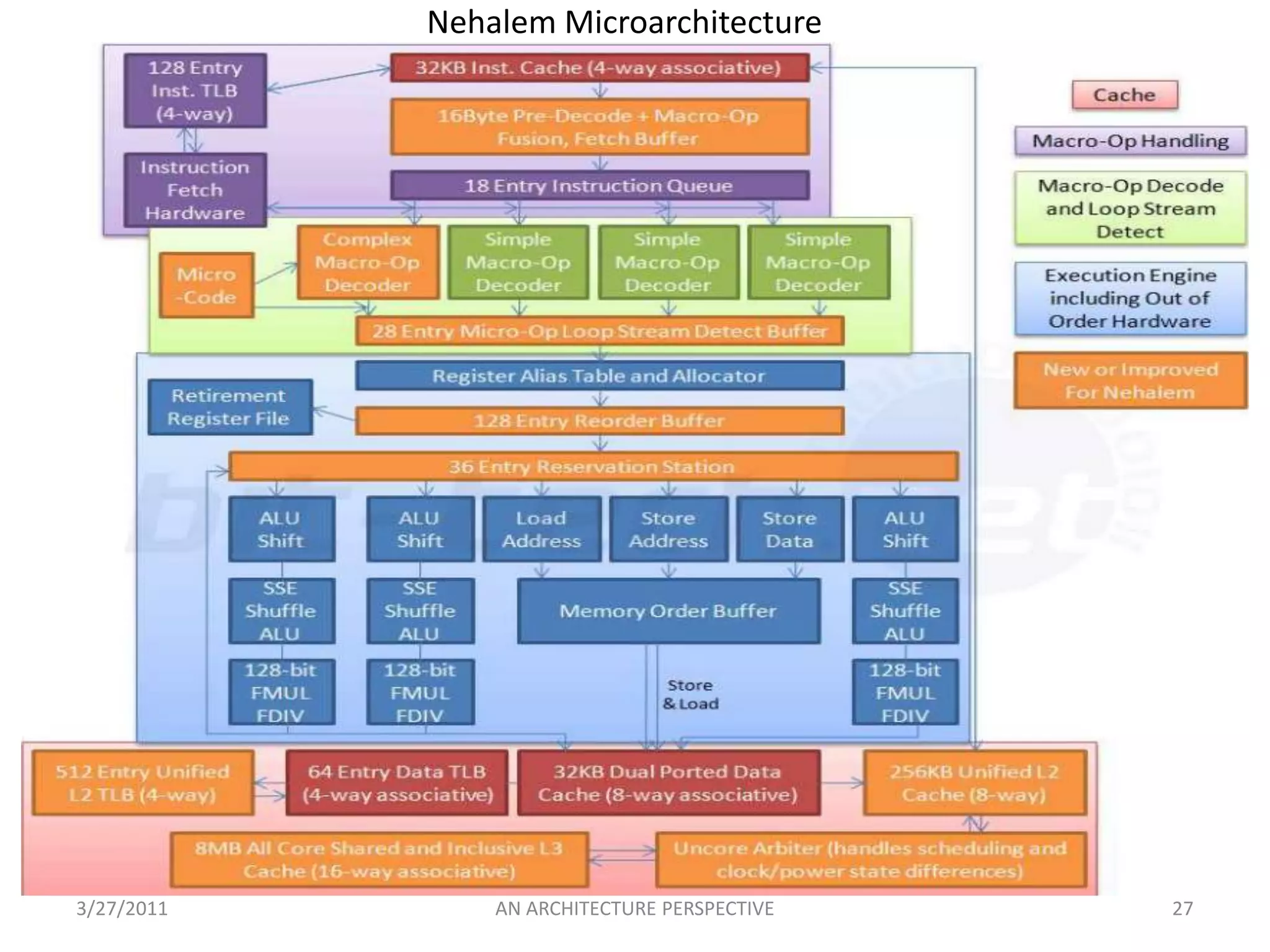

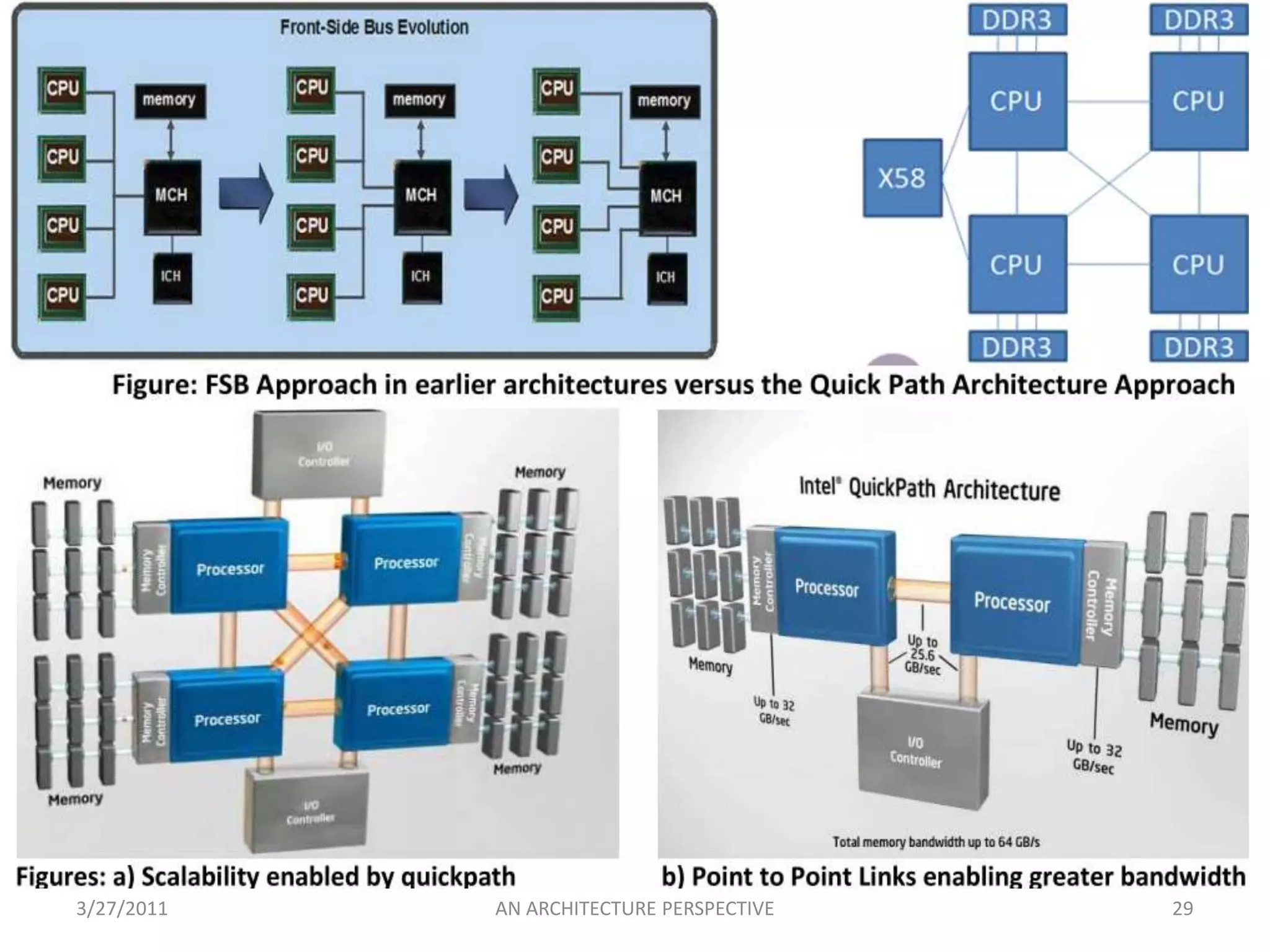

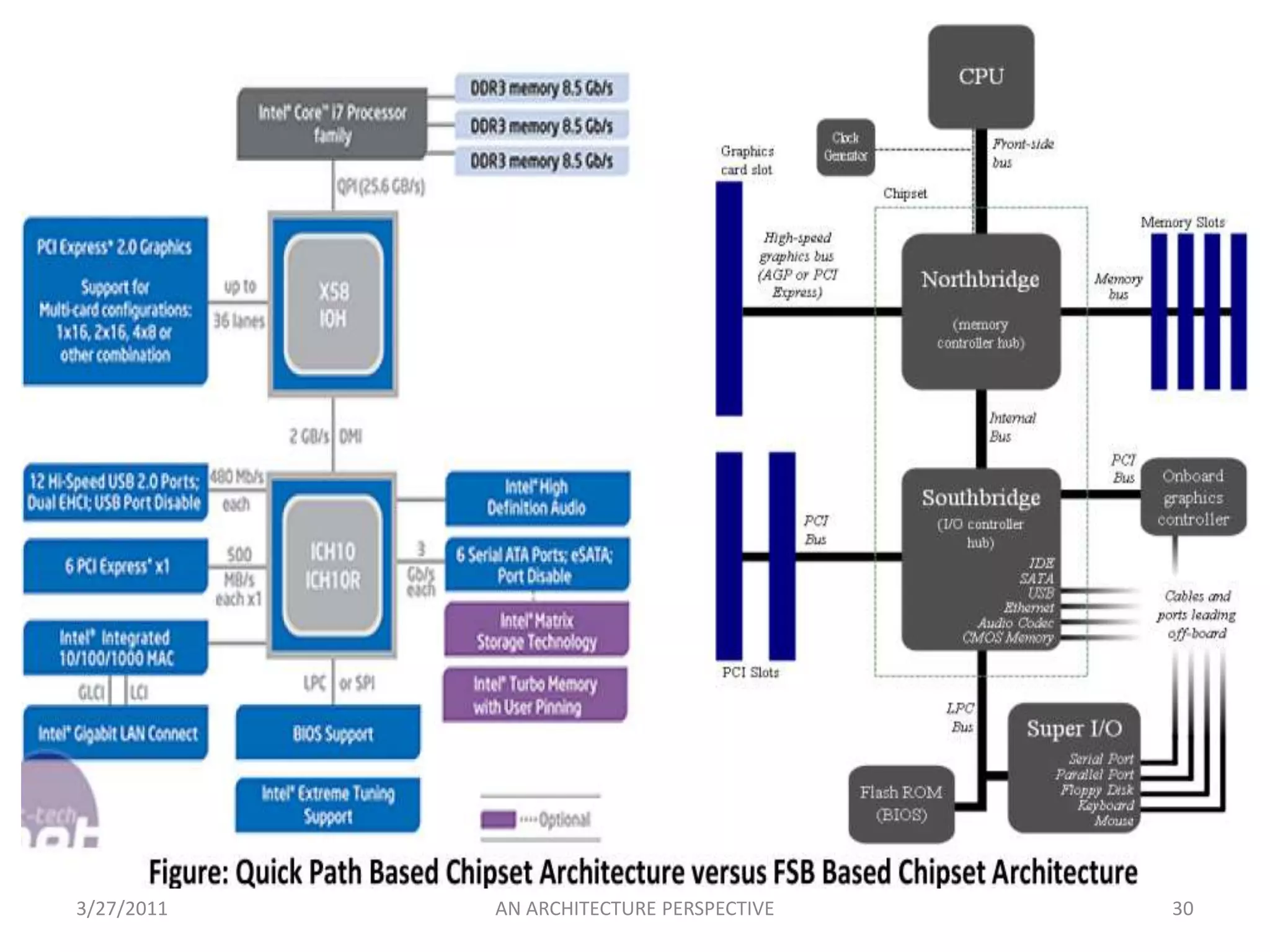

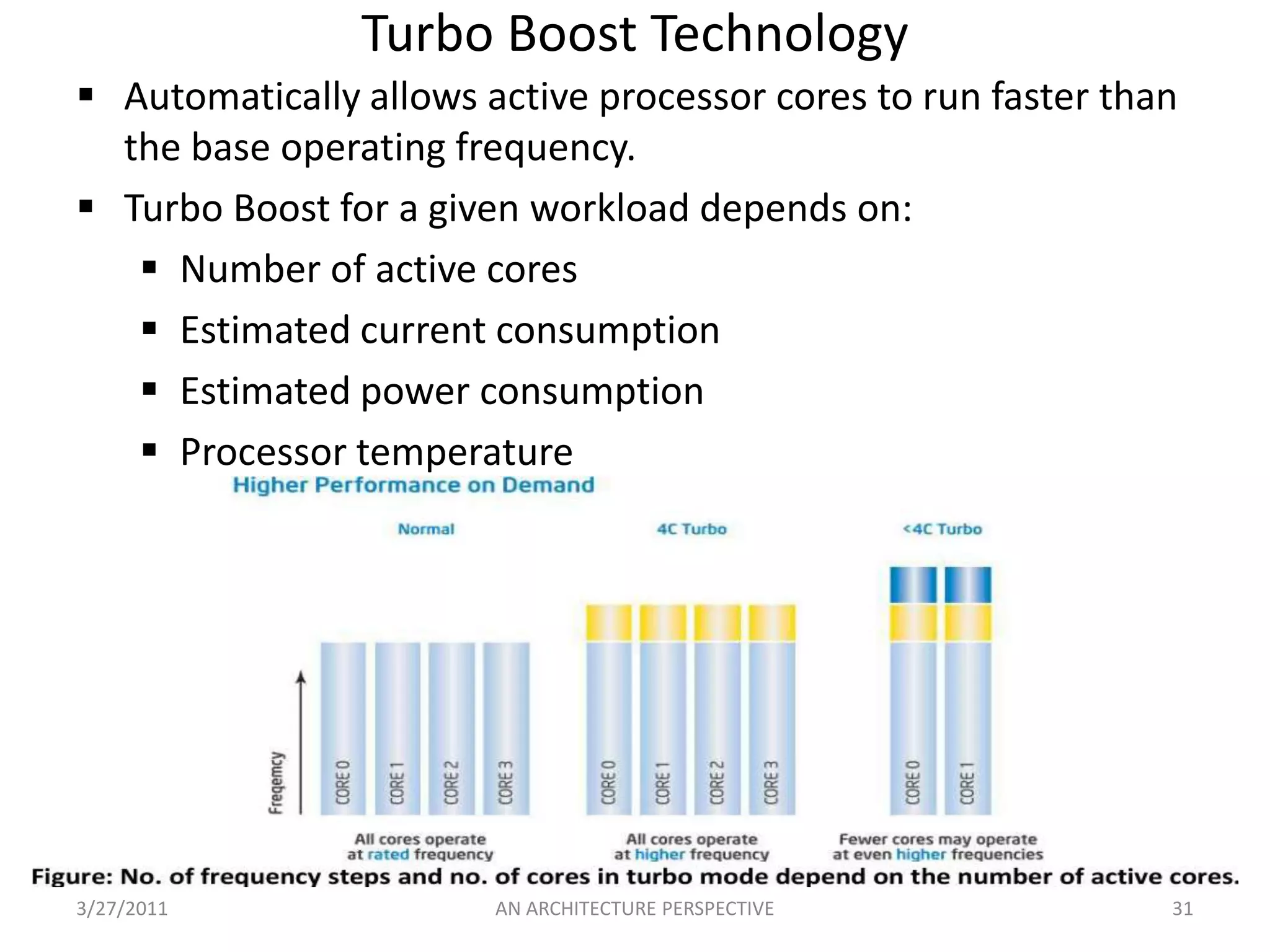

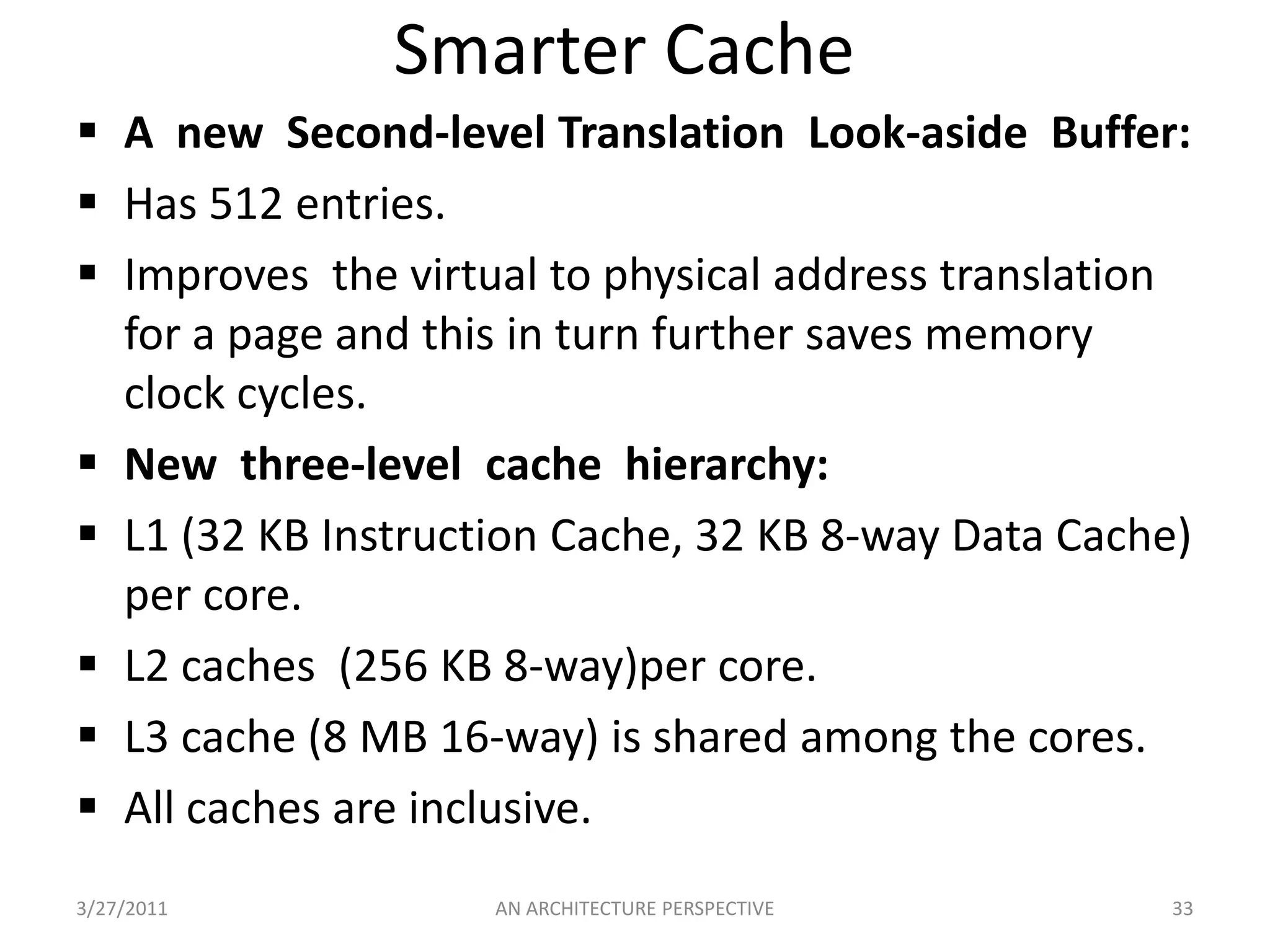

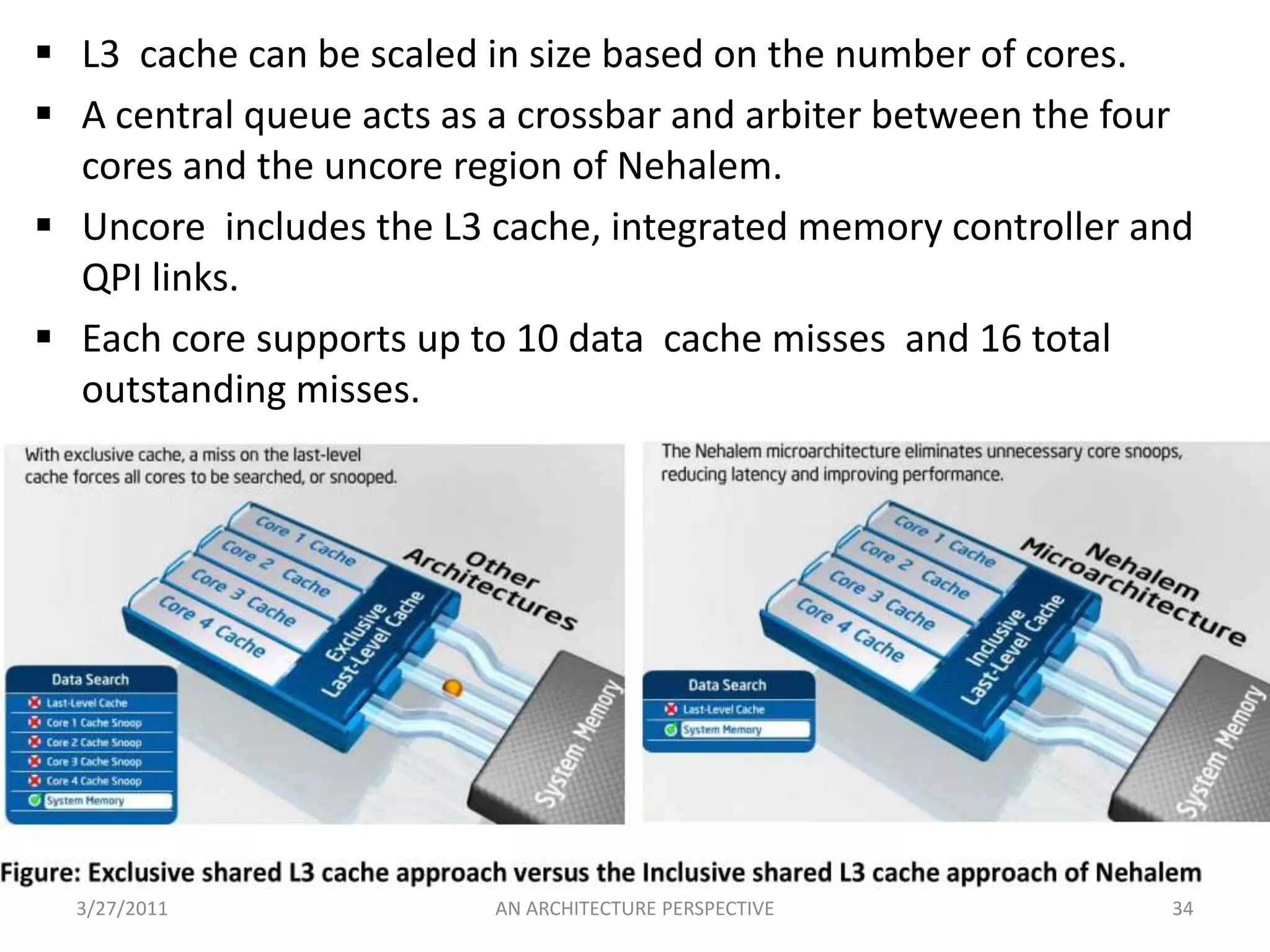

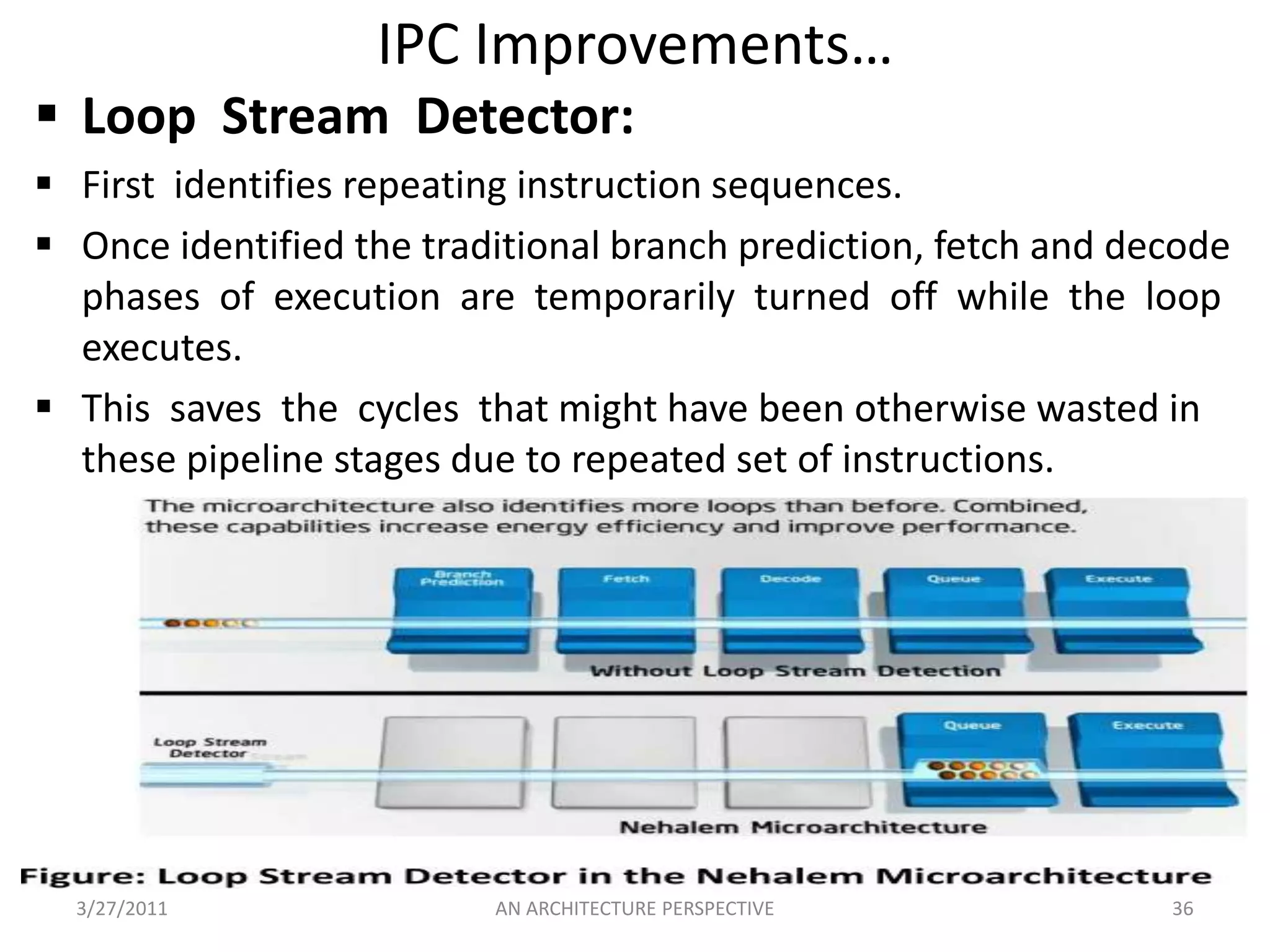

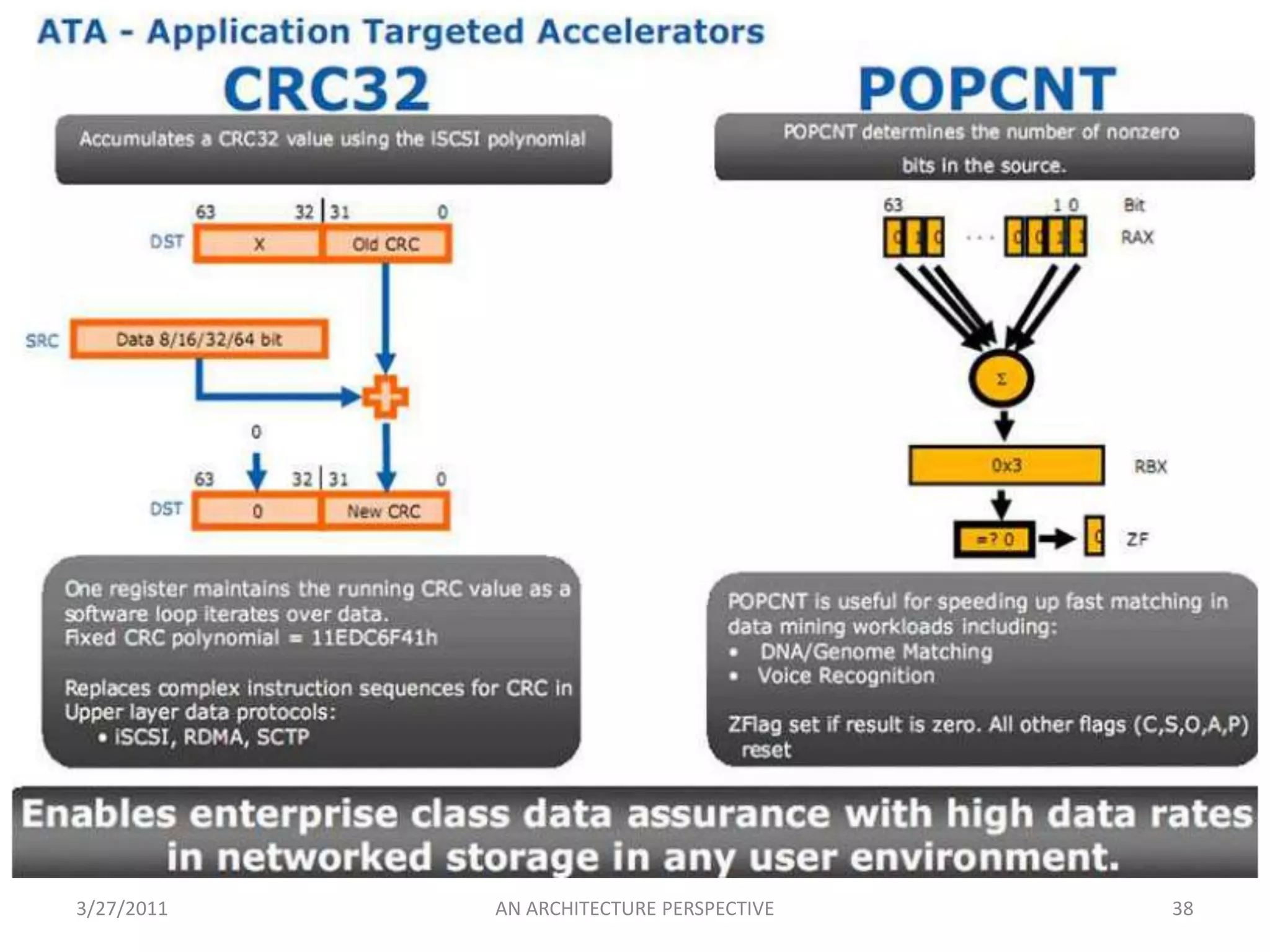

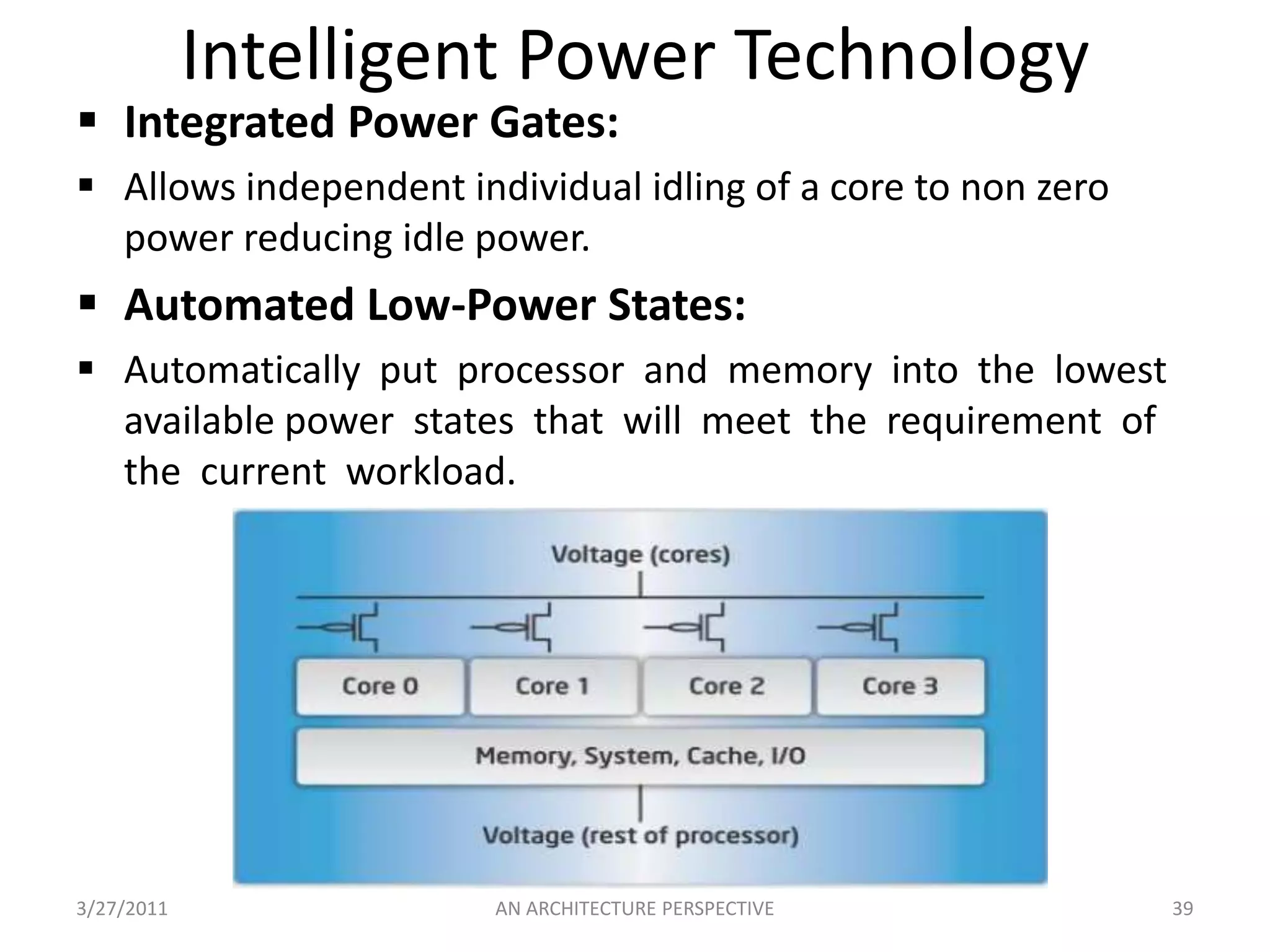

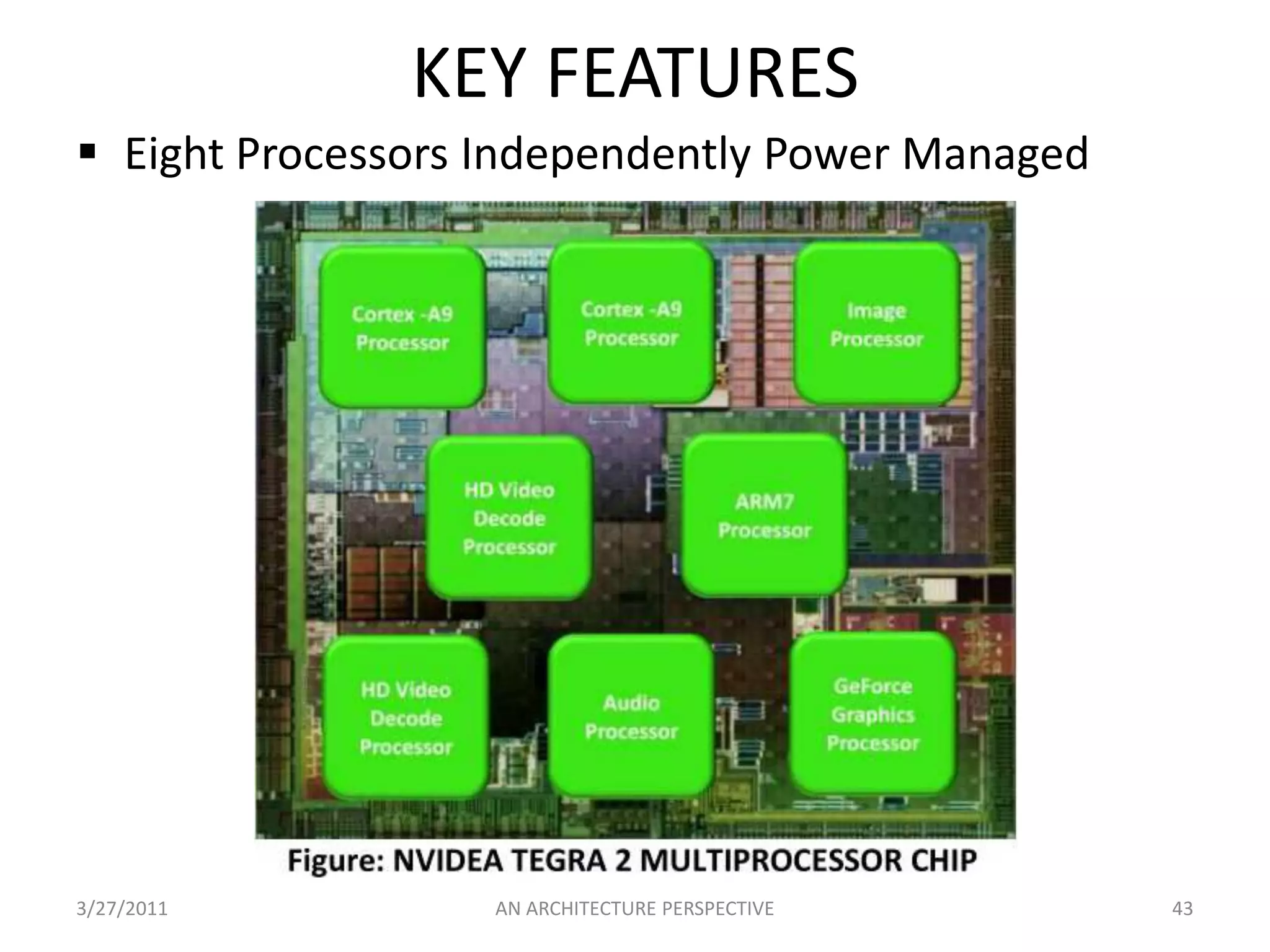

The document provides an in-depth analysis of Intel's microprocessor architectures, including NetBurst, Core, and Nehalem, discussing features like hyper-threading, advanced branch prediction, and memory management. It also gives a sneak peek at Nvidia's Tegra GPU, emphasizing its specialized processors for graphics and video tasks. Various architectural improvements aim to enhance performance, energy efficiency, and virtualization support across these platforms.