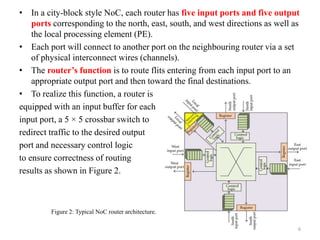

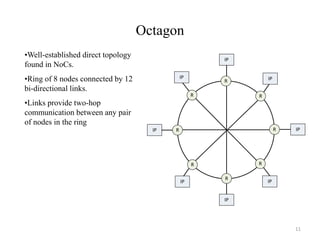

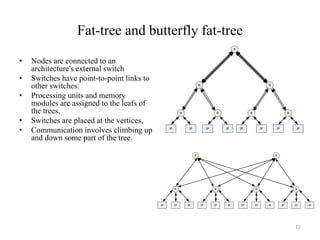

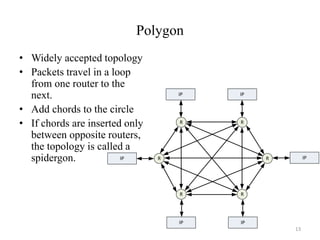

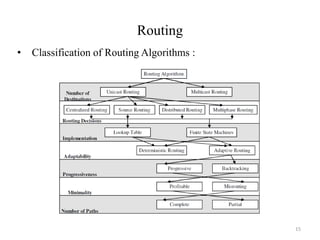

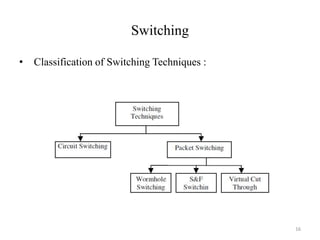

The presentation discusses Network on Chip (NoC), which is a communication subsystem on an integrated circuit that enhances scalability and power efficiency in systems on chip. Key features include simplified hardware for routing, improved synchronization, and higher operating frequencies, along with various architectural topologies such as mesh and torus. The field of NoC is still emerging, with many opportunities for research and optimization.