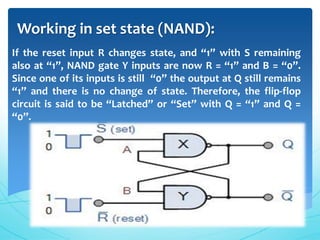

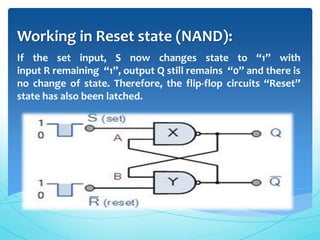

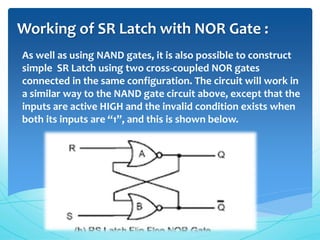

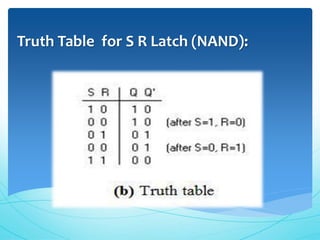

The document describes the workings of an SR latch circuit. An SR latch consists of two cross-coupled NOR or NAND gates with inputs named S (Set) and R (Reset). The circuit can be in one of two states: the set state where output Q=1 and Q'=0, or the reset state where Q=0 and Q'=1. When S=1 and R=0, the circuit enters the set state by forcing Q to 1 and Q' to 0. When R=1 and S=0, the circuit enters the reset state with Q=0 and Q'=1. Once set or reset, the state will be maintained even if the input changing it toggles again.