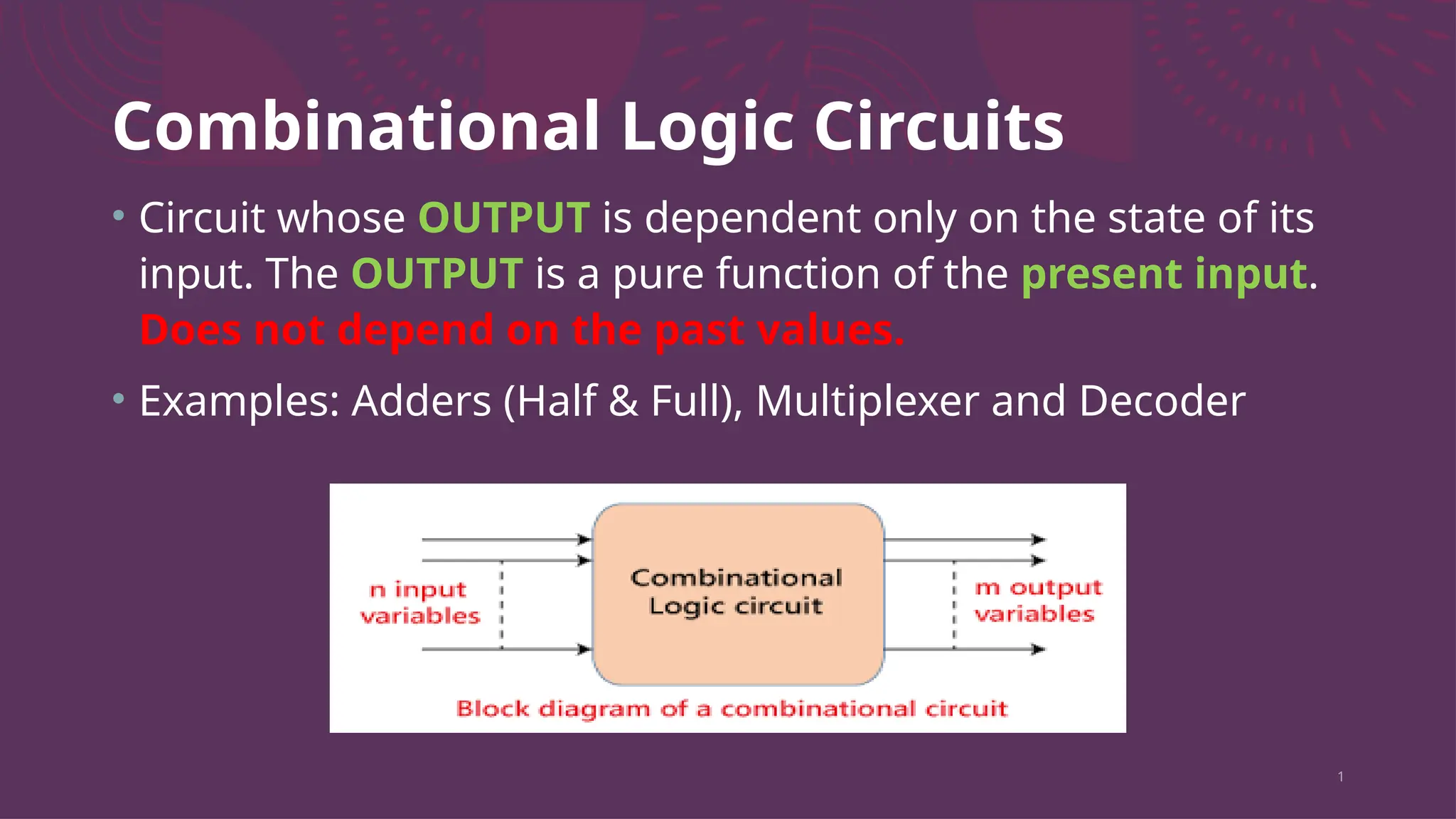

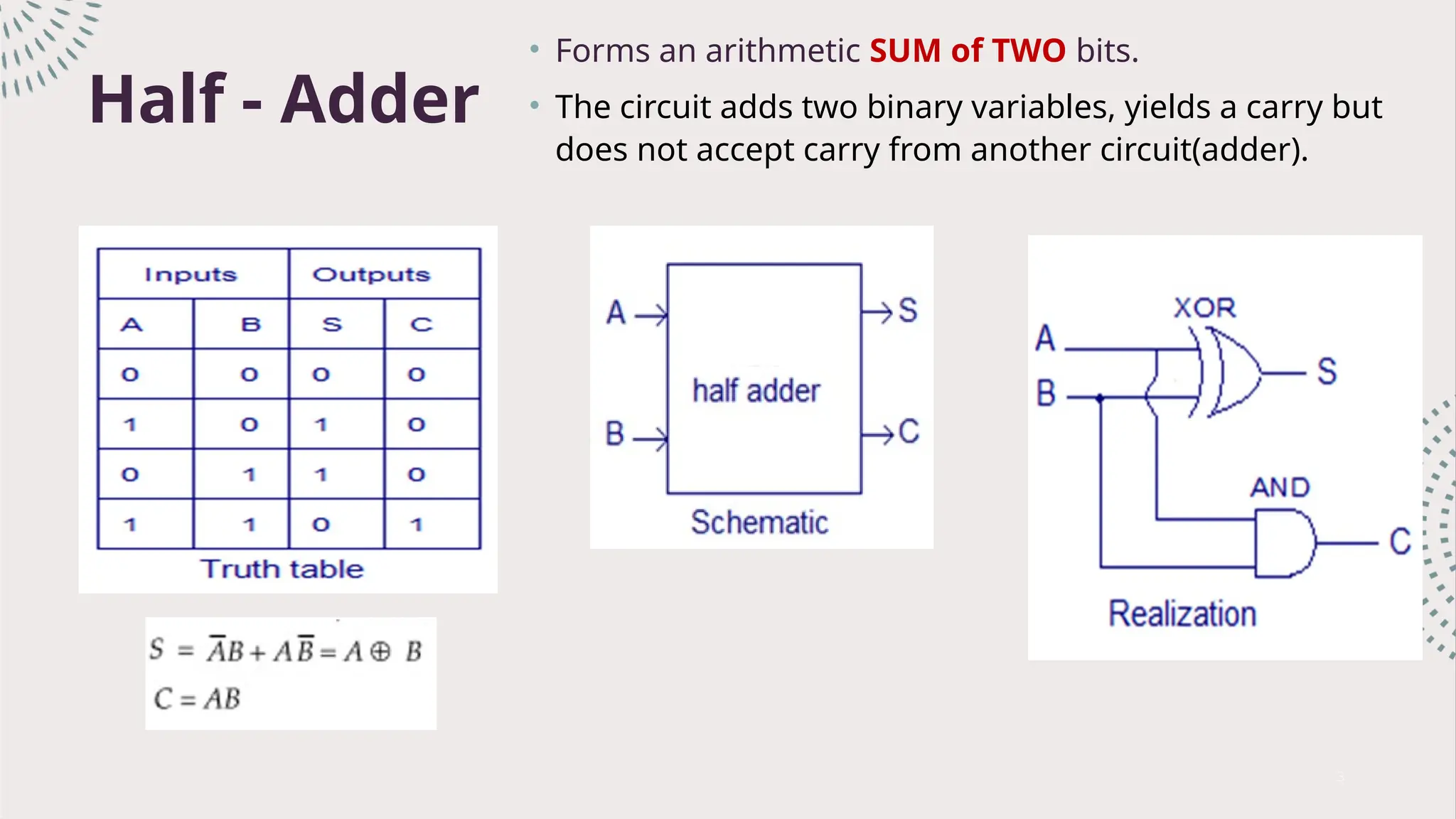

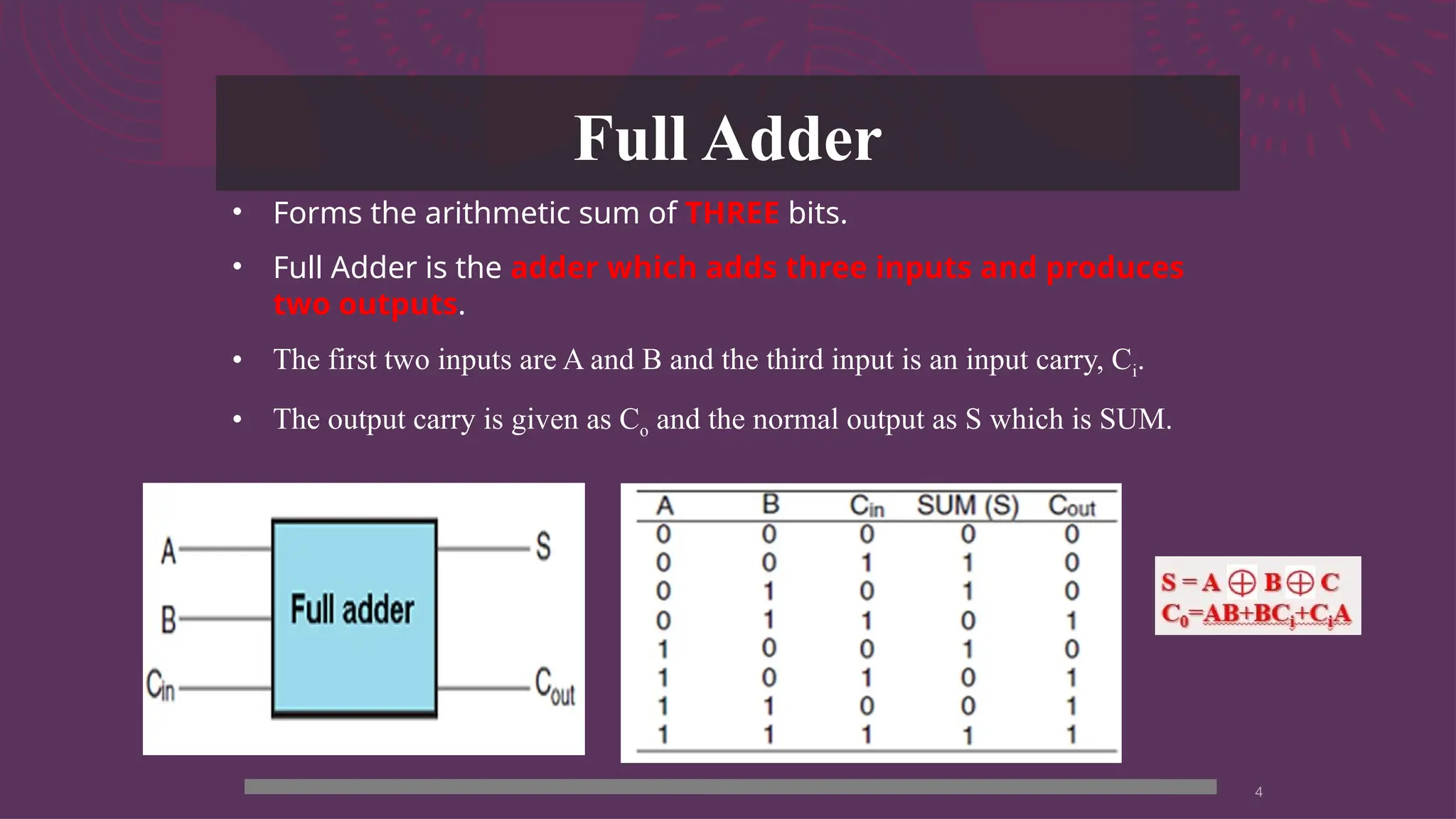

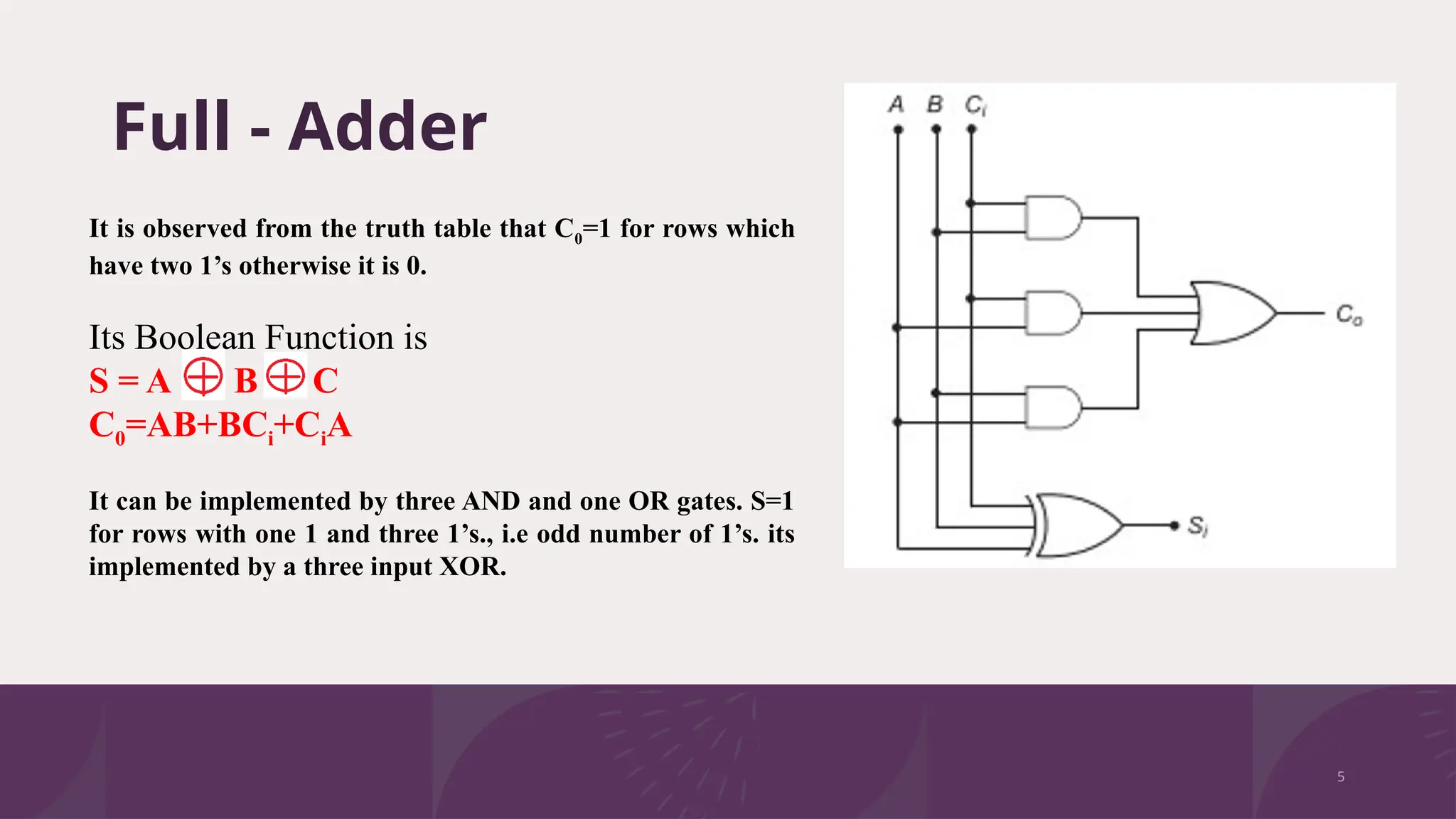

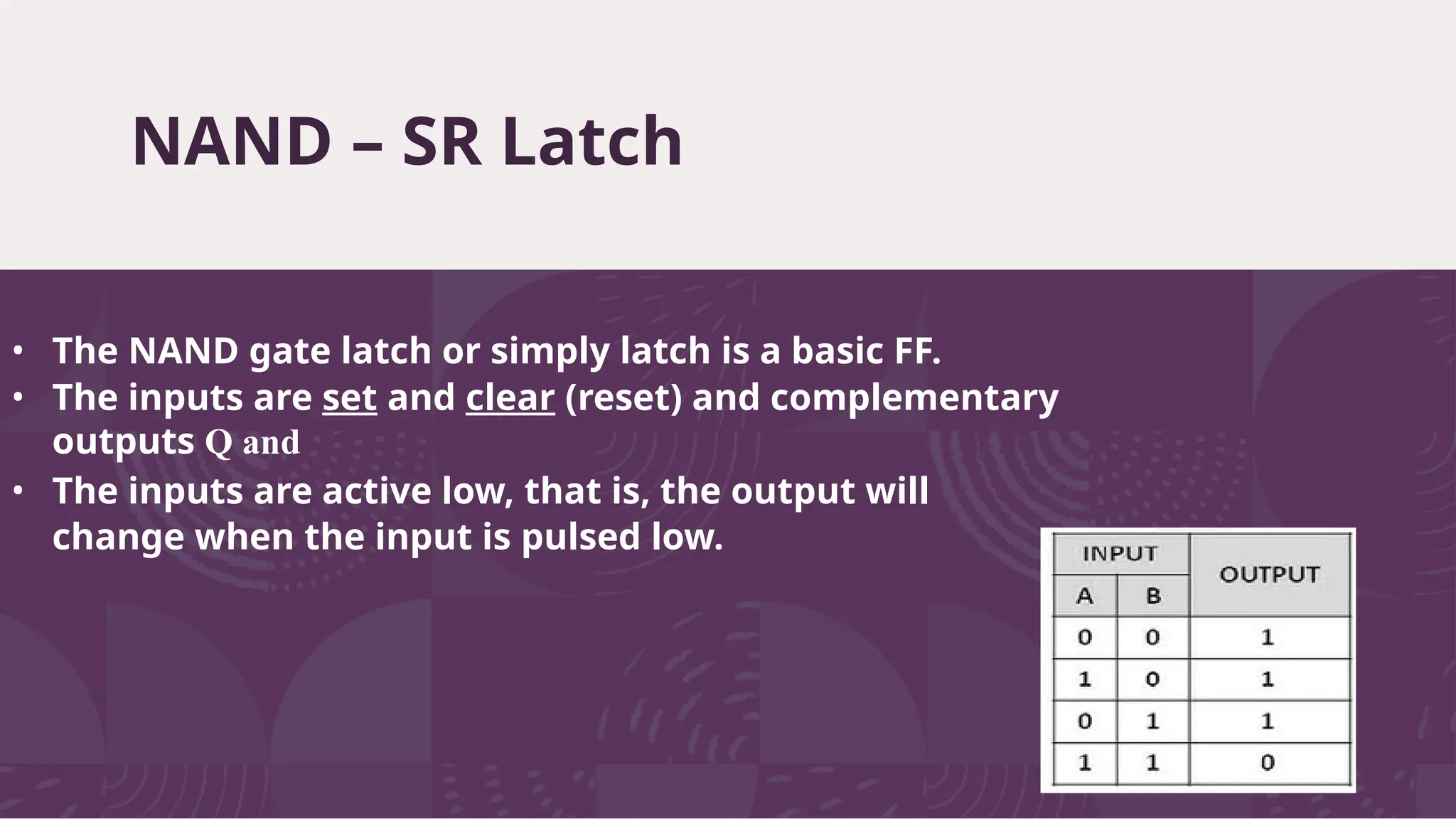

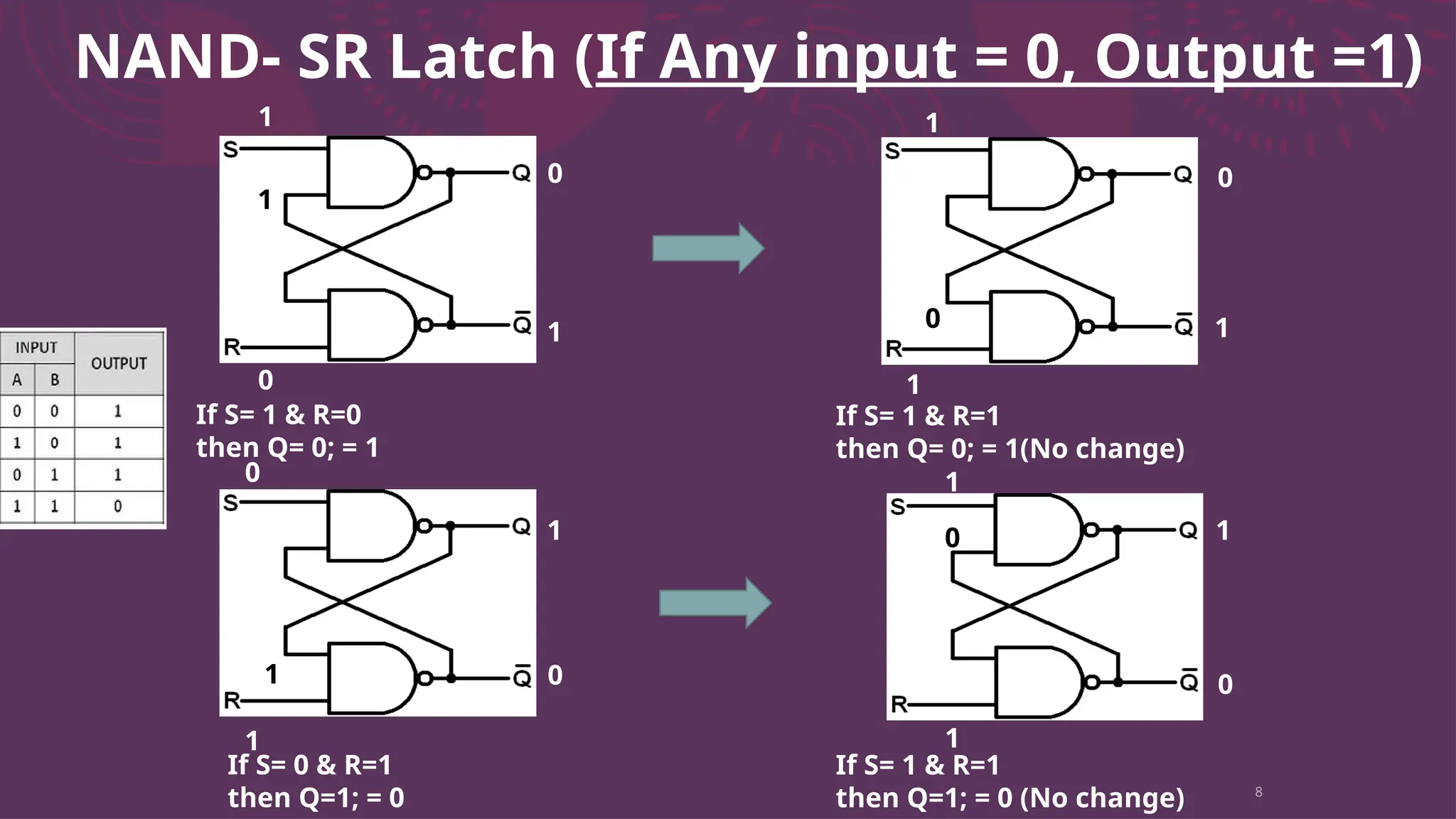

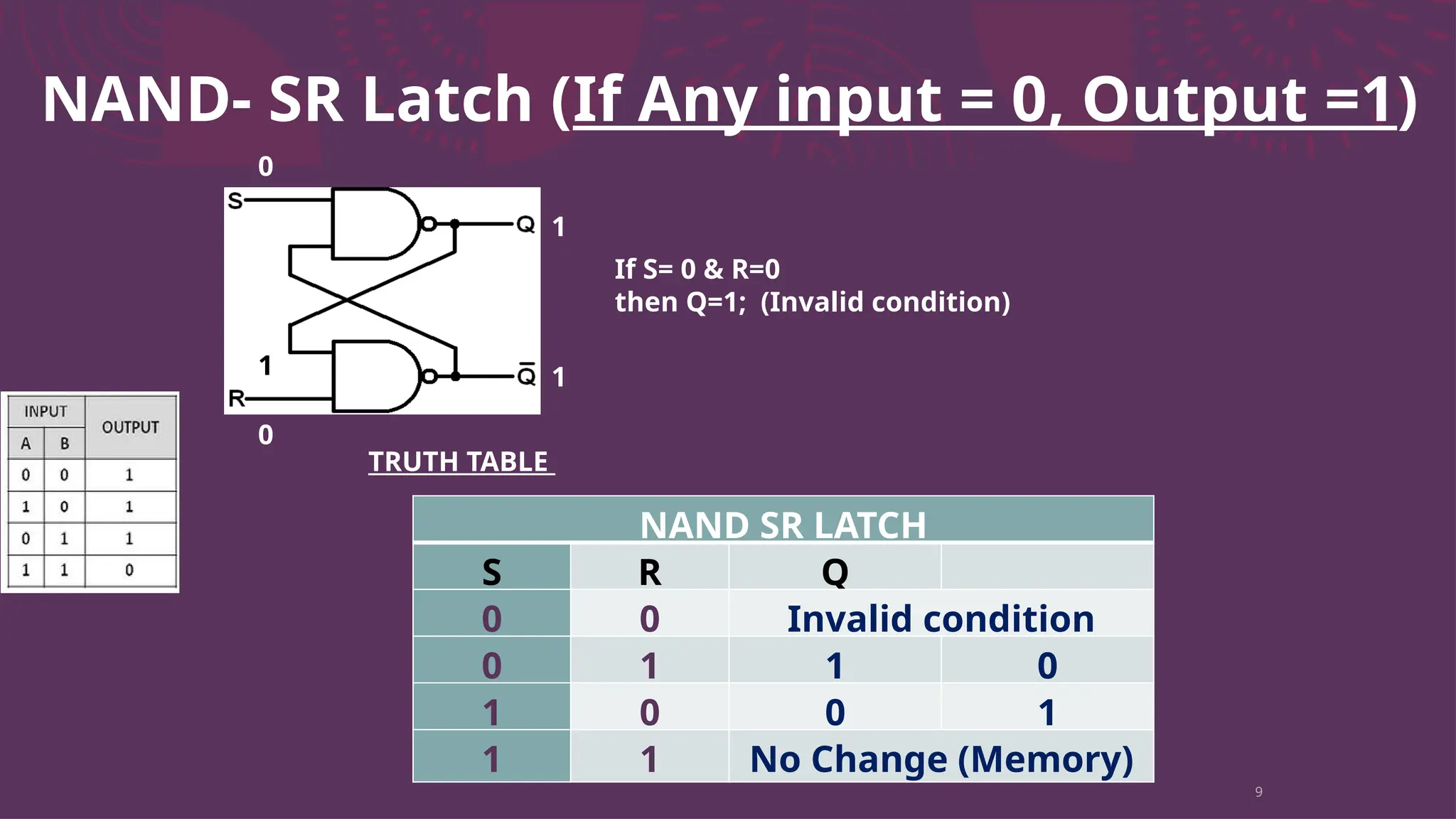

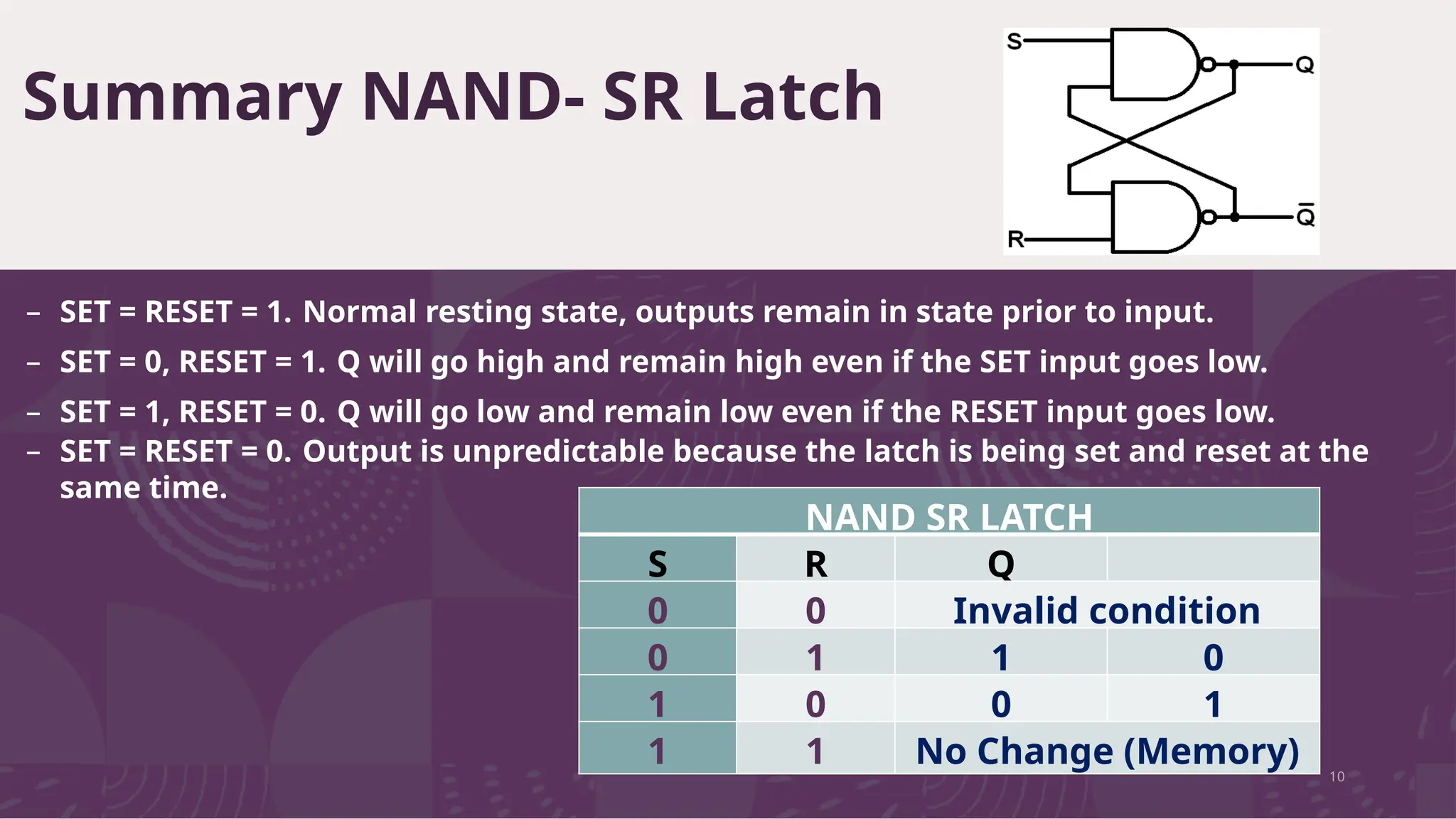

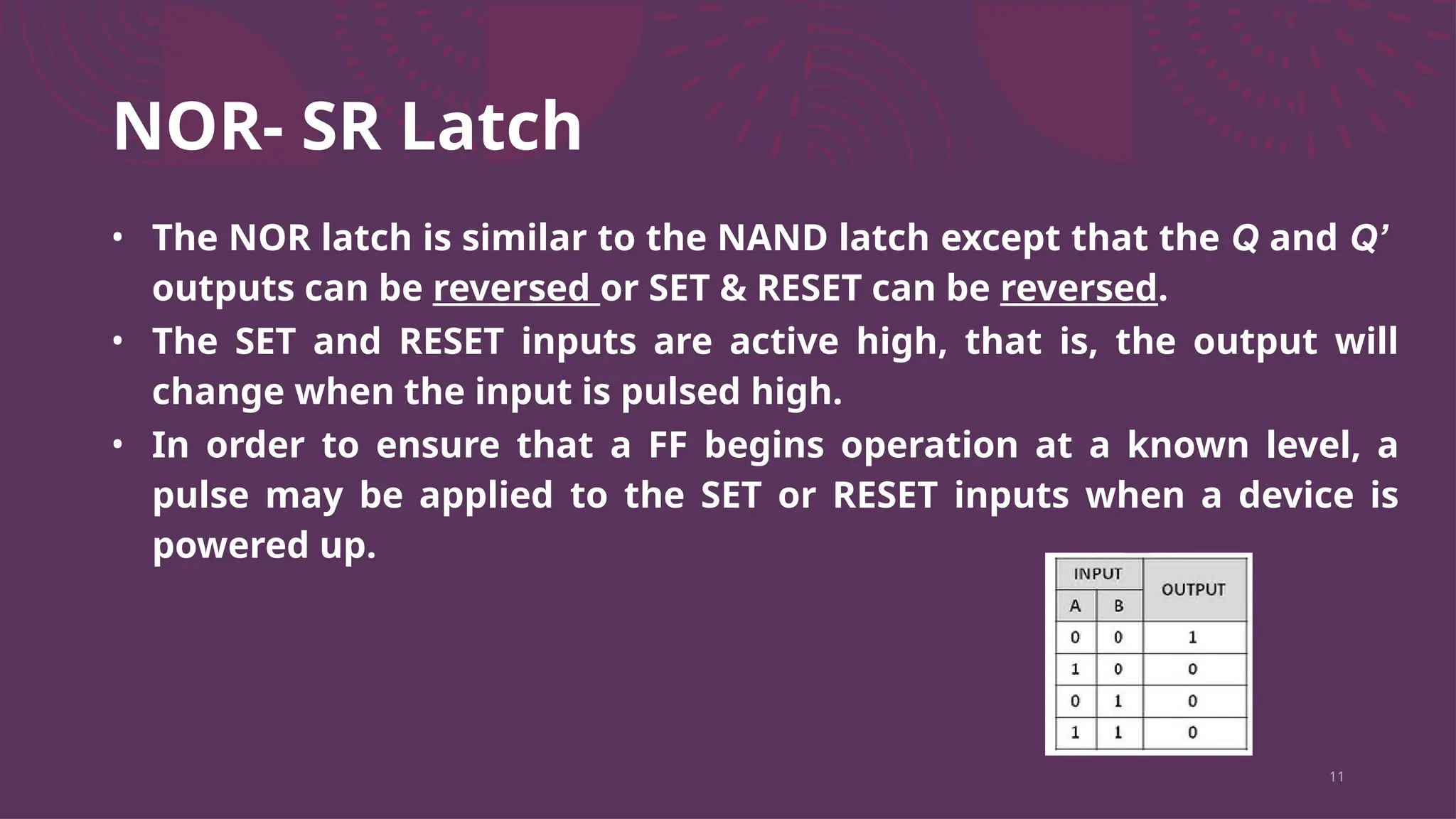

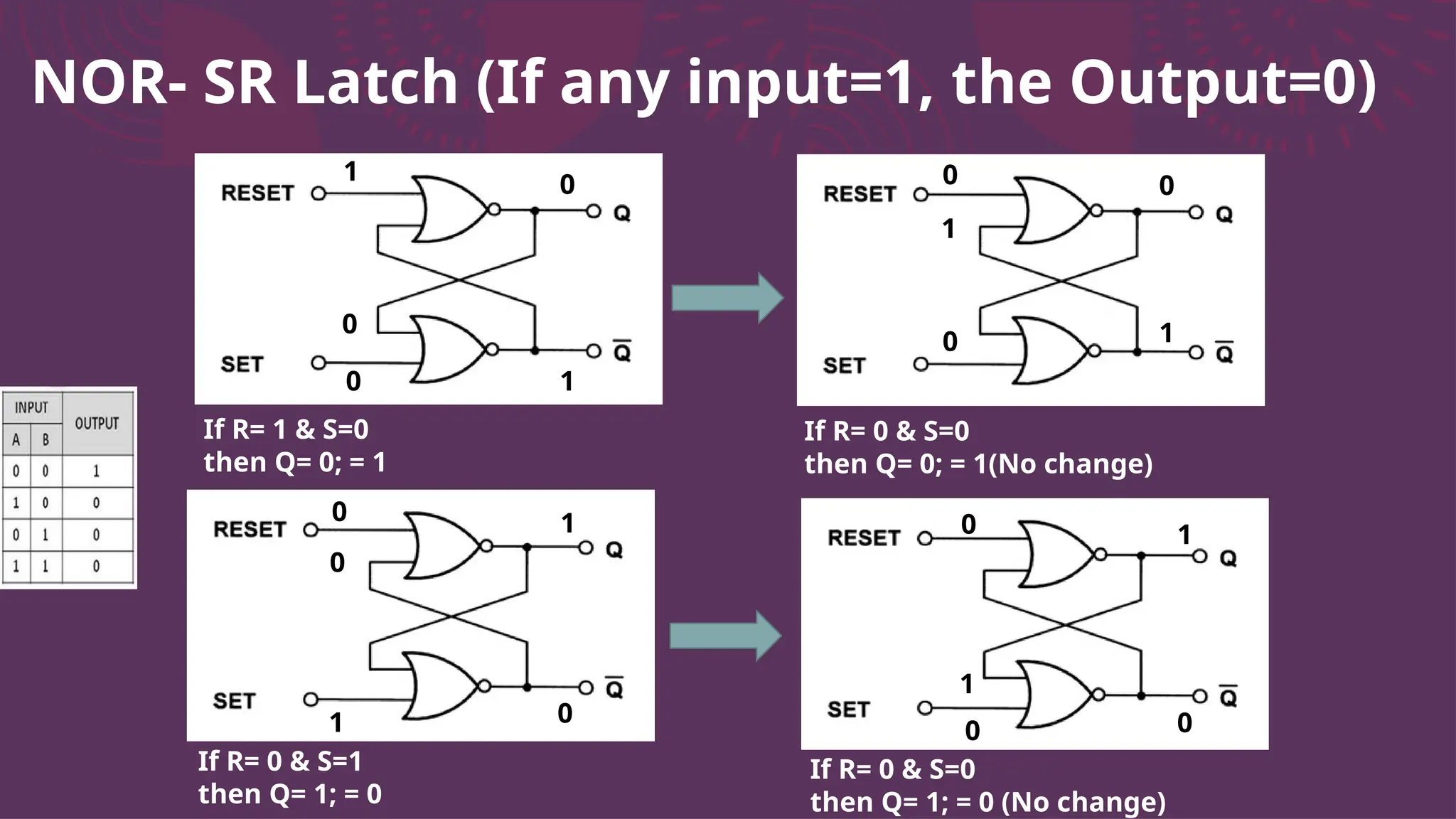

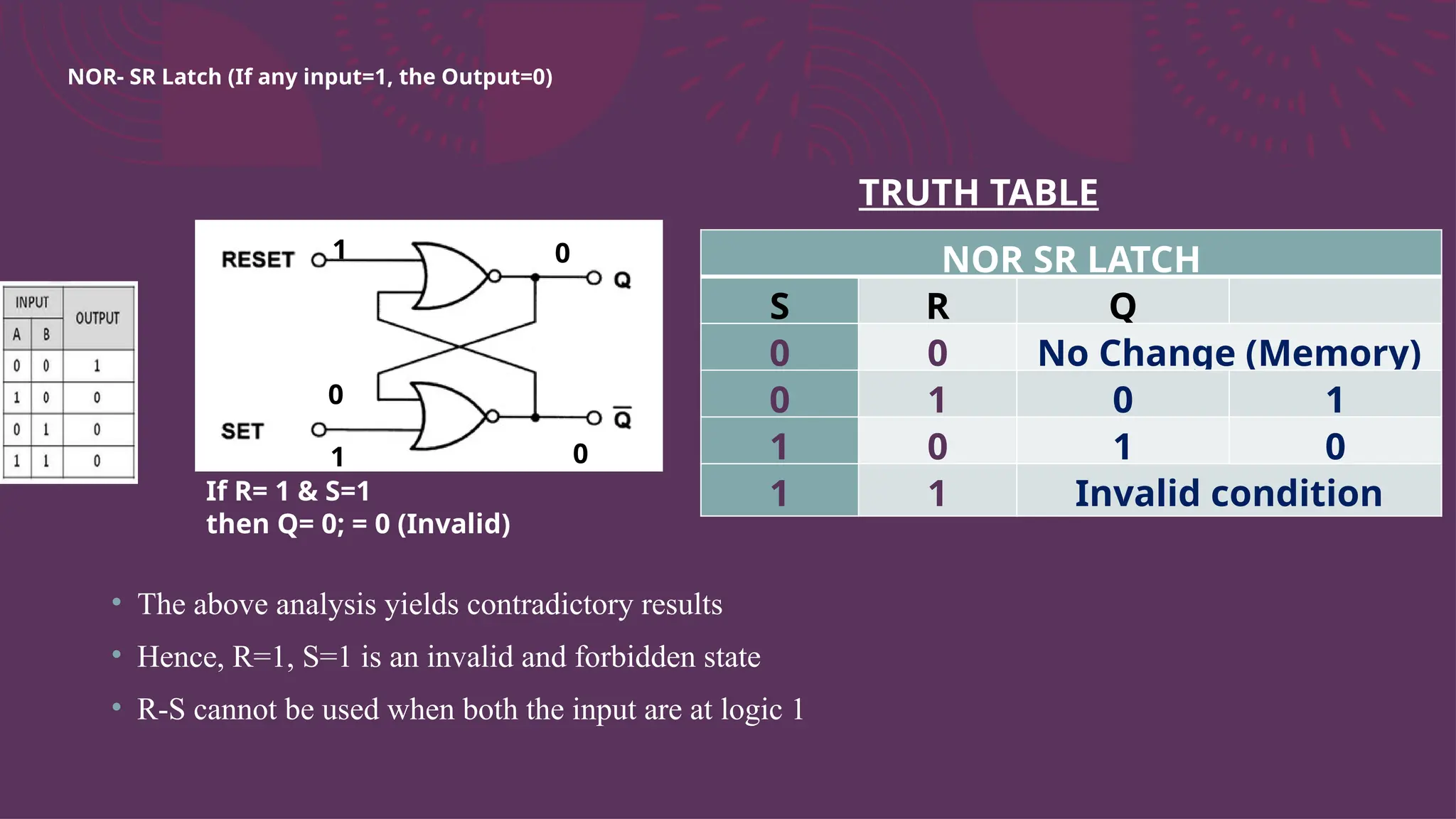

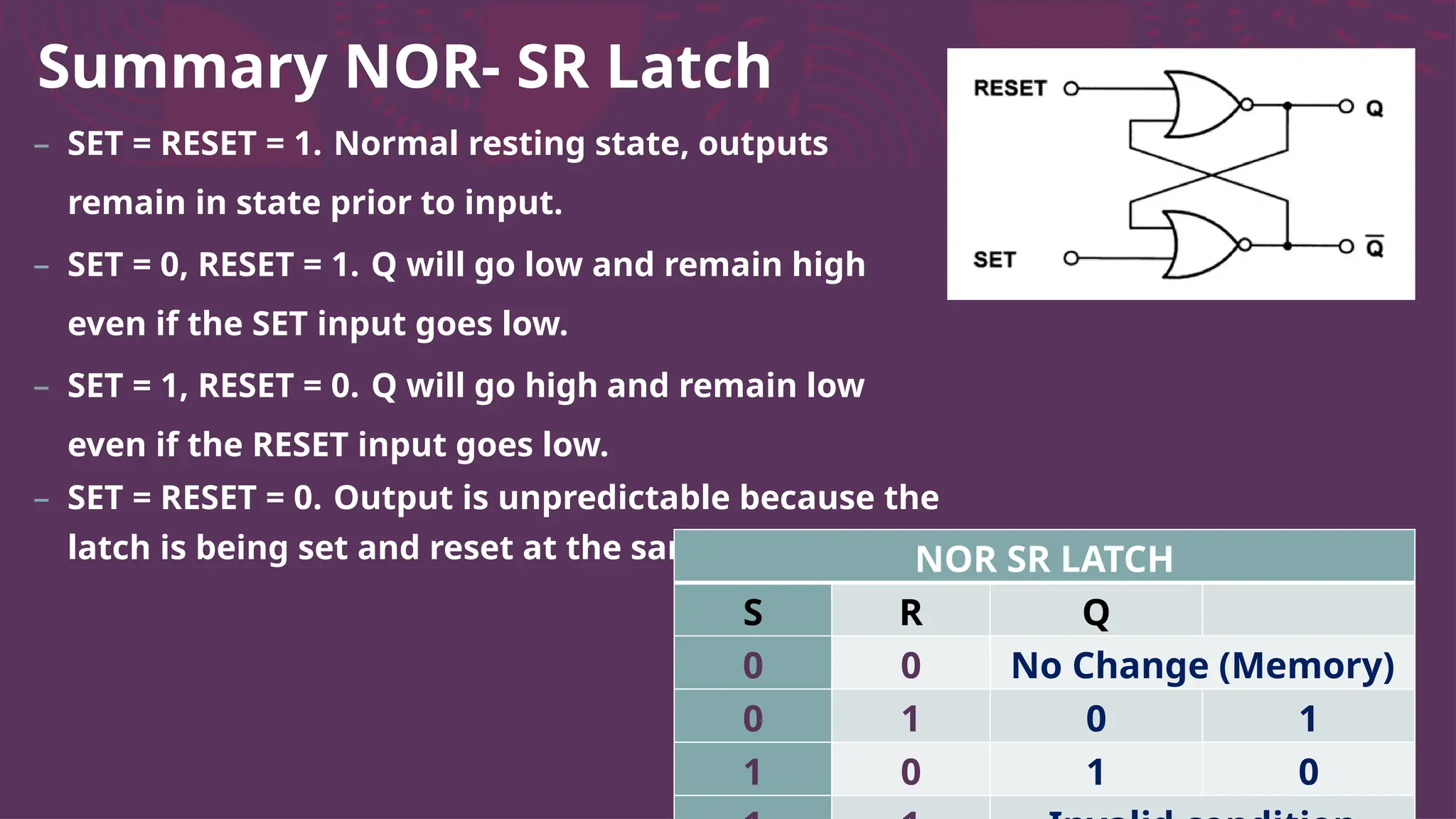

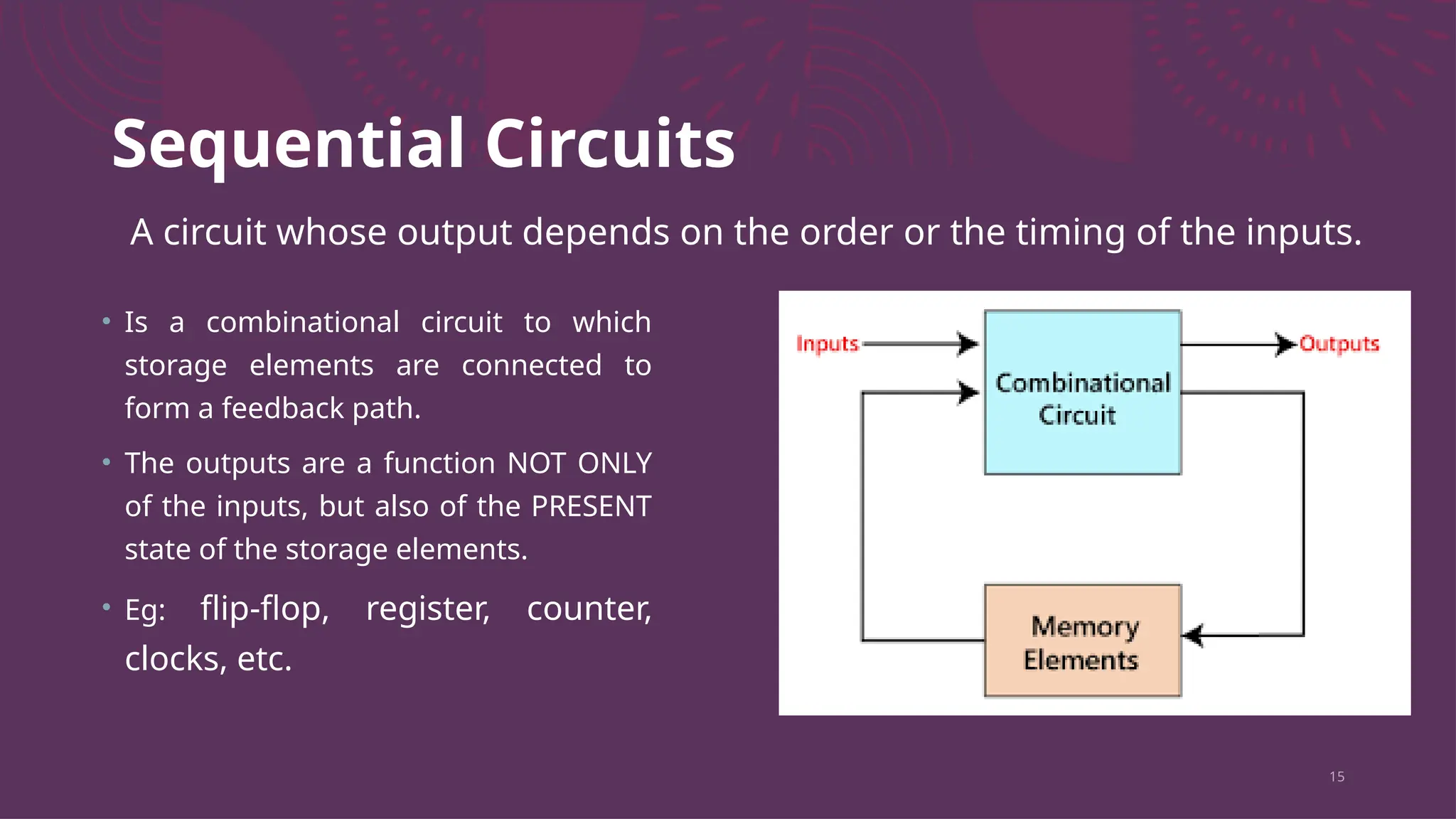

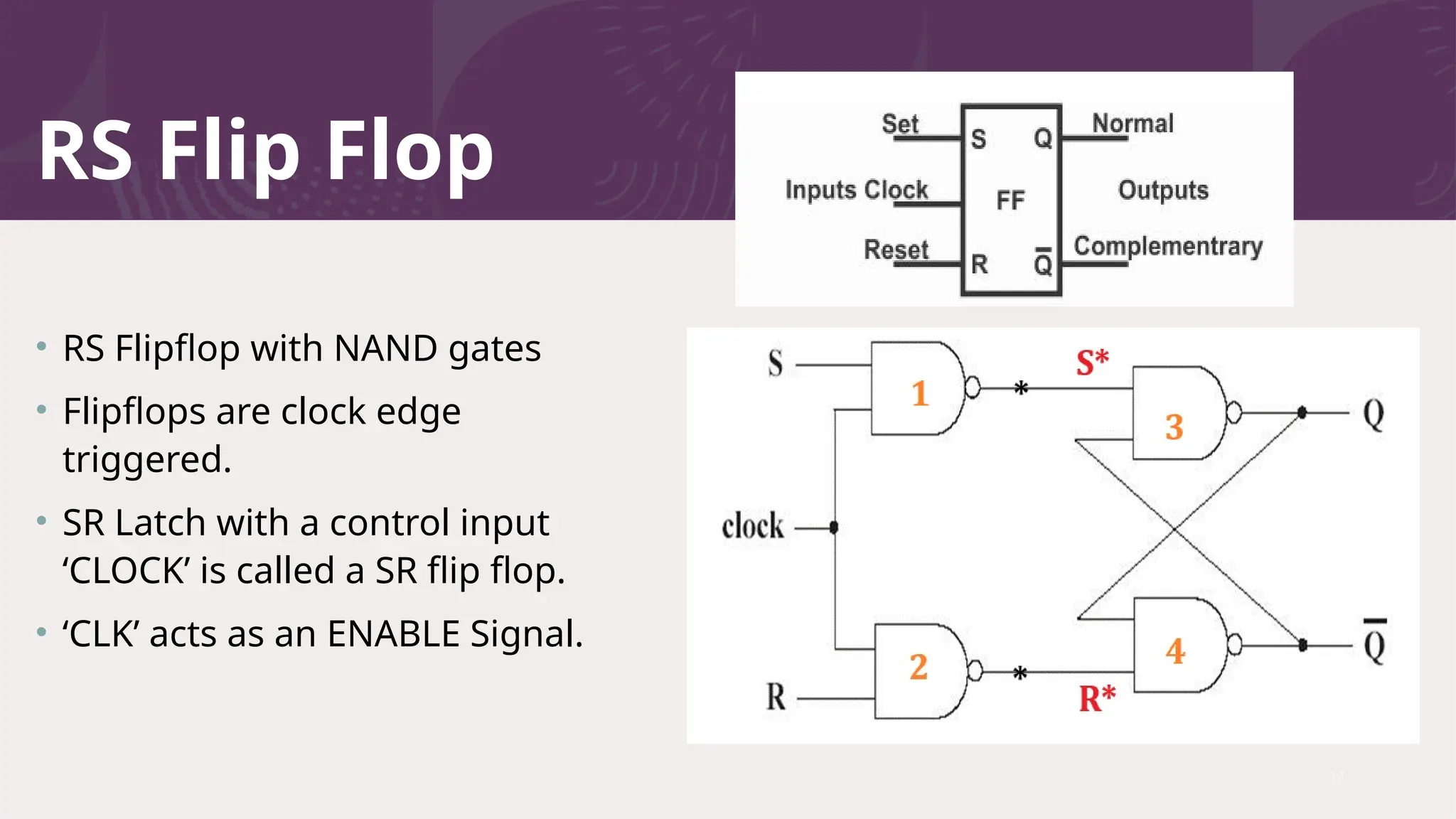

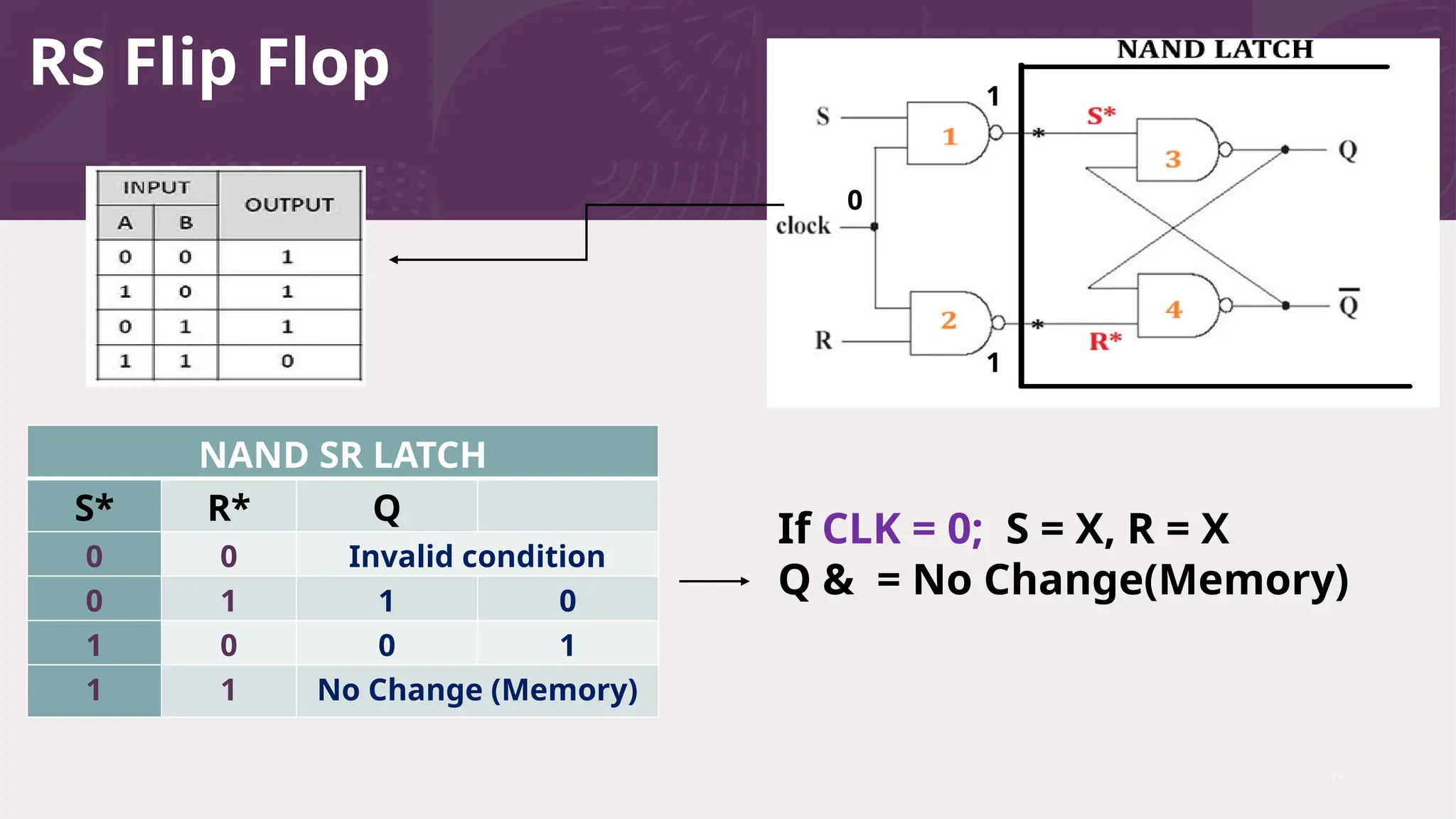

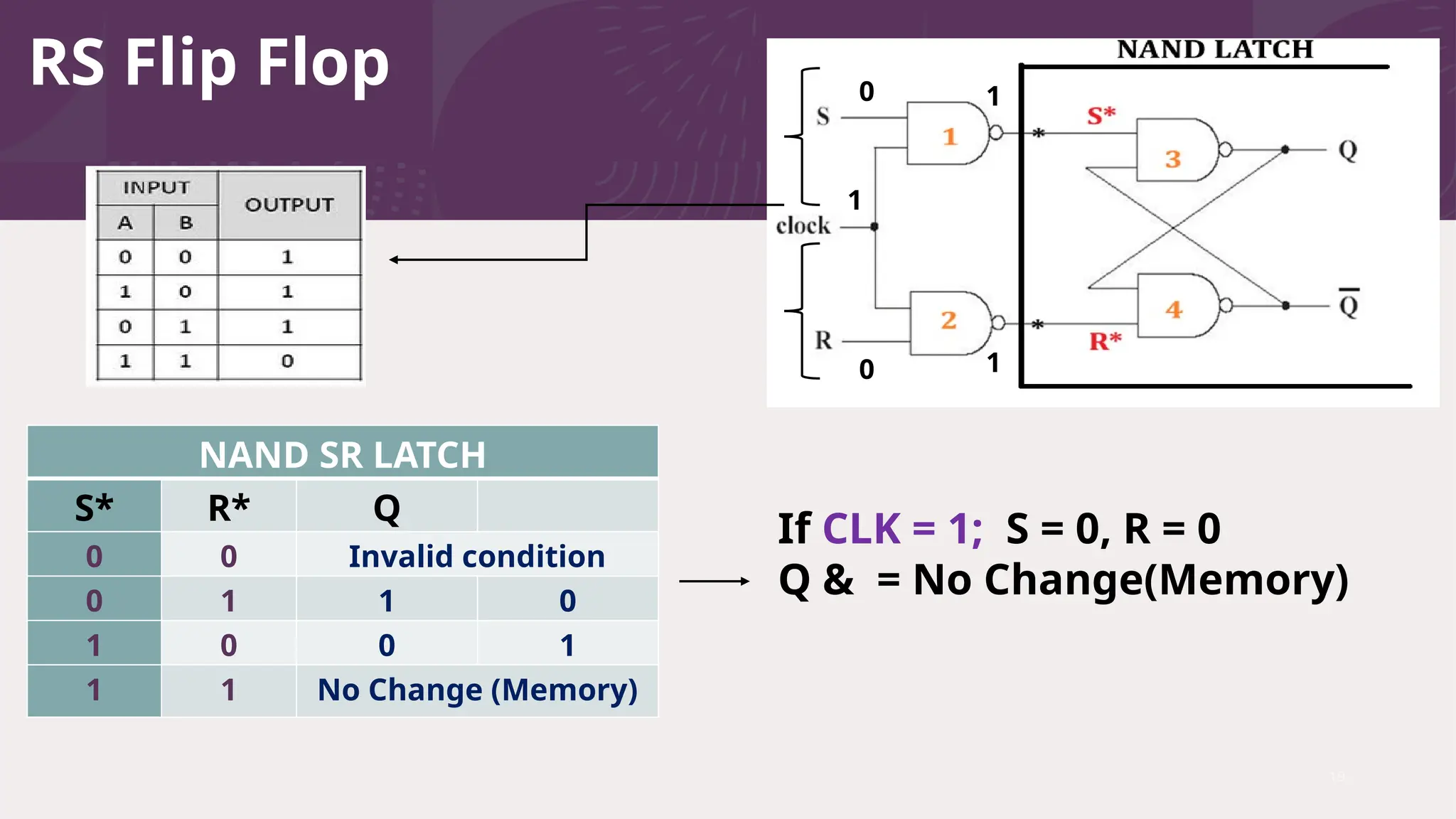

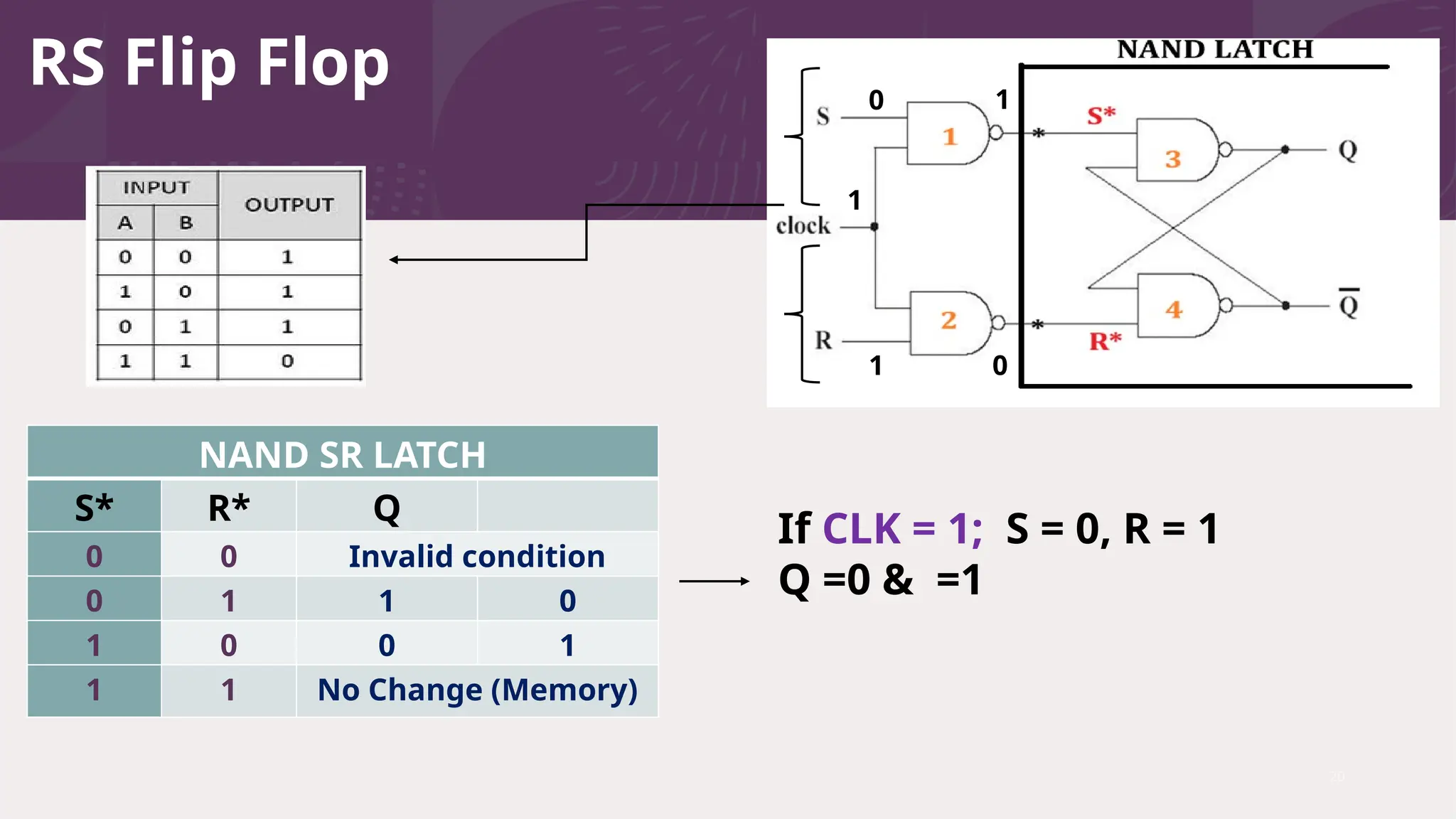

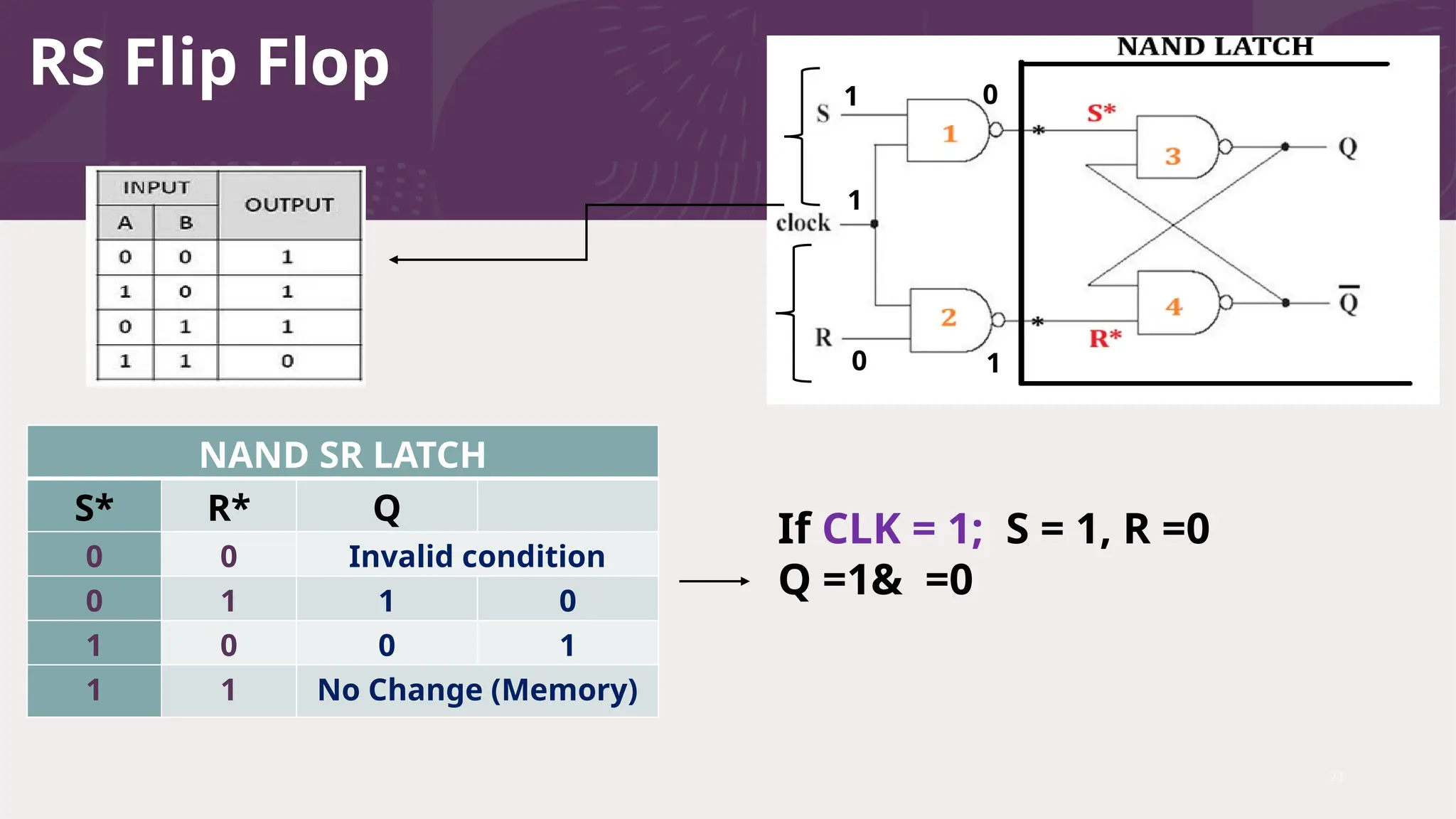

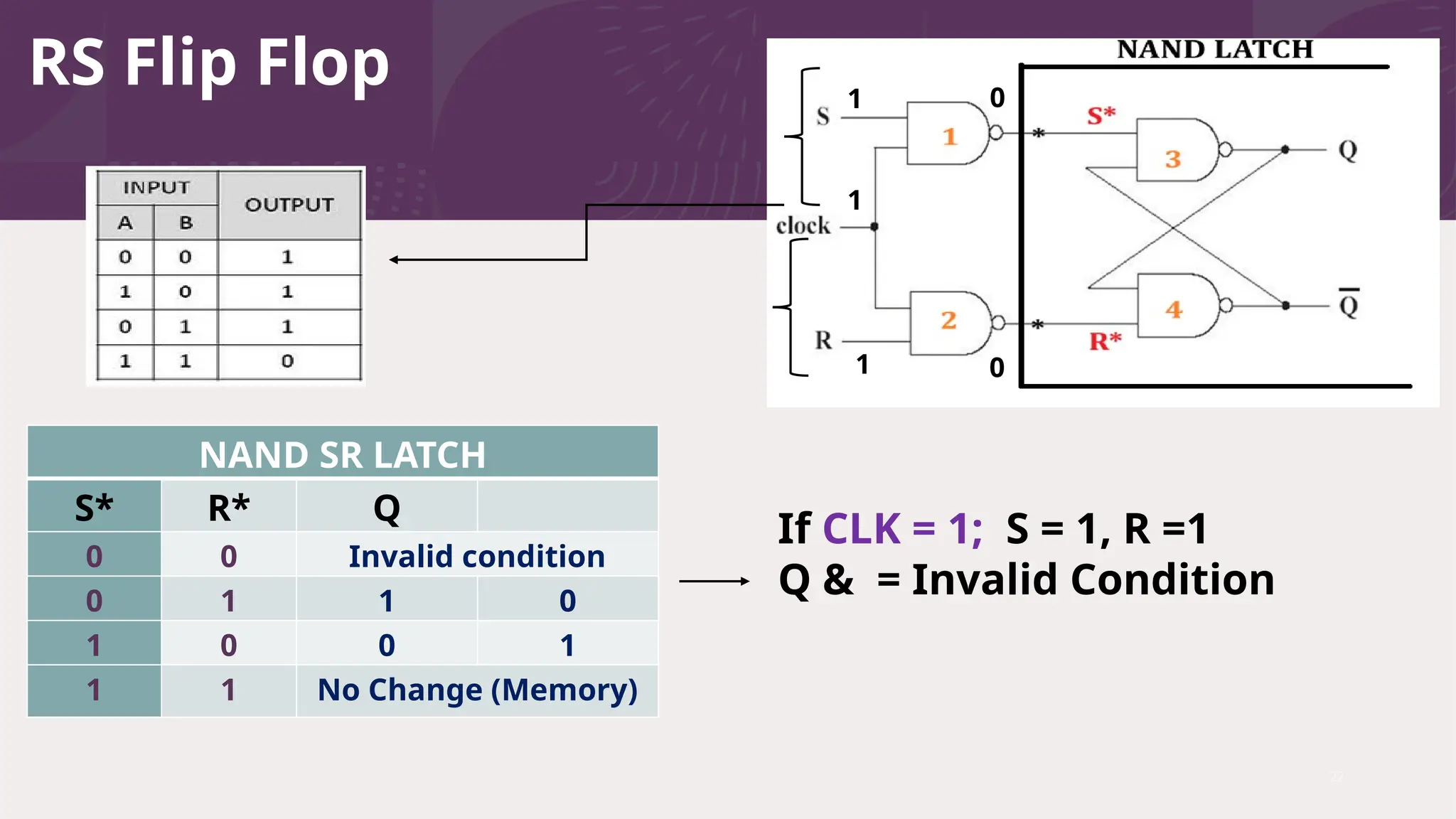

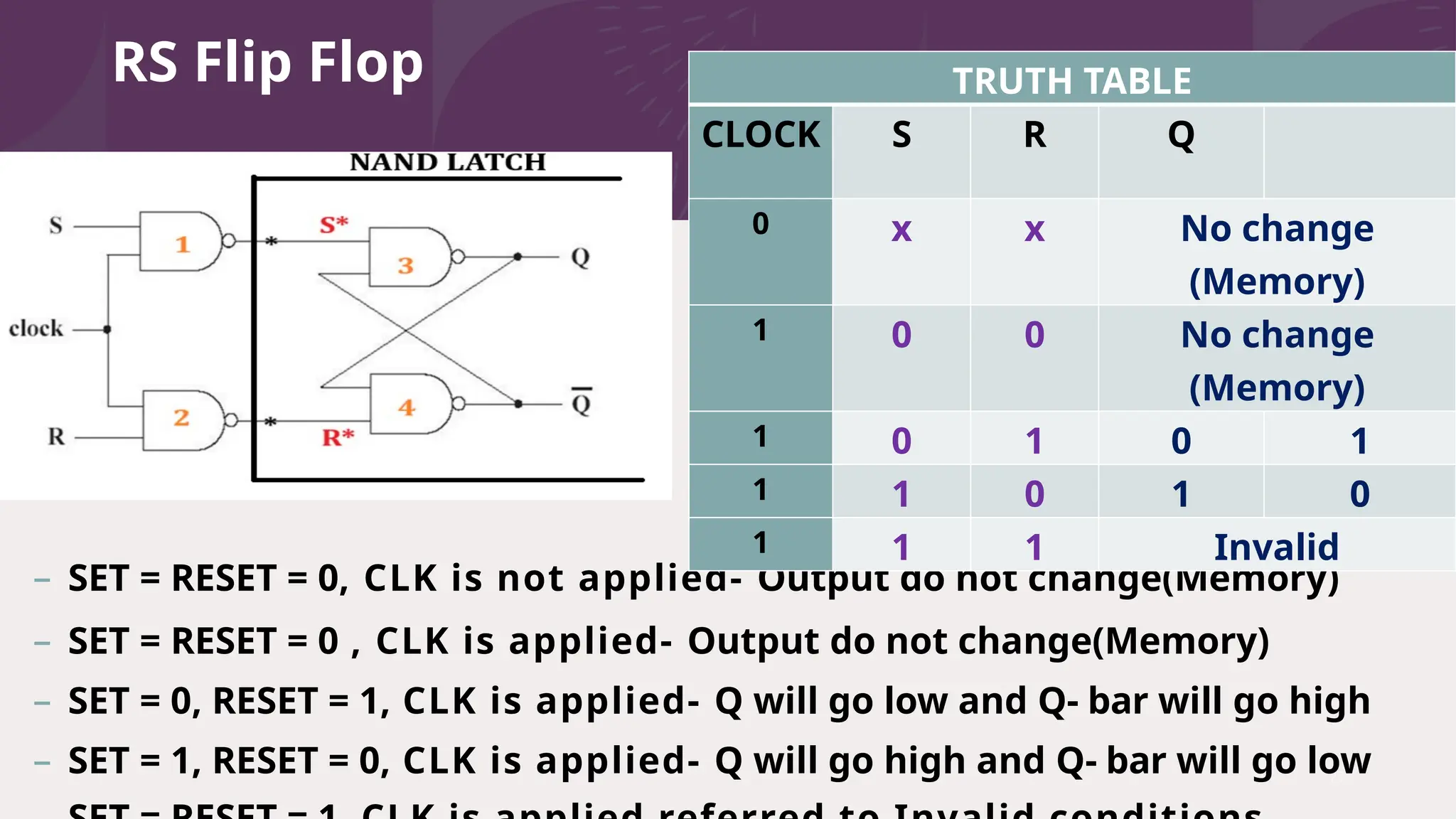

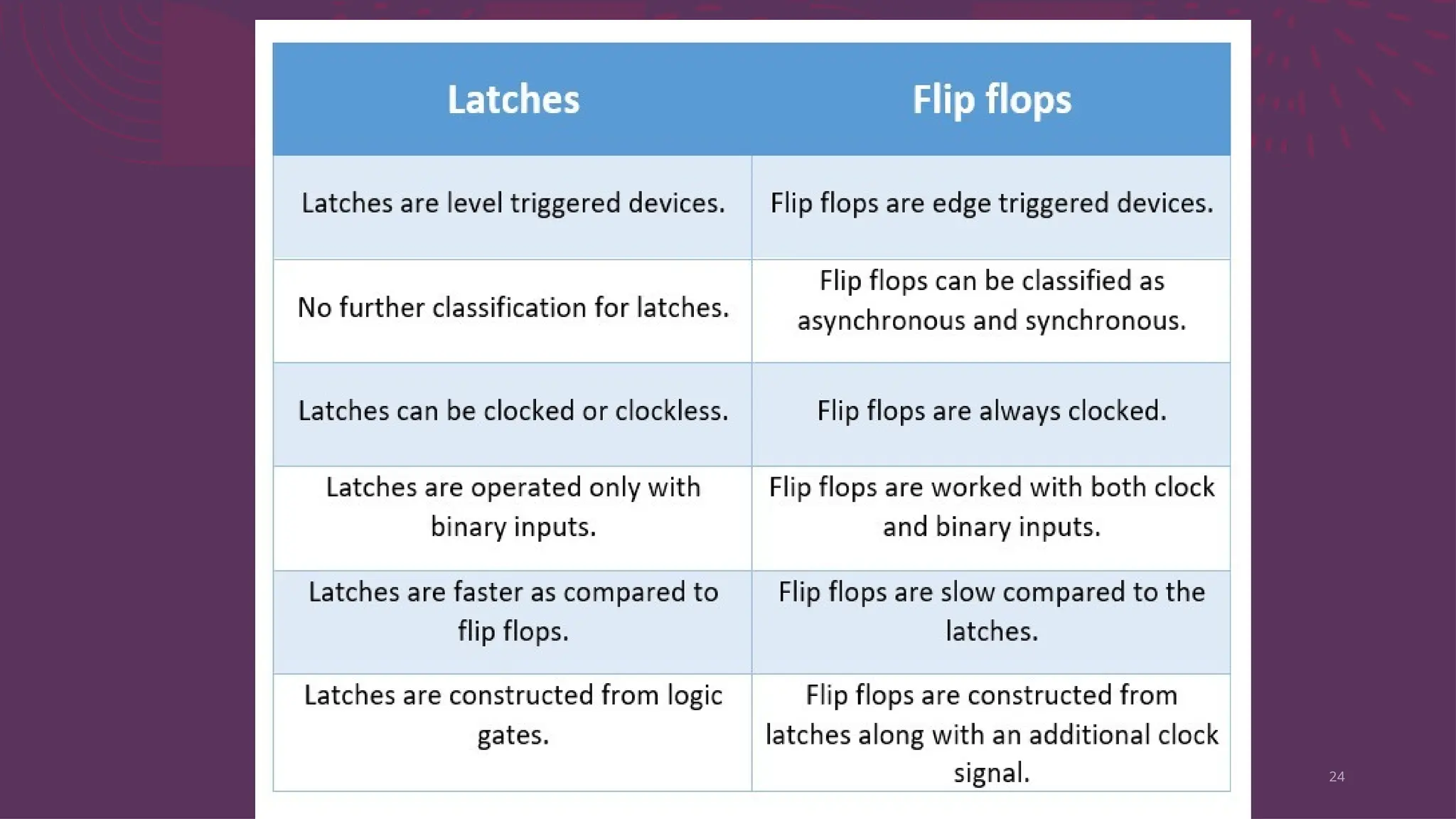

The document explains combinational logic circuits, which produce outputs based solely on current inputs without reference to past states, highlighting components like adders, multiplexers, and decoders. It details two types of adders: half adders and full adders, and introduces latches and flip-flops, emphasizing their memory functions and the impact of clock signals. Various truth tables and conditions for NAND and NOR latches and flip-flops are provided, illustrating their operational behaviors under different input scenarios.