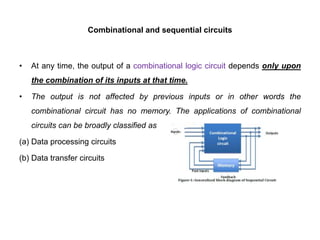

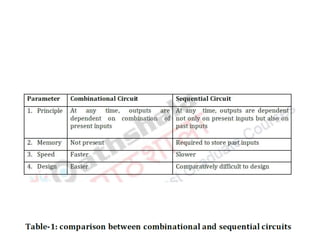

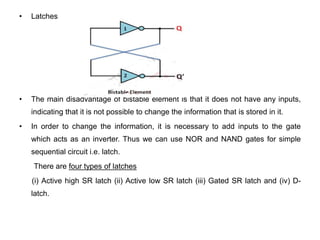

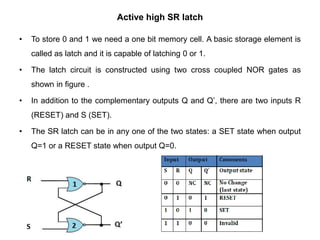

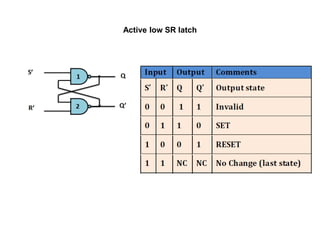

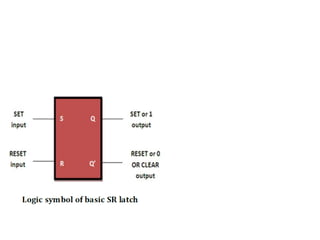

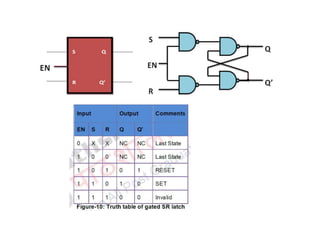

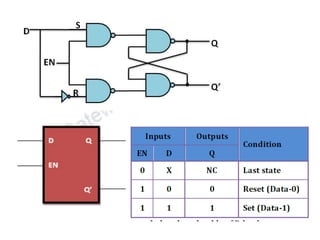

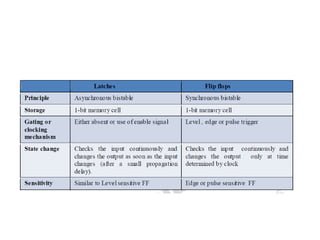

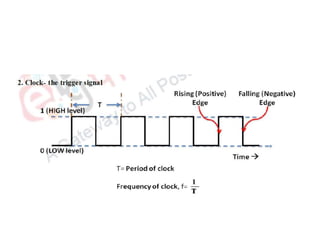

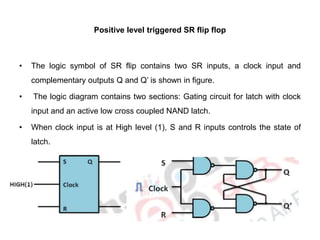

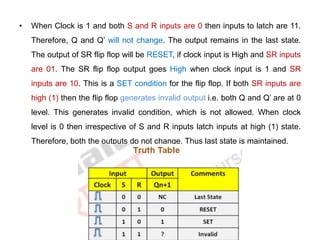

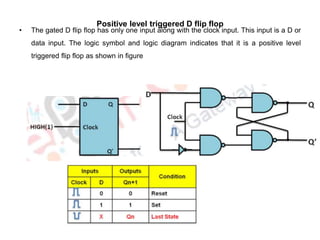

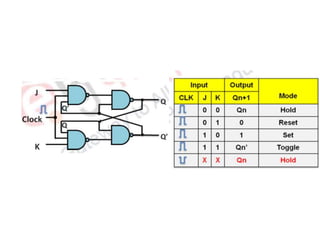

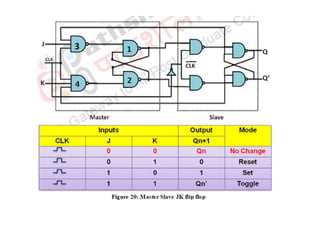

The document discusses synchronous sequential logic circuits. It defines sequential circuits as those whose outputs depend on both the present inputs and past inputs, requiring memory elements like latches and flip-flops. Several types of latches and flip-flops are described, including SR, D, JK, and T latches/flops. Their structures and operations are explained. The key difference between latches and flops is that latches change state asynchronously while flops change state synchronously with a clock signal.