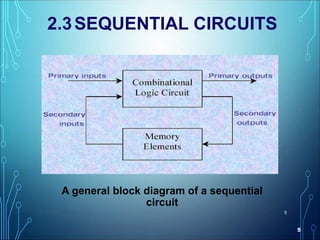

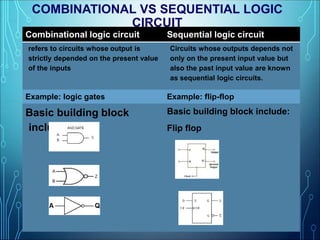

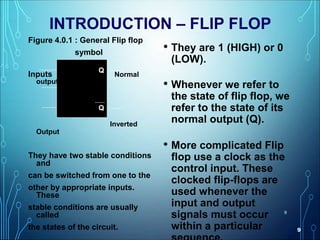

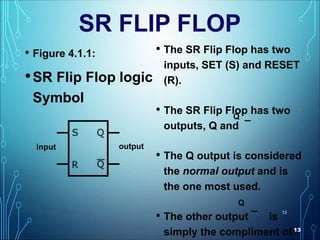

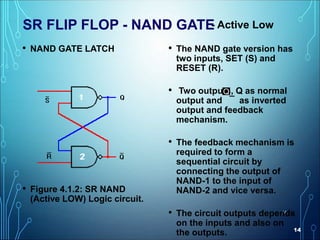

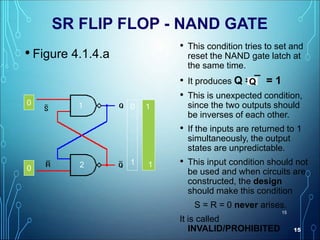

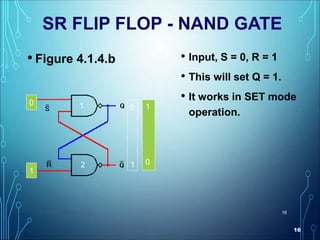

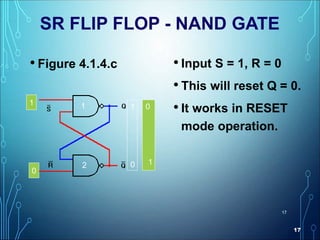

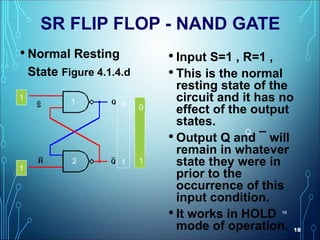

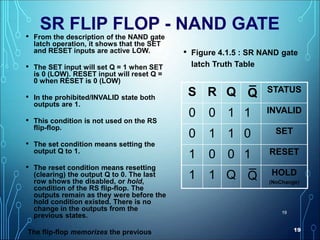

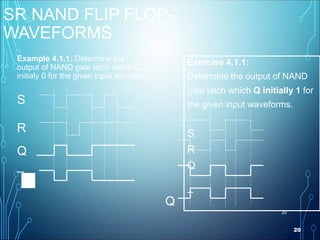

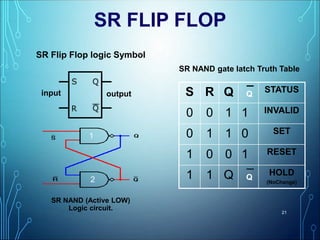

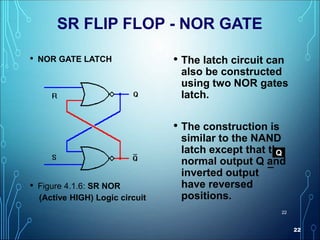

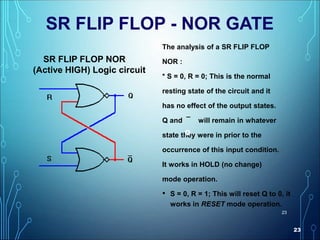

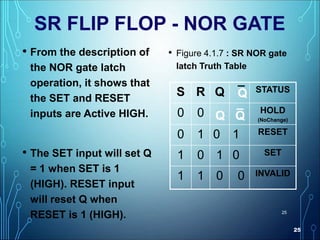

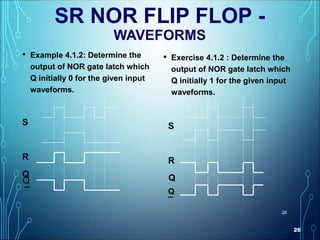

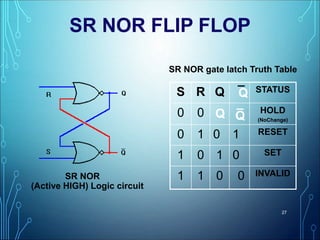

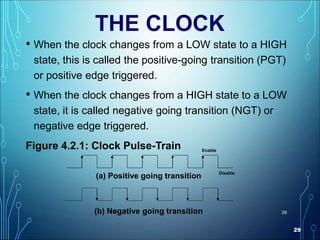

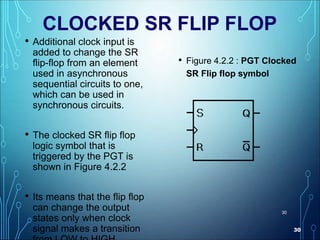

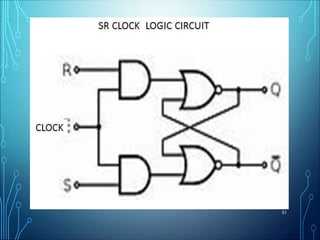

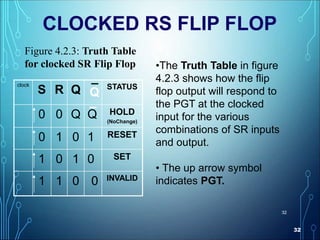

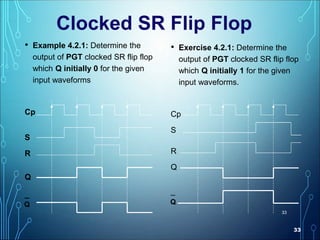

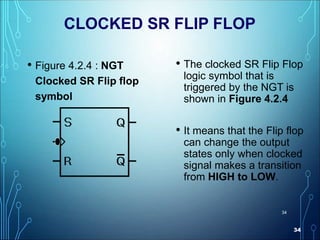

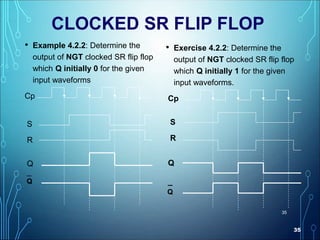

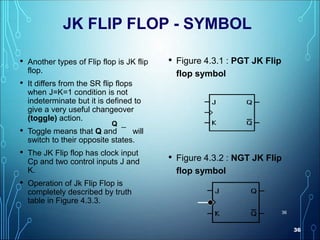

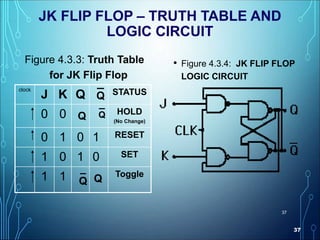

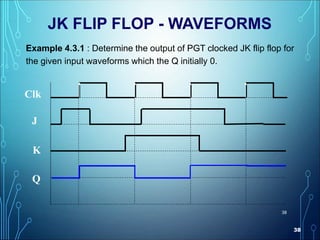

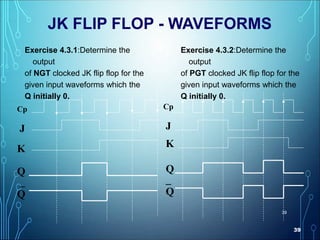

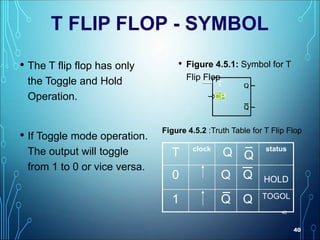

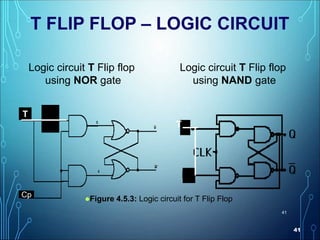

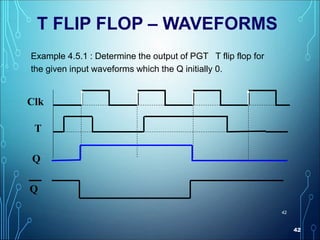

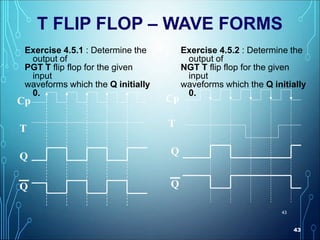

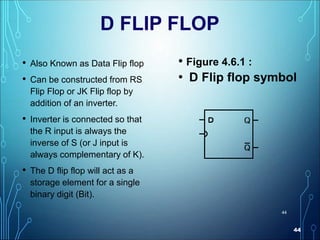

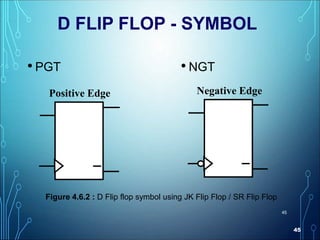

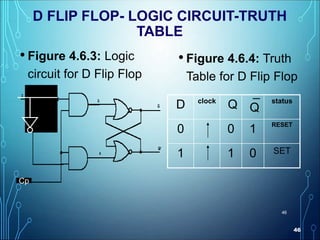

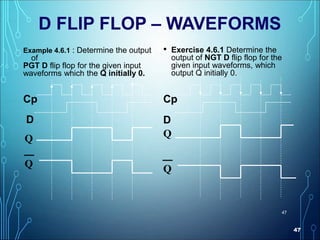

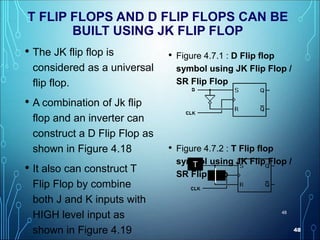

This document discusses sequential logic circuits and various types of flip flops. It defines sequential logic circuits as circuits whose outputs depend not only on present inputs but also past inputs. Several types of flip flops are described including SR, Clocked SR, JK, T, and D flip flops. The document provides details on the logic symbol, truth table, and logic circuit for SR and JK flip flops. It also discusses clock signals and provides examples of determining the output for various flip flop types given input waveforms.