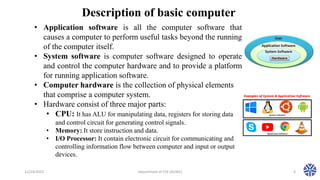

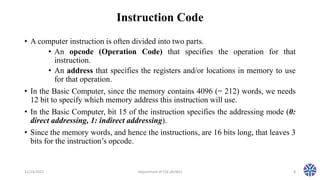

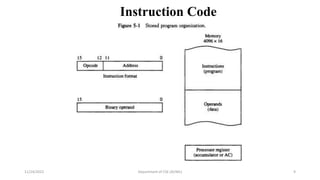

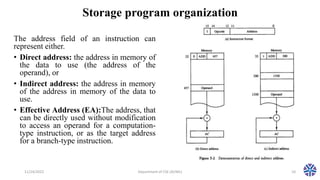

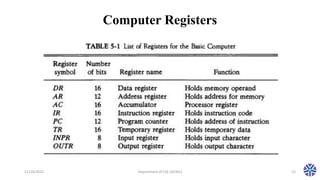

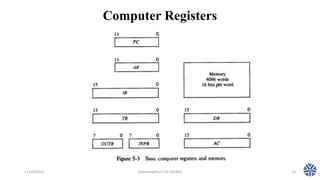

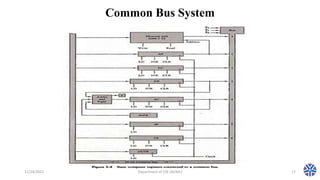

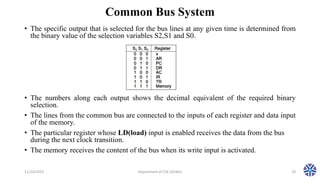

This document discusses a computer organization and architecture course. It covers topics like instruction codes, computer registers, instruction cycle, and input/output. The session covered basic computer organization design, instruction codes, registers, timing and control, instruction cycle, memory reference instructions, and input/output interrupts. It also describes the basic components of a computer like CPU, memory, I/O and how instructions, registers, addressing modes, and the common bus system work.