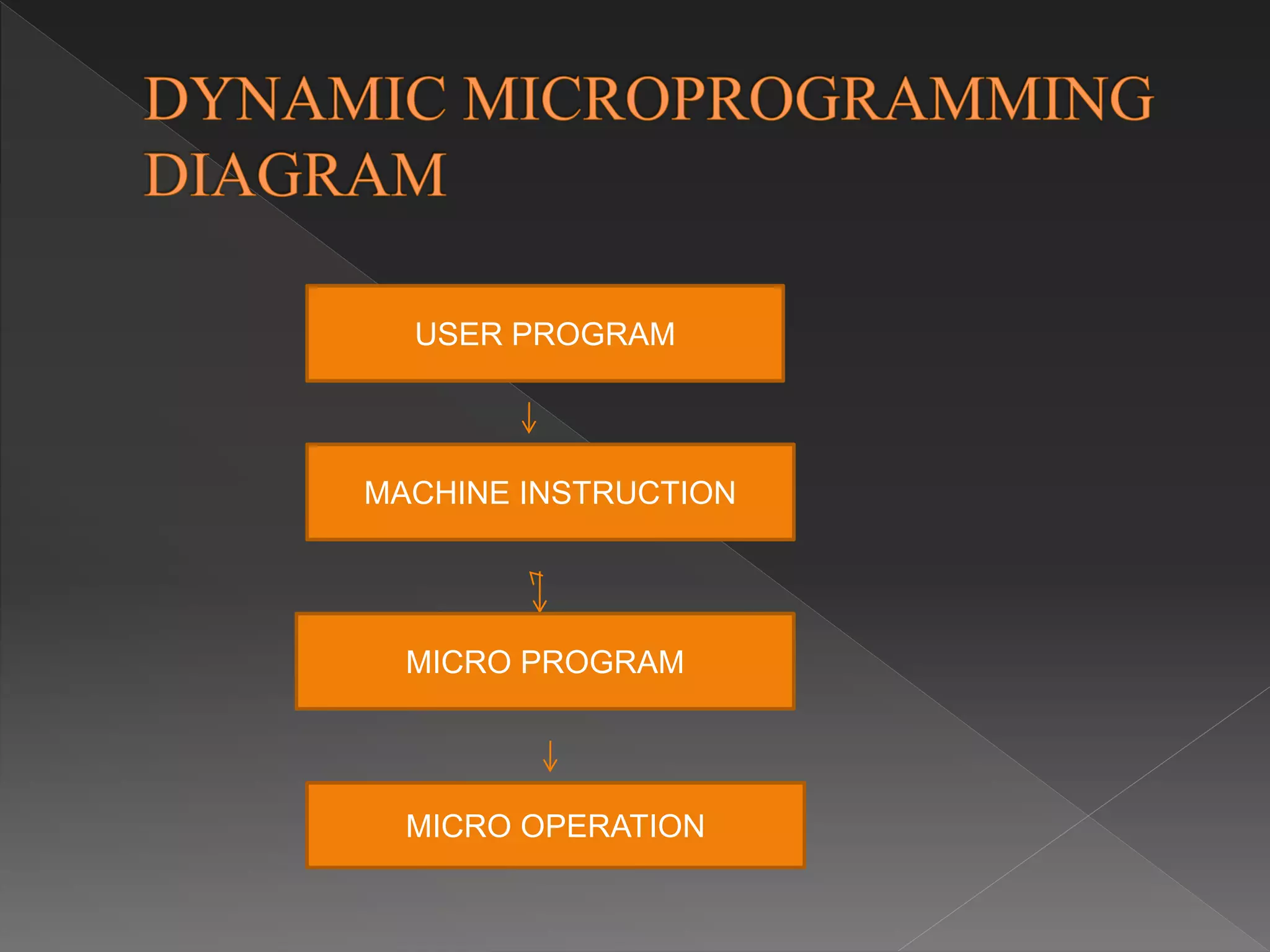

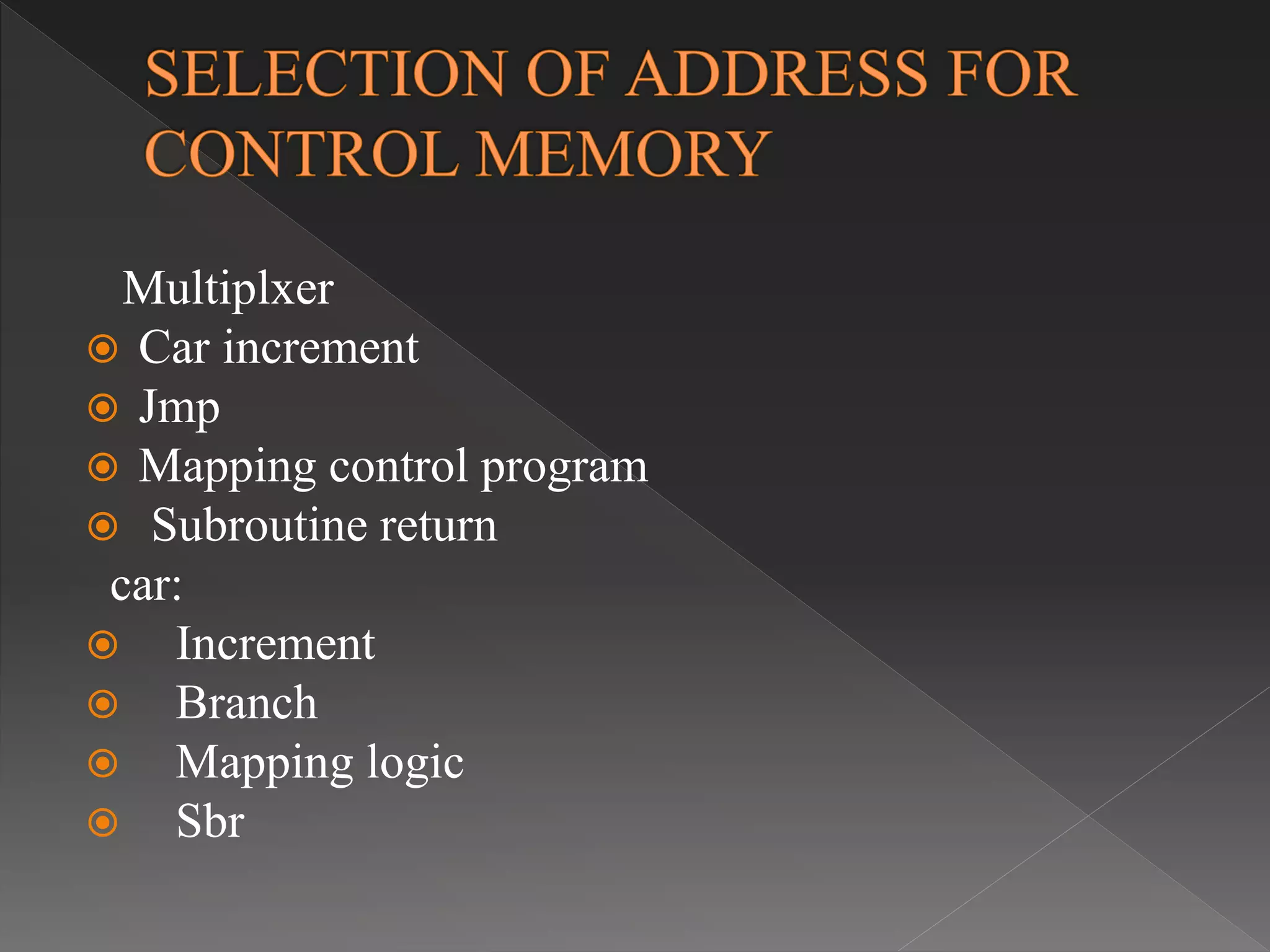

The document discusses address sequencing in a microprogram control unit. It begins by defining key terms like control address register, which stores the initial address of the first microinstruction. It then explains that the next address generator is responsible for selecting the next address from control memory based on the current microinstruction. Microinstructions are stored in control memory in groups that make up routines corresponding to each machine instruction. The document also discusses control memory, hardwired control vs microprogrammed control, and examples of next address generation and status bits.