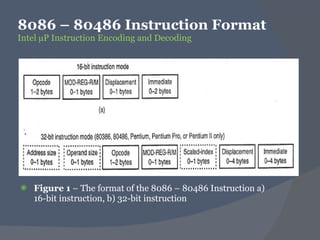

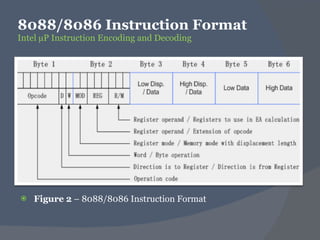

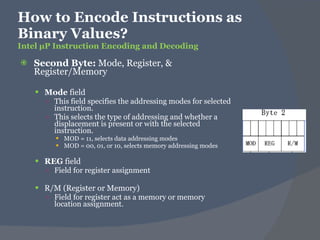

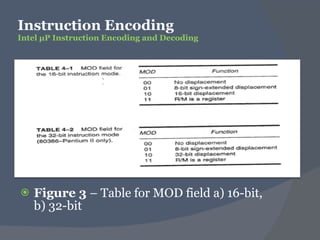

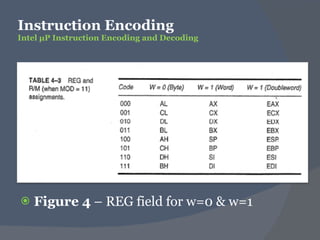

The document discusses microprocessor instruction encoding and decoding. It explains that instructions are encoded as binary machine code that the microprocessor understands and are decoded during execution. The encoding process represents an entire assembly language instruction as a binary value using opcodes, operands, and addressing information. Decoding is the reverse process of converting the binary code back into an assembly language format. It also provides details on instruction formats, encoding fields, and examples of encoding and decoding specific instructions.

![Register Addressing It uses the R/M field to specify a register instead of memory location Special addressing modes This addressing modes occurs whenever memory data are referenced by only the displacement mode of addressing for 16-bit instructions. MOV [1000h], DL MOV NUMB, DL MOD = 00 and R/M =110 Scaled-Index Byte Indicates the additional forms of scaled-index addressing. Occurs when R/M = 100 Instruction Encoding Intel µP Instruction Encoding and Decoding](https://image.slidesharecdn.com/ceng04midtermlecture23-intelpinstructionencodinganddecoding-100731025542-phpapp02/85/Intel-p-instruction-encoding-and-decoding-14-320.jpg)

![Determine the equivalent machine code of the following assembly code: MOV DX, AX MOV DX, [BX + DI + 1234h] ADD AX, 1023 SUB DX, 1234h AND [BX + 12h], AX MOV EAX, [EBX + 4*ECX] MOV [5267h], DH MOV CS, AX MOV DS, AX MOV AX, [BX] Examples (Encoding) Intel µP Instruction Encoding and Decoding](https://image.slidesharecdn.com/ceng04midtermlecture23-intelpinstructionencodinganddecoding-100731025542-phpapp02/85/Intel-p-instruction-encoding-and-decoding-15-320.jpg)