Embed presentation

Downloaded 99 times

The presentation by Md. Ashikur Rahman Khan covers set-associative mapping cache, which is a combination of direct and associative mapping for data storage in CPU caches. It explains the process of cache indexing, searching for desired addresses, and the calculations involved in defining cache size, number of lines, and sets. Examples illustrate the use of set-associative mapping with various address sizes and configurations.

Introduction of the presenter, Md. Ashikur Rahman Khan with identification number 152-35-1185.

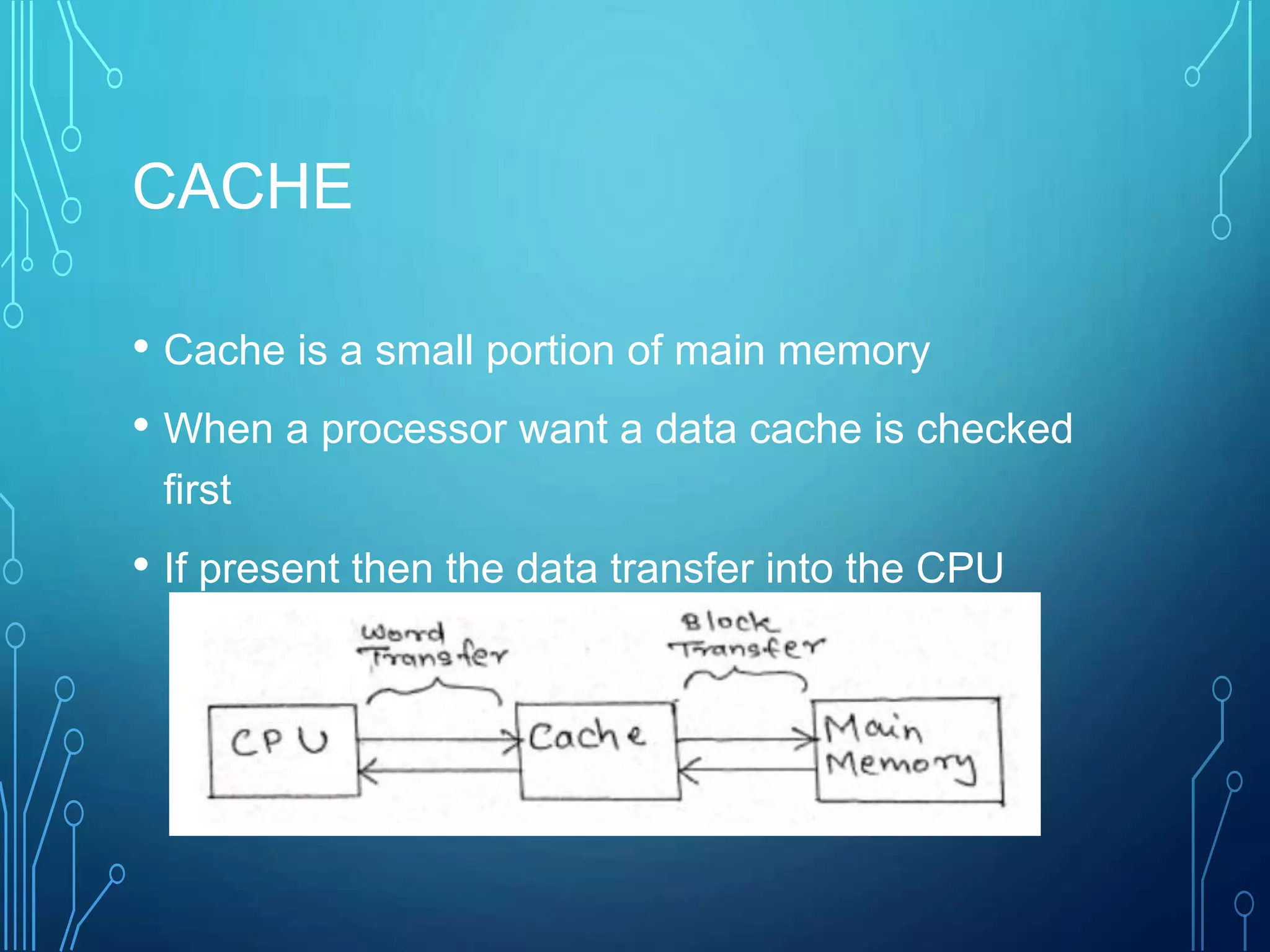

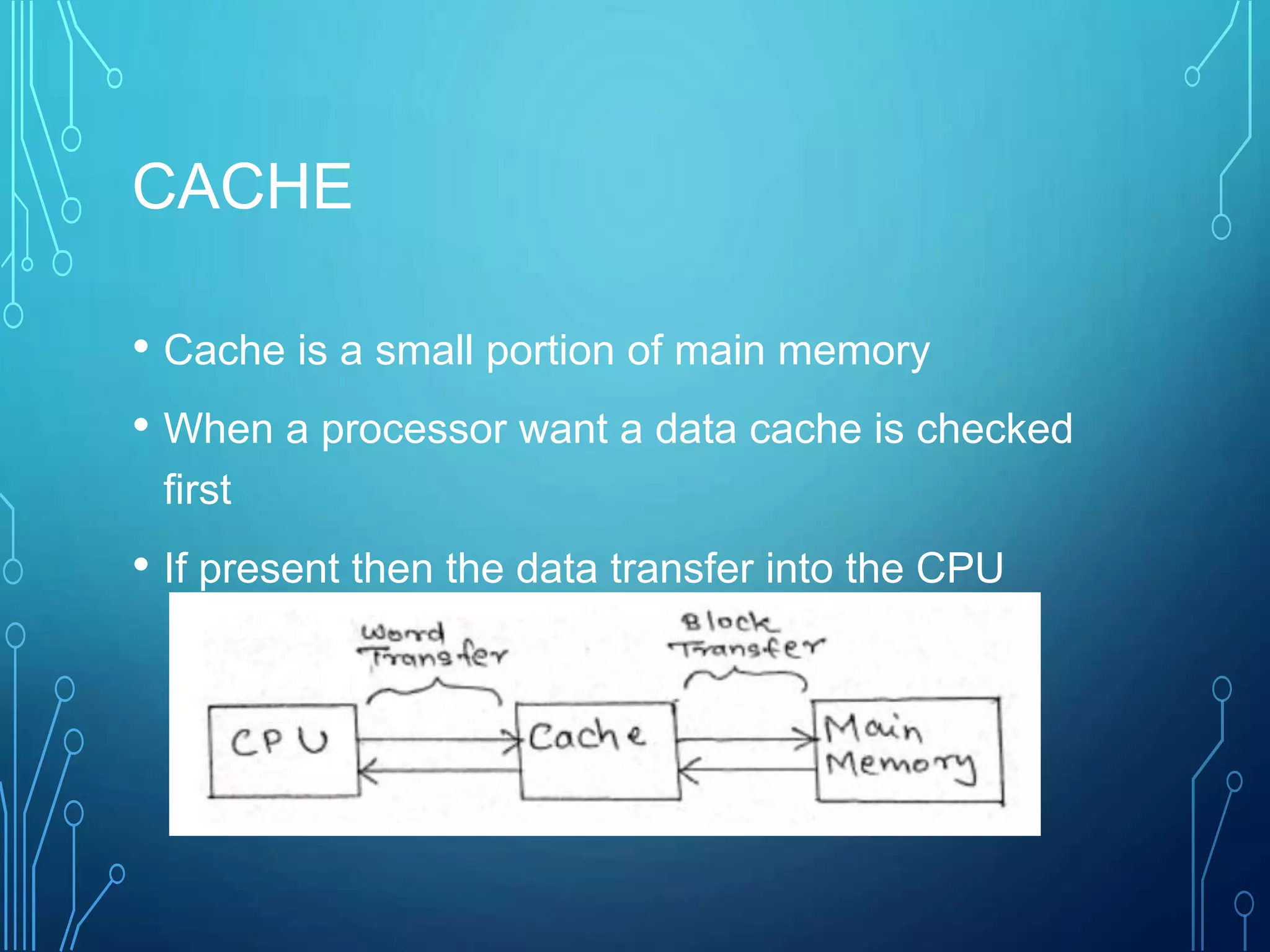

Discussion on cache, a small portion of main memory, and its initial check by the processor for data.

Introduction to three types of cache mapping: Direct, Associative, and Set-associative.

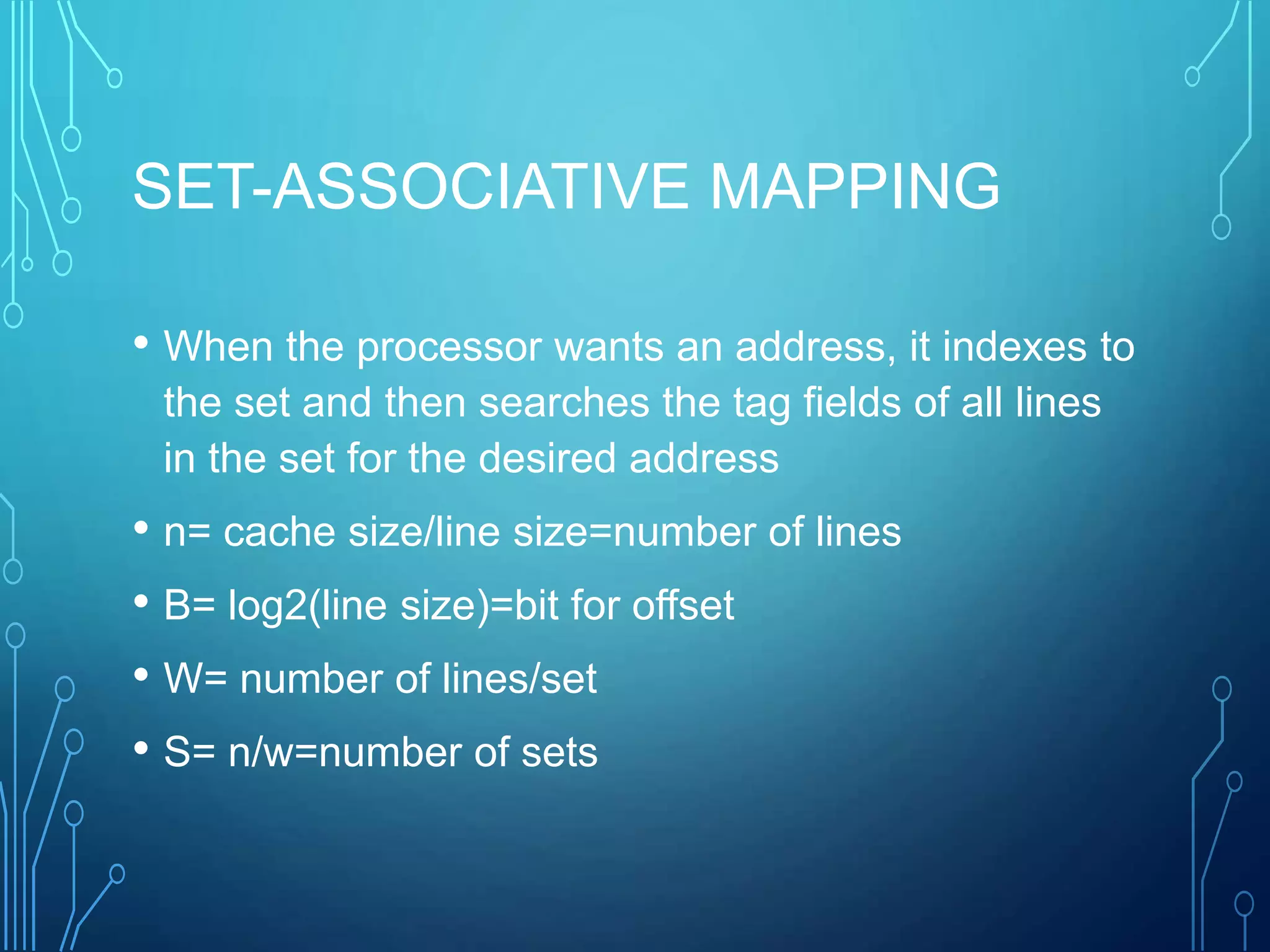

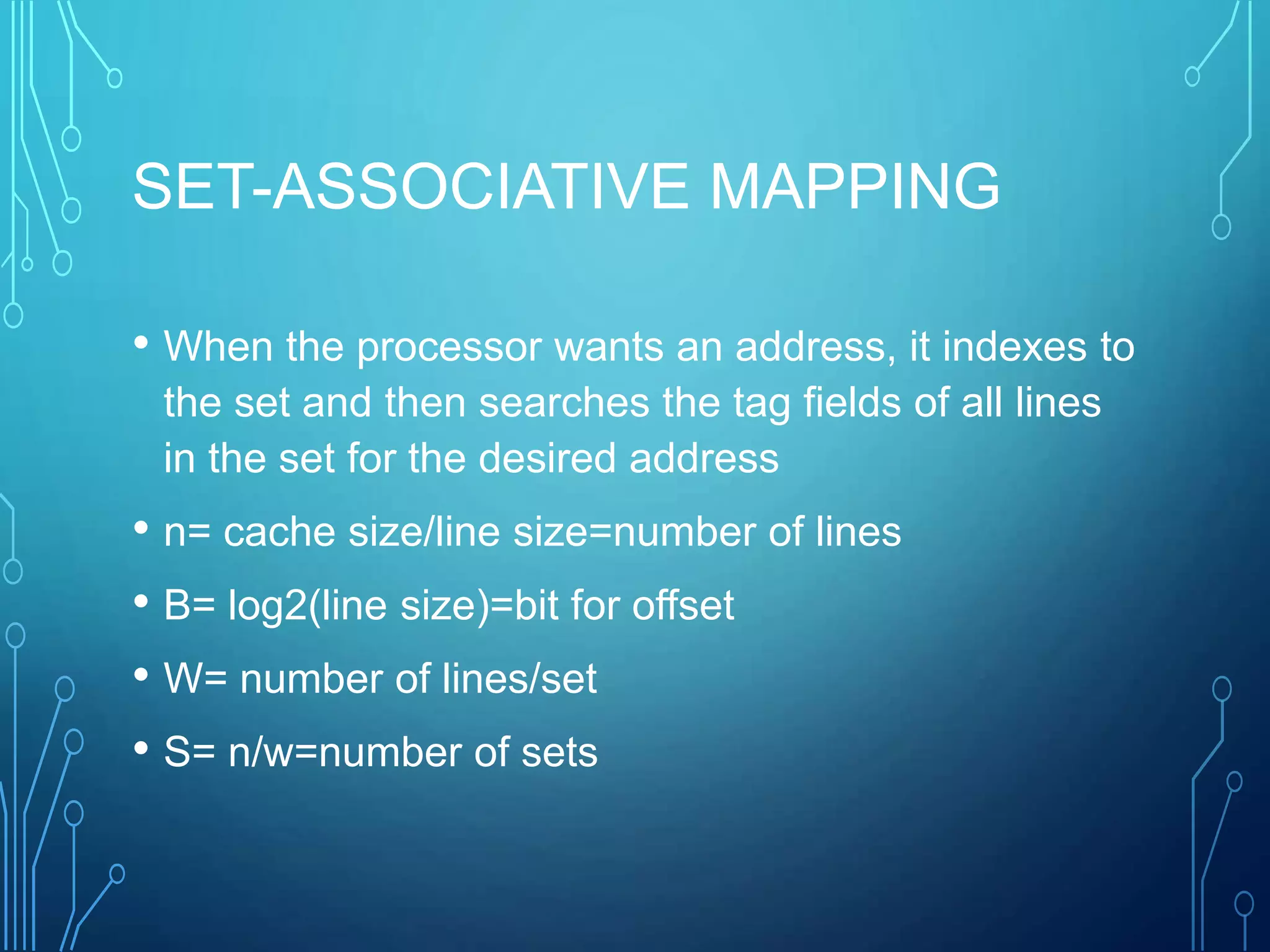

Set-associative mapping is a hybrid of direct and associative methods, detailing the organization of cache lines into sets.

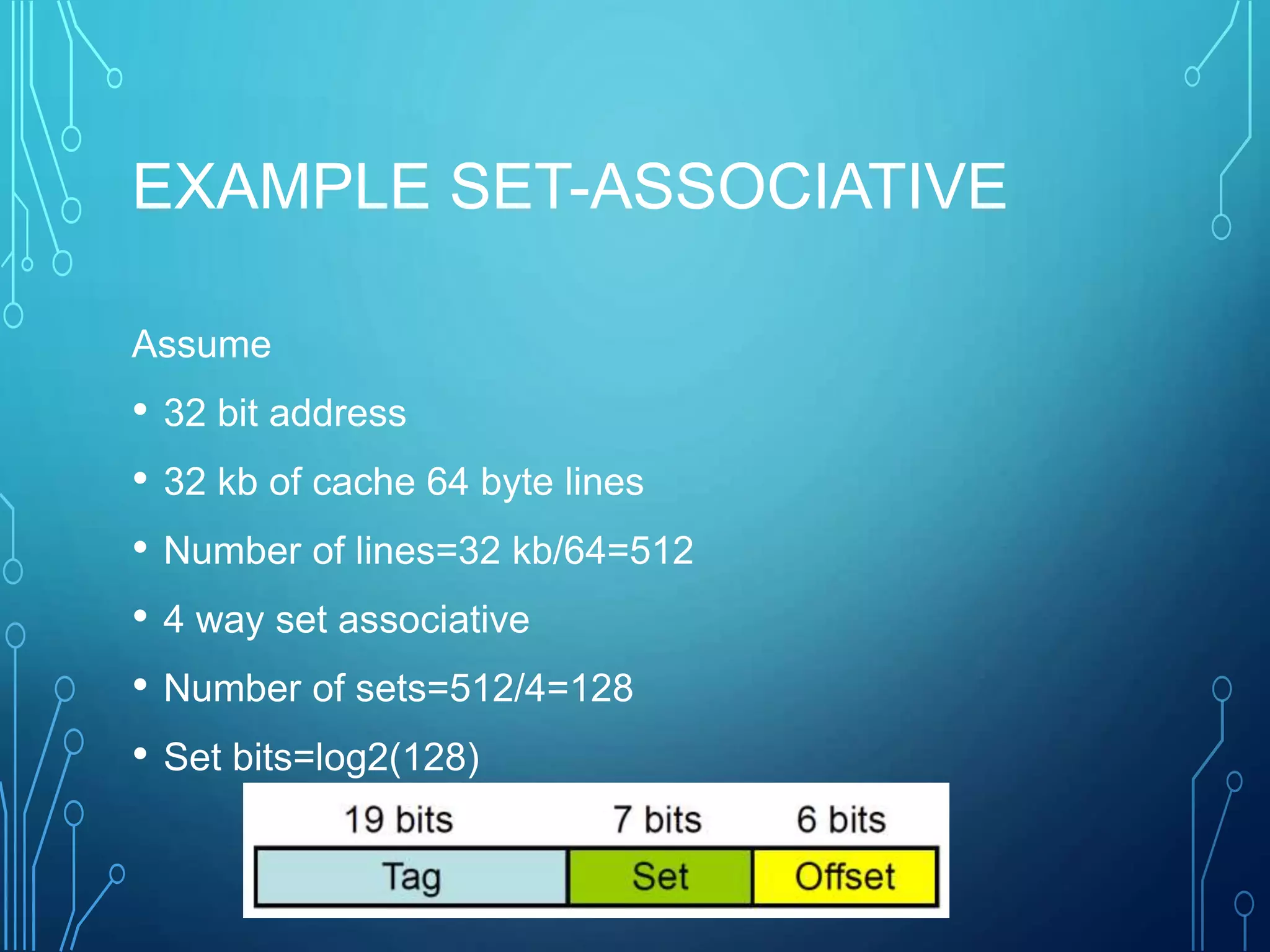

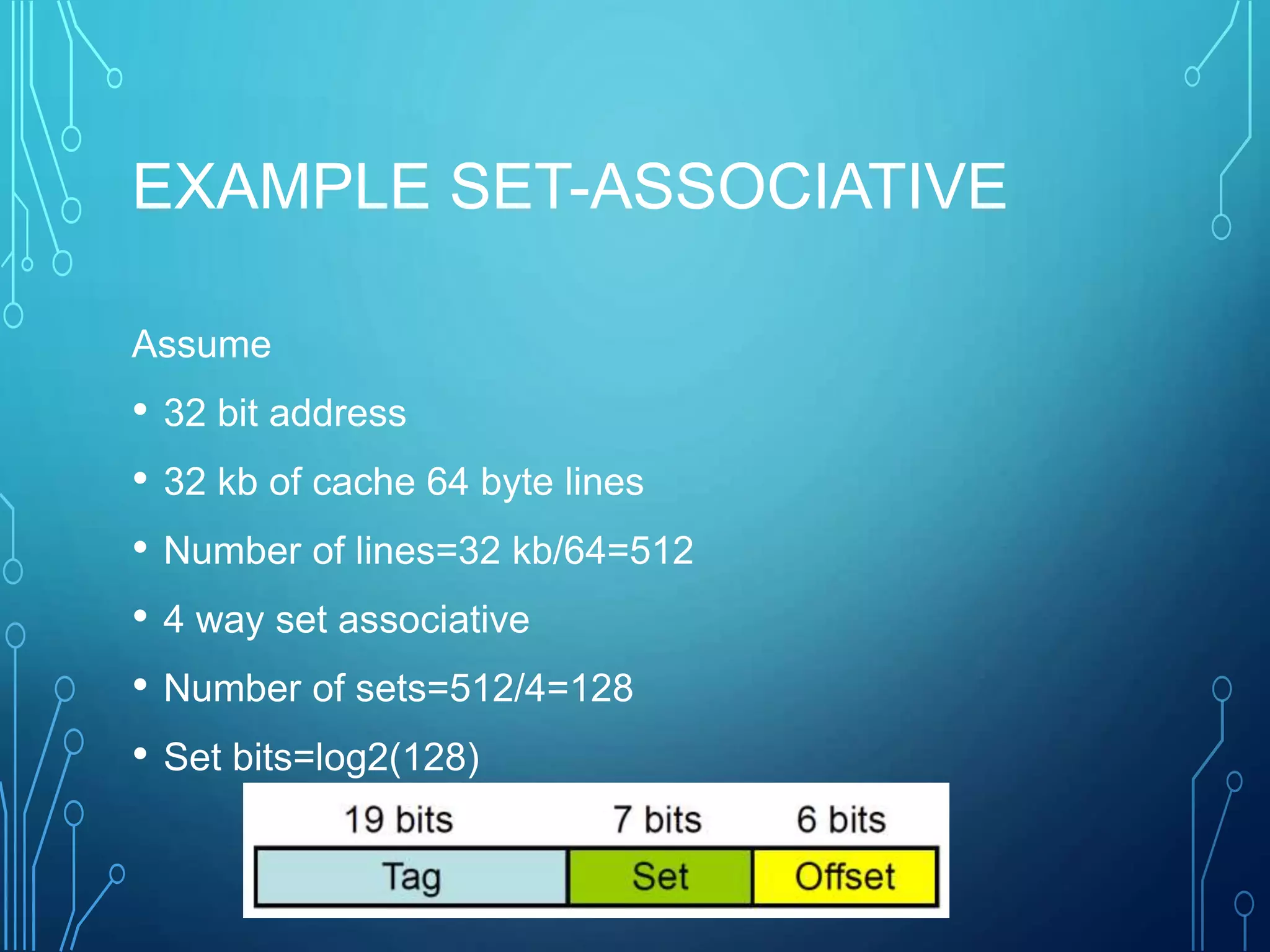

Example illustrating set-associative mapping with a specified 32-bit address, detailing cache size and set calculations.

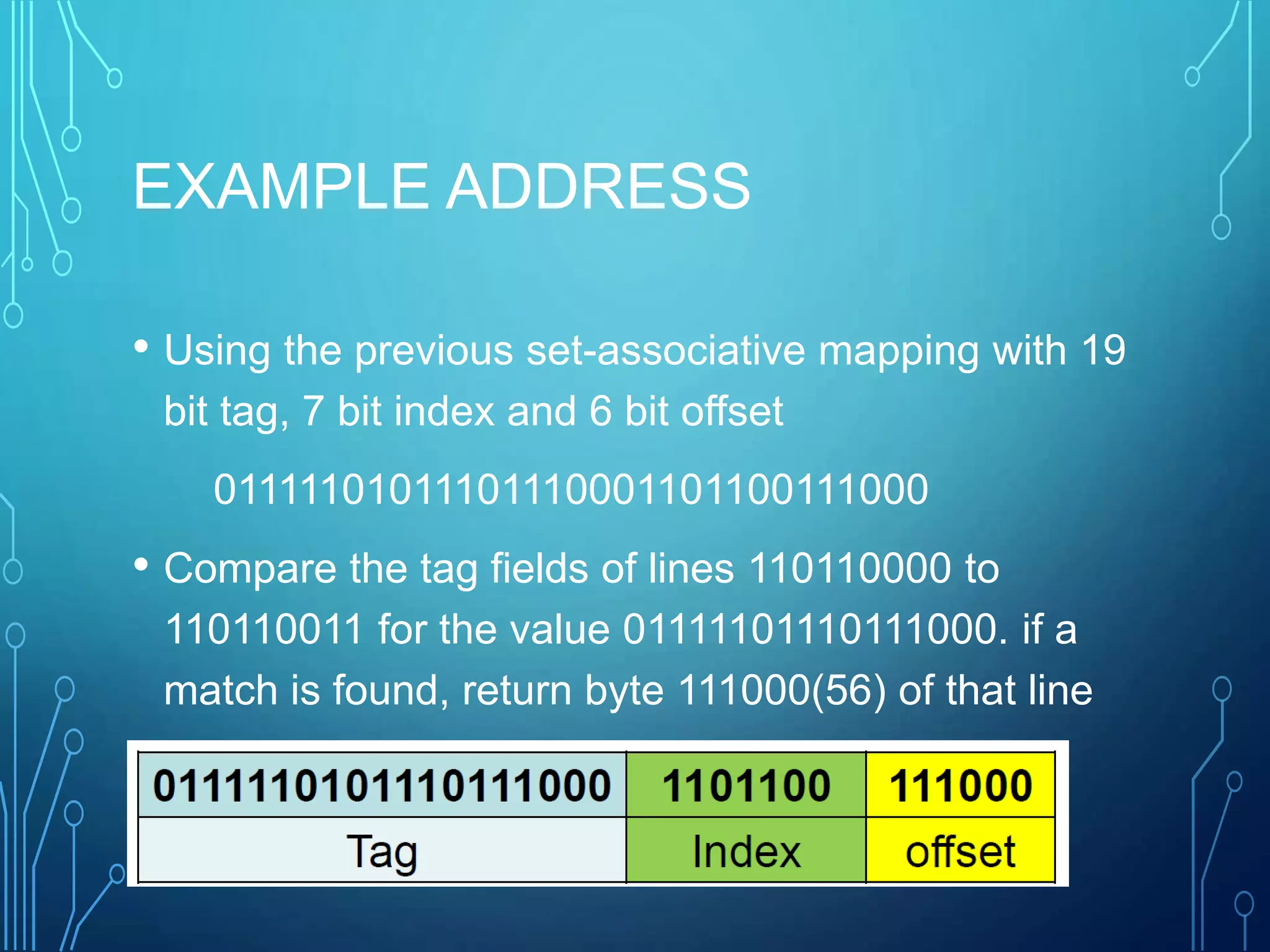

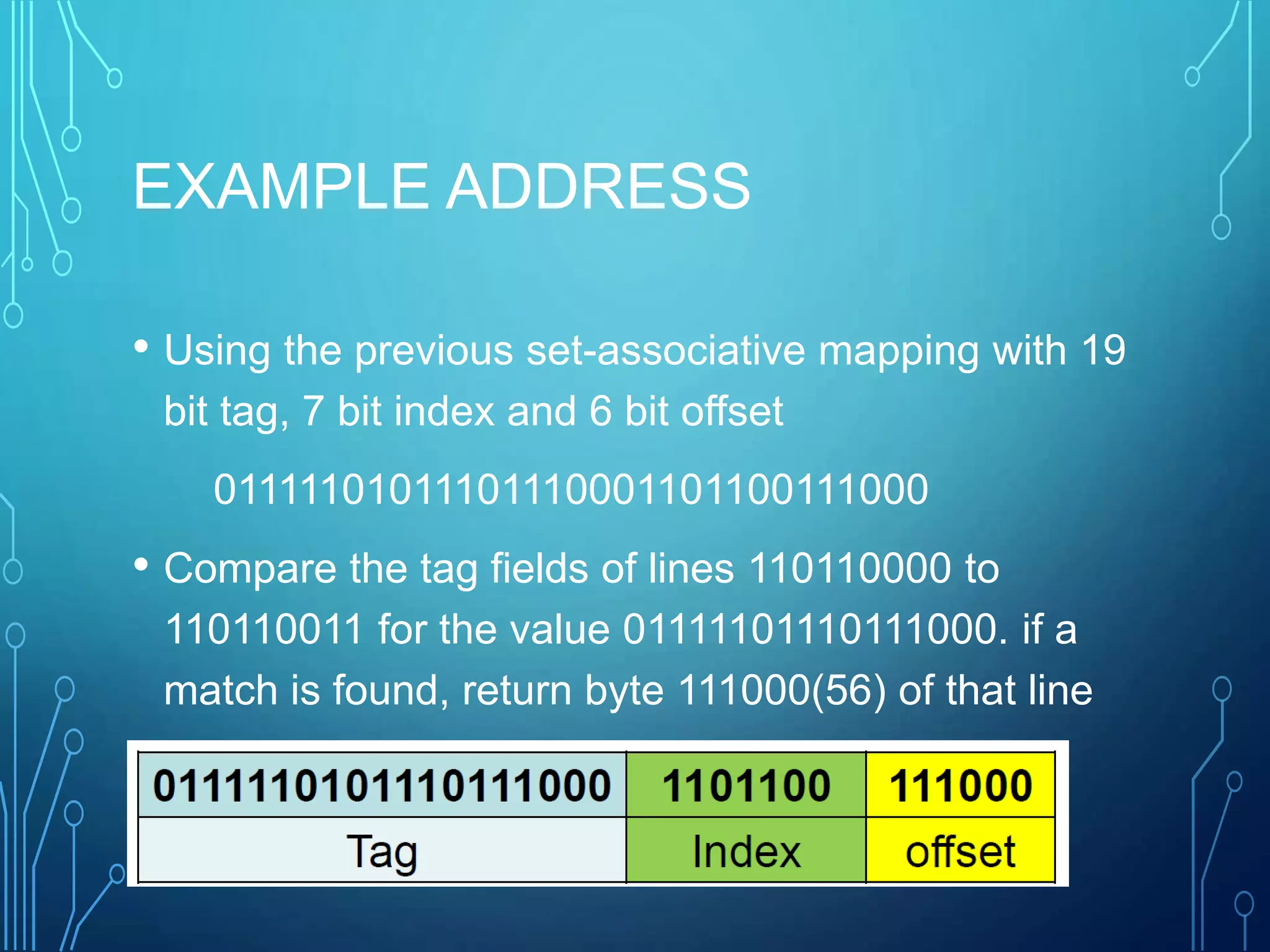

Example of an address comparison demonstrating how to find a match in set-associative mapping with specific bit allocation.

Details of a 2-way set-associative example with 24-bit address, including tag, set, and offset calculations.

Closing remarks and invitation for questions from the audience.