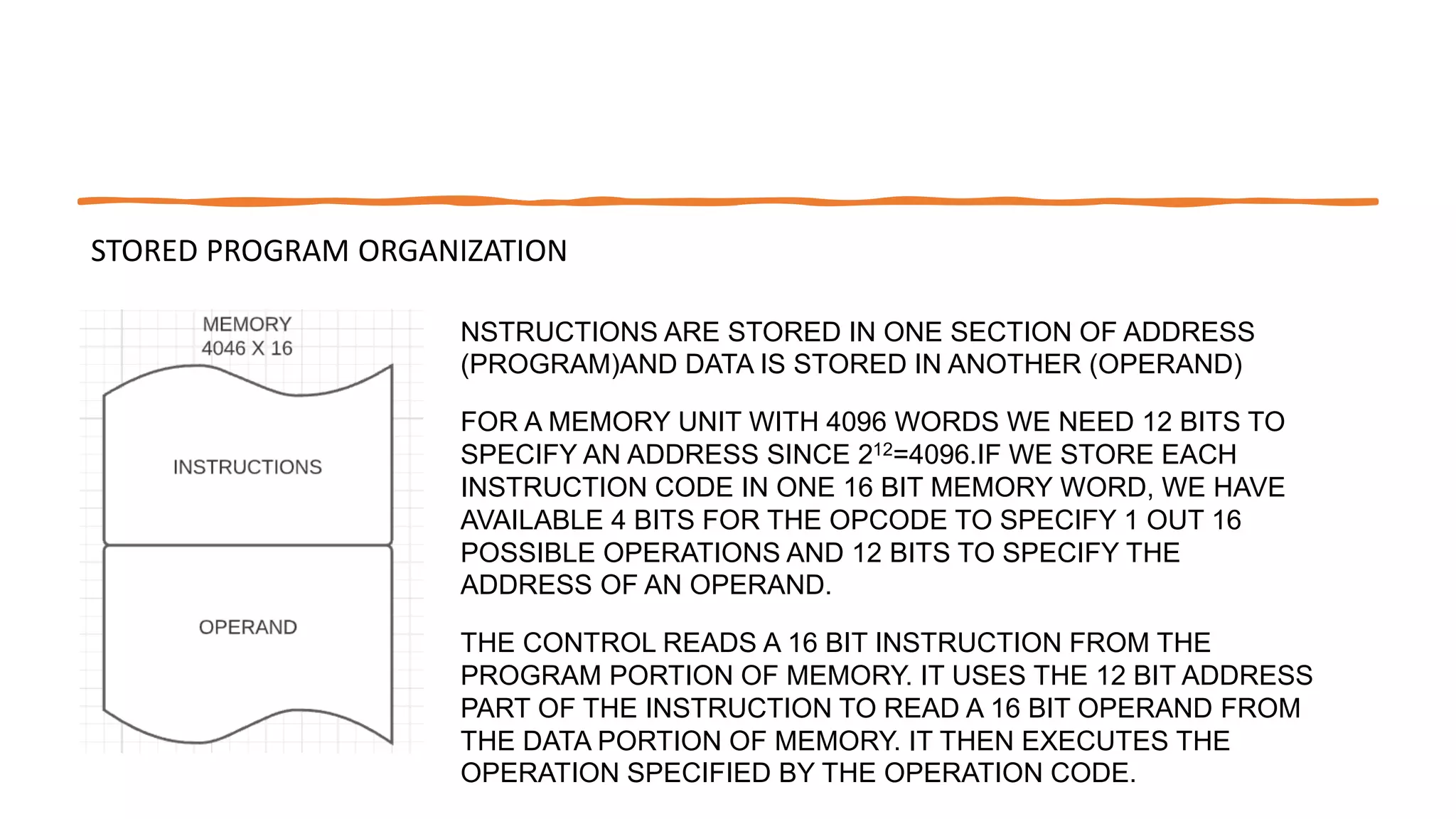

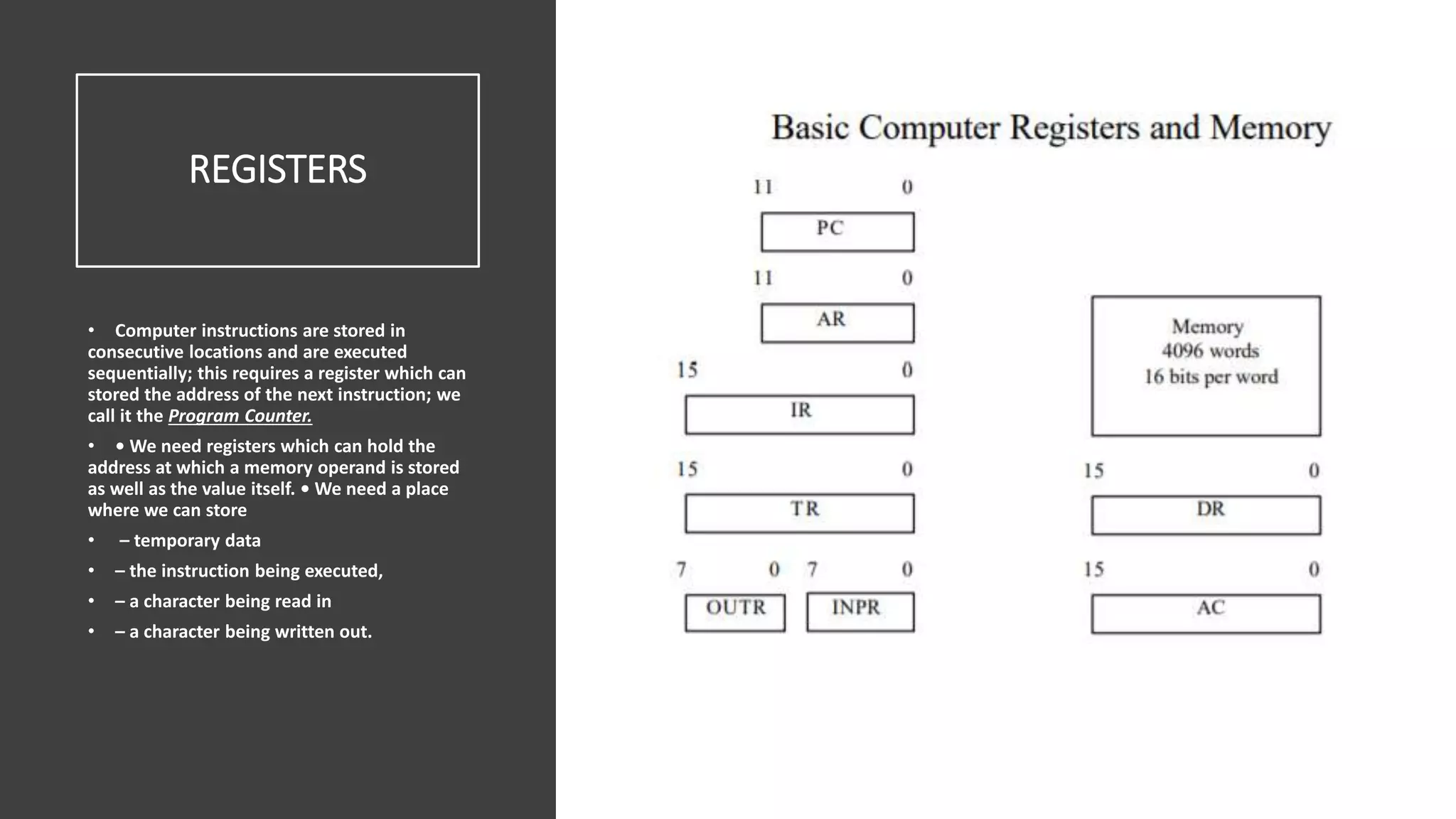

This document provides an overview of memory reference instructions in a computer system. It begins by defining the prerequisites for understanding memory reference instructions, including instruction codes, operation codes, and addresses. It then defines what a memory reference instruction is and lists some common terminology. The document outlines the basic components of a computer including registers like the program counter, accumulator, and data register. It describes direct and indirect addressing modes and provides examples of different memory reference instruction codes. Finally, it presents the control flowchart and lists some common memory reference instructions and their corresponding micro-operations.

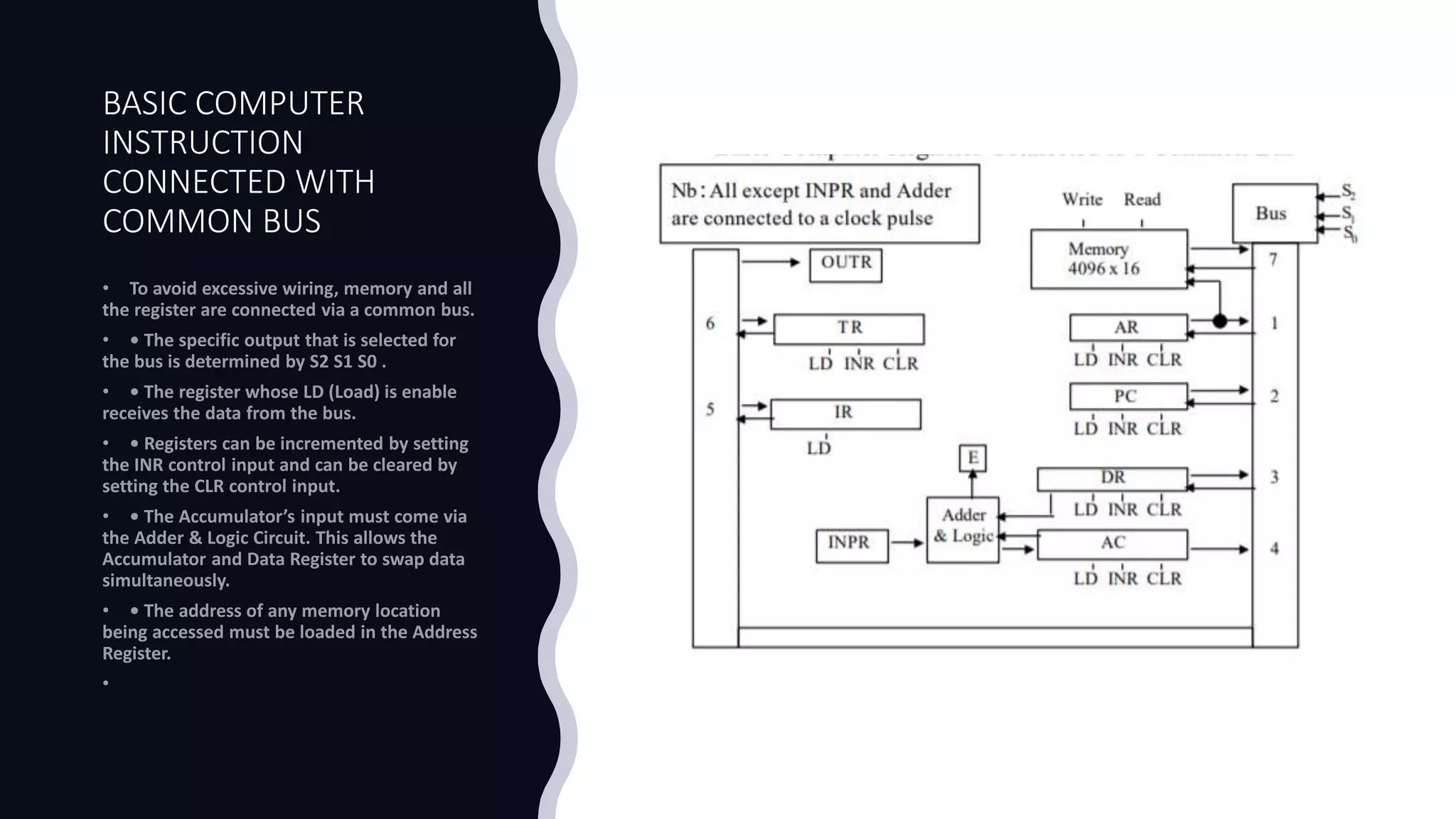

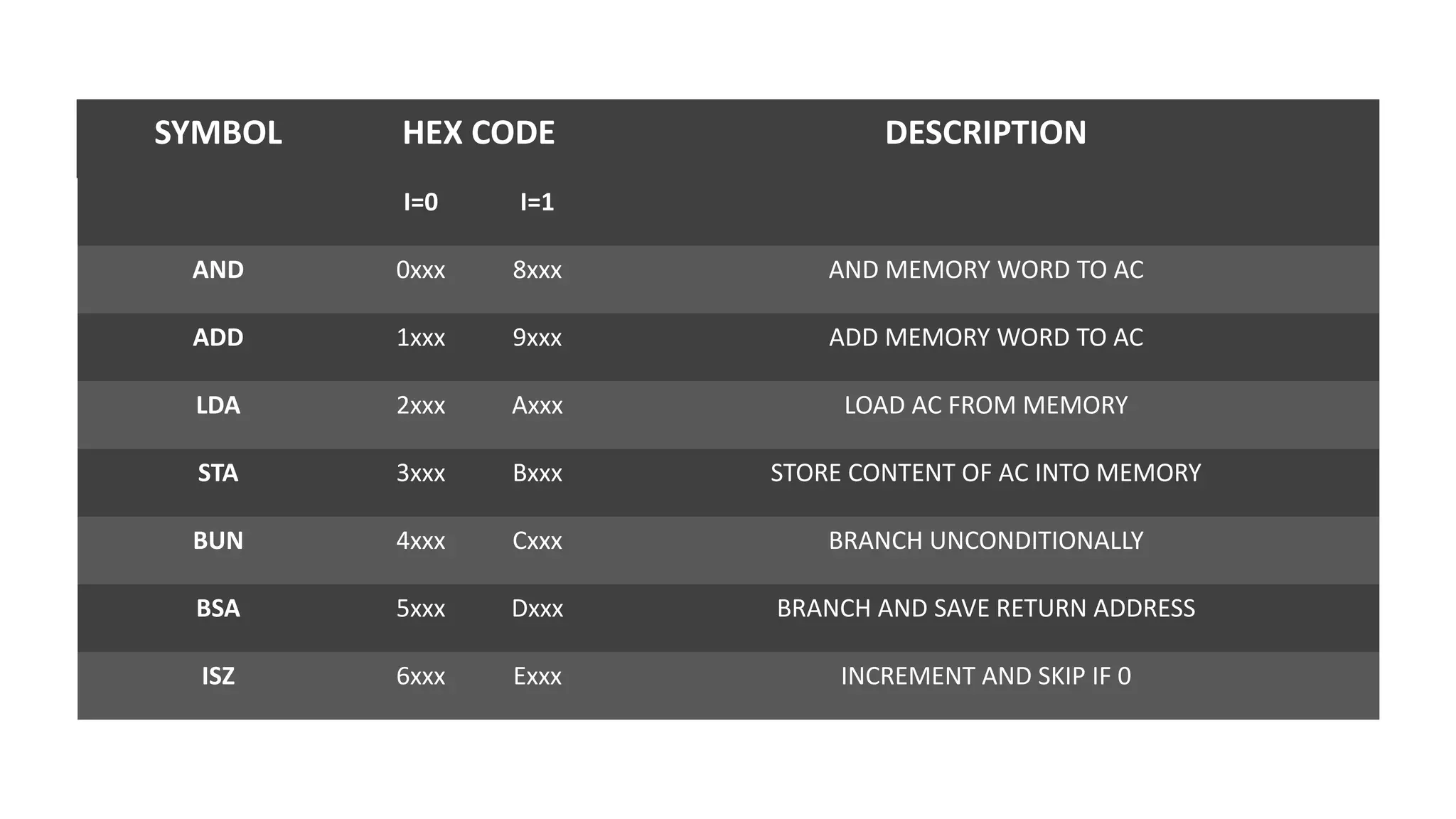

![Contents

•PREREQUISITES FOR BETTER UNDERSTANDING OF MEMORY

REFERENCE INSTRUCTIONS[MRI]

•WHAT IS MEMORY REFERENCE INSTRUCTION?

•SOME TERMINOLOGIES.

•NECESSARY INSTRUCTIONS IN MRI.

•CONTROL FLOW CHART AND FLOW CHART FOR MEMORY](https://image.slidesharecdn.com/memoryreferenceinstructions-210911085731/75/Memory-Reference-Instructions-3-2048.jpg)

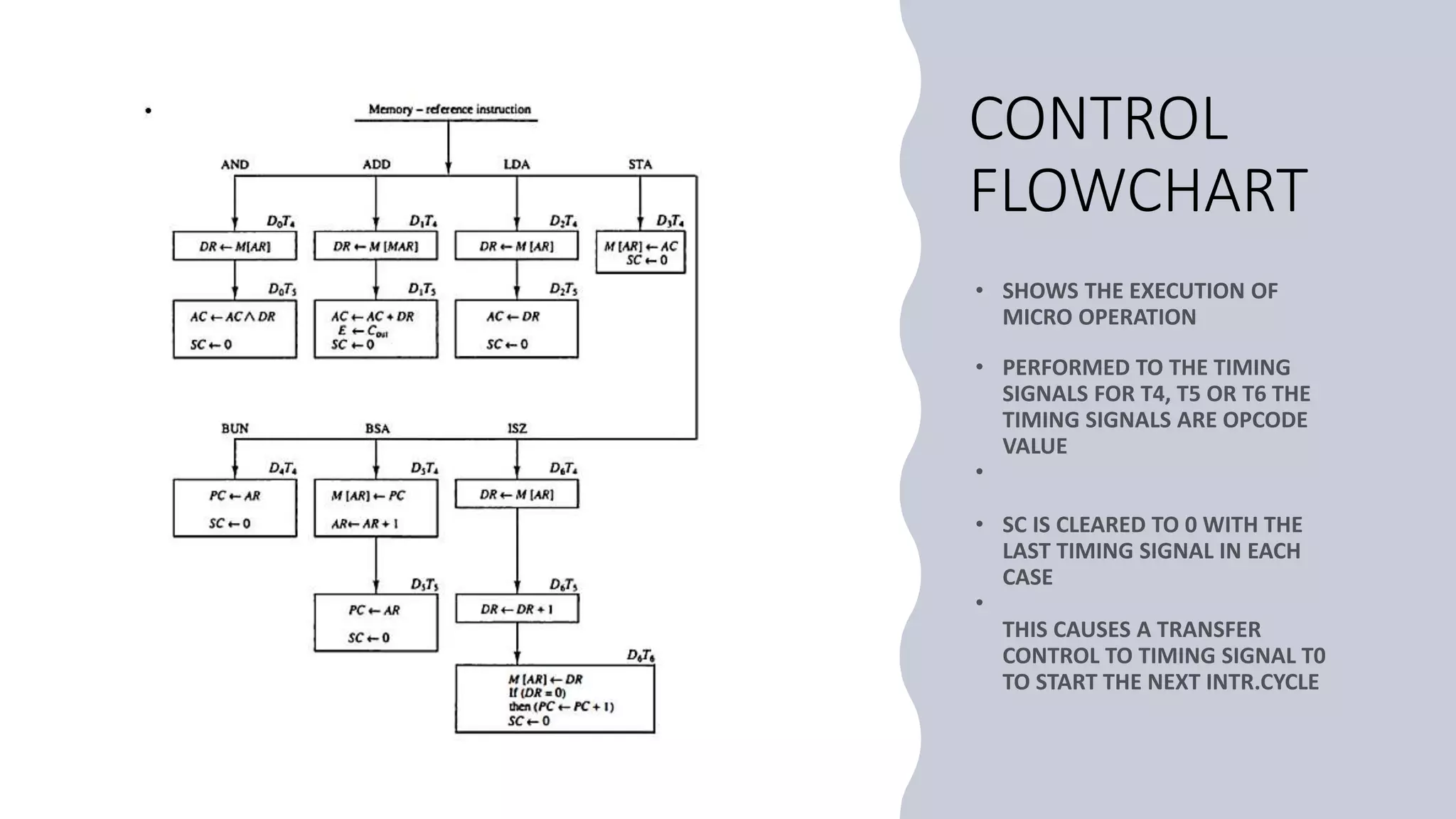

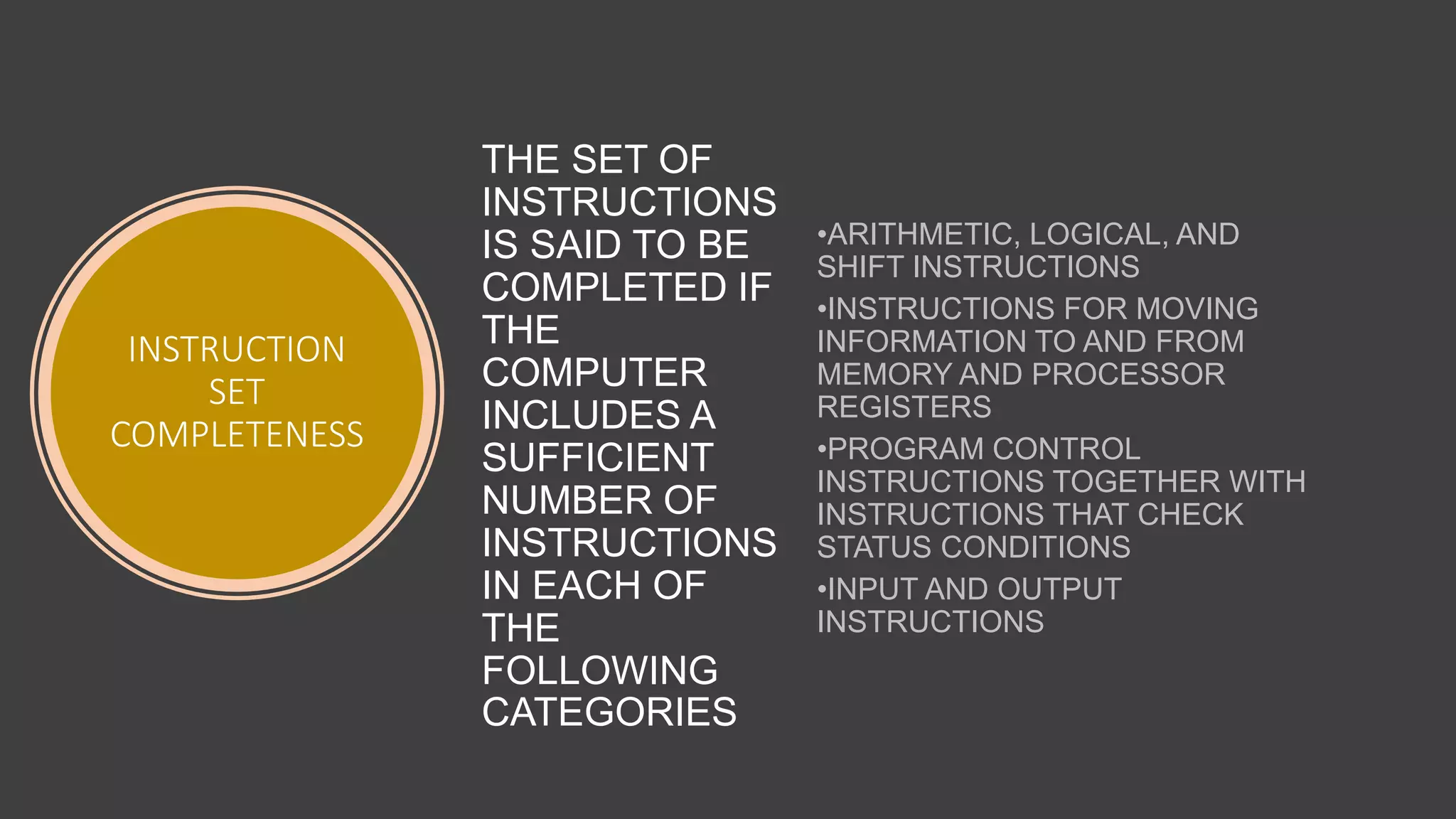

![MICRO-OPERATIONS

AND D0 AC ← AC M[AR] D0T4: DR ← M[AR]

D0T5: AC ← AC DR , SC ←0

ADD D1 AC ← AC + M[AR] , E ←Cout D1T4: DR ← M[AR]

D1T5: AC ← AC + DR , E ←Cout ,SC ←0

LDA D2 AC ← M[AR] D2T4: DR ← M[AR]

D2T5: AC ← DR ,SC ←0

STA D3 M[AR] ← AC D3T4: M[AR] ← AC , SC ←0

BUN D4 PC ← AR D4T4: PC ← AR , SC ←0

BSA D5 M[AR] ← PC , PC ← AR + 1 D5T4: M[AR] ← PC , AR ← AR + 1

D5T5: PC ← AR , SC ←0

ISZ D6 M[AR] ← M[AR] + 1 ,

If M[AR] + 1 =0 then PC ← PC + 1

D6T4: DR ← M[AR]

D6T5: DR ← DR + 1

D6T6: M[AR] ← DR , if (DR =0) then (PC ←PC+ 1) ,SC ←0](https://image.slidesharecdn.com/memoryreferenceinstructions-210911085731/75/Memory-Reference-Instructions-17-2048.jpg)