The document outlines three essential principles for solution product development, focusing on innovation, transparency, and quality. It details a methodology for automating the verification process of system-on-chip (SoC) designs, highlighting the significant reduction in time and effort compared to manual methods. Case studies demonstrate increased verification productivity, with substantial time savings and rapid test bench generation capabilities.

![6/11

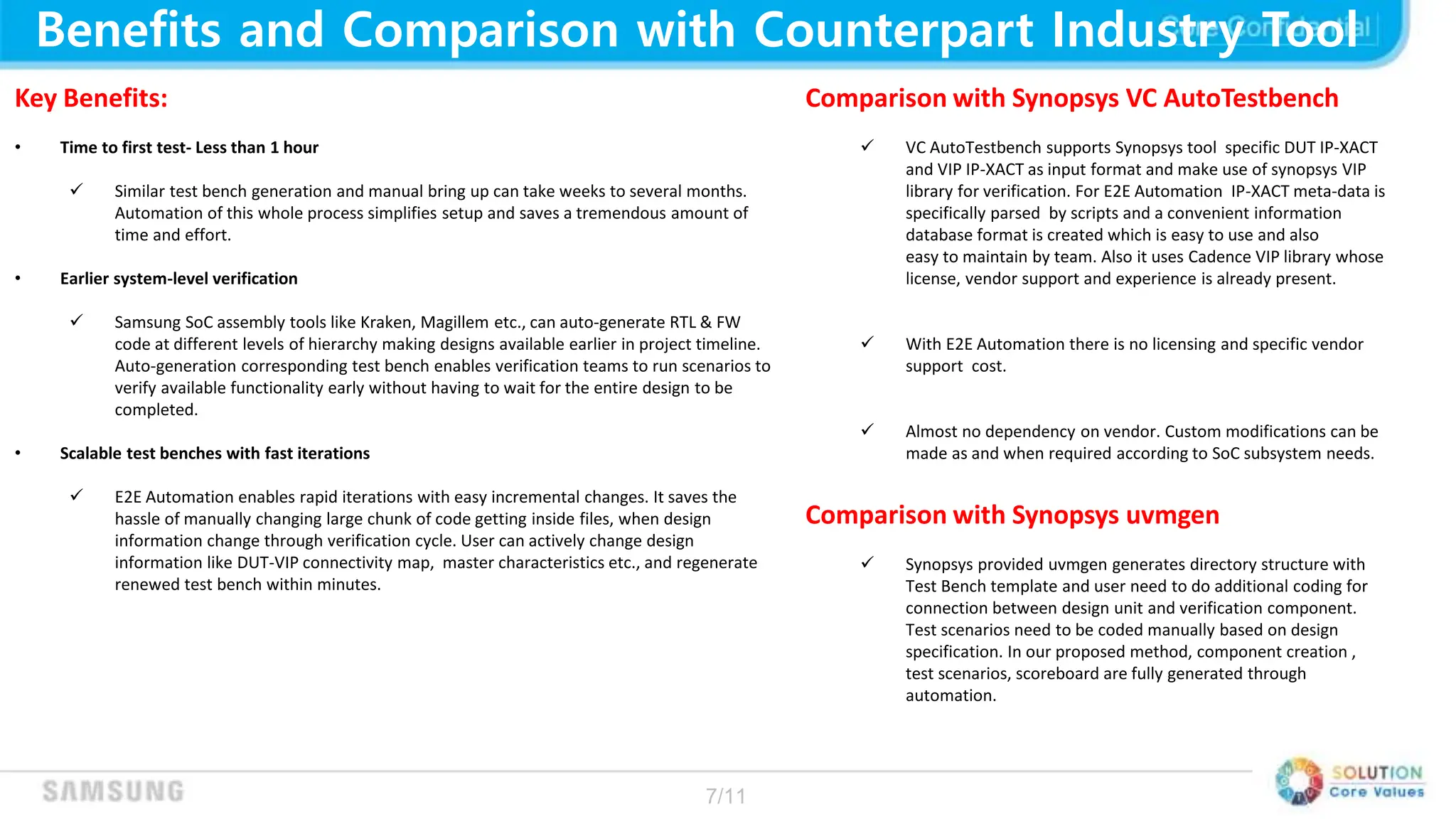

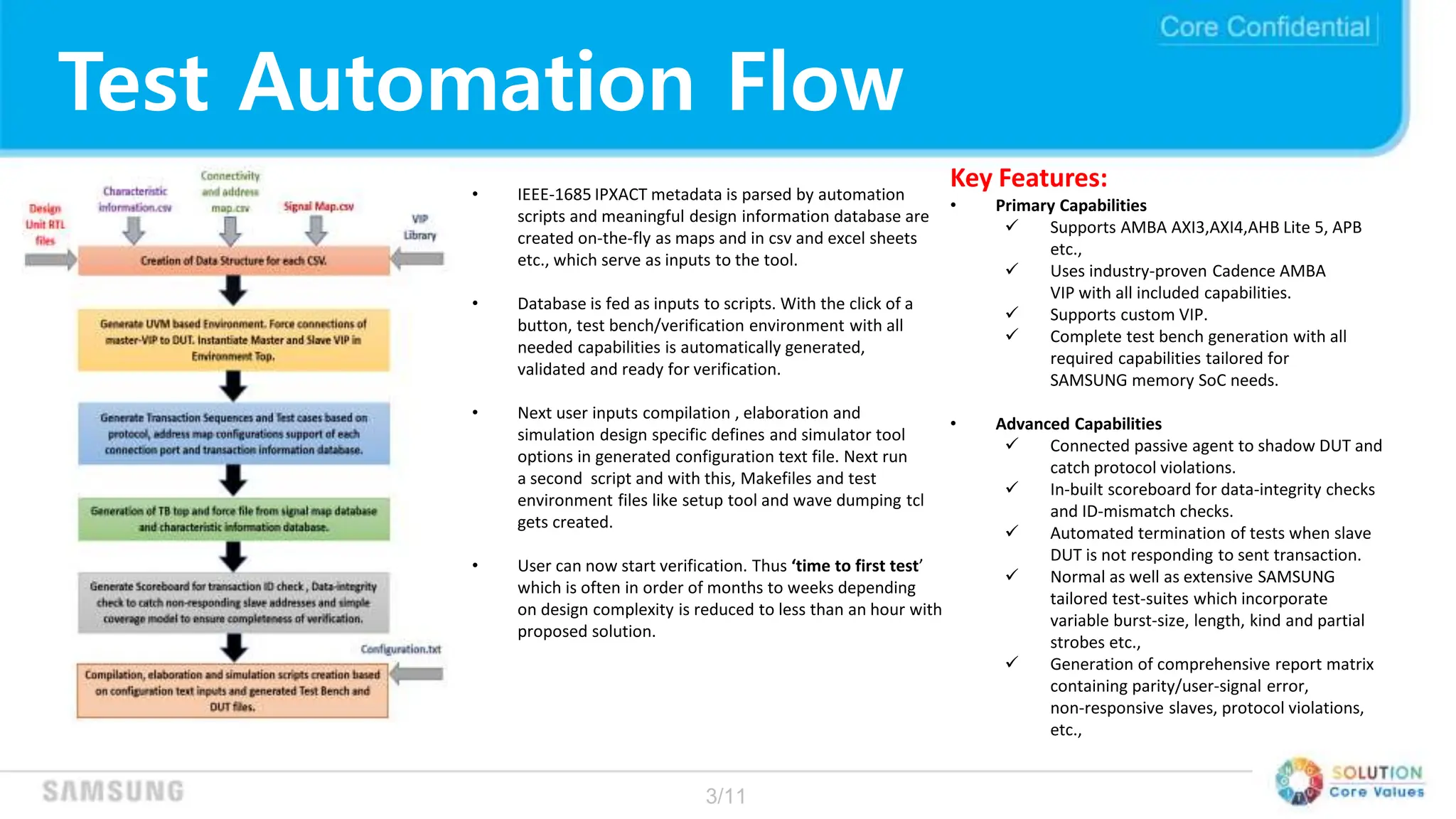

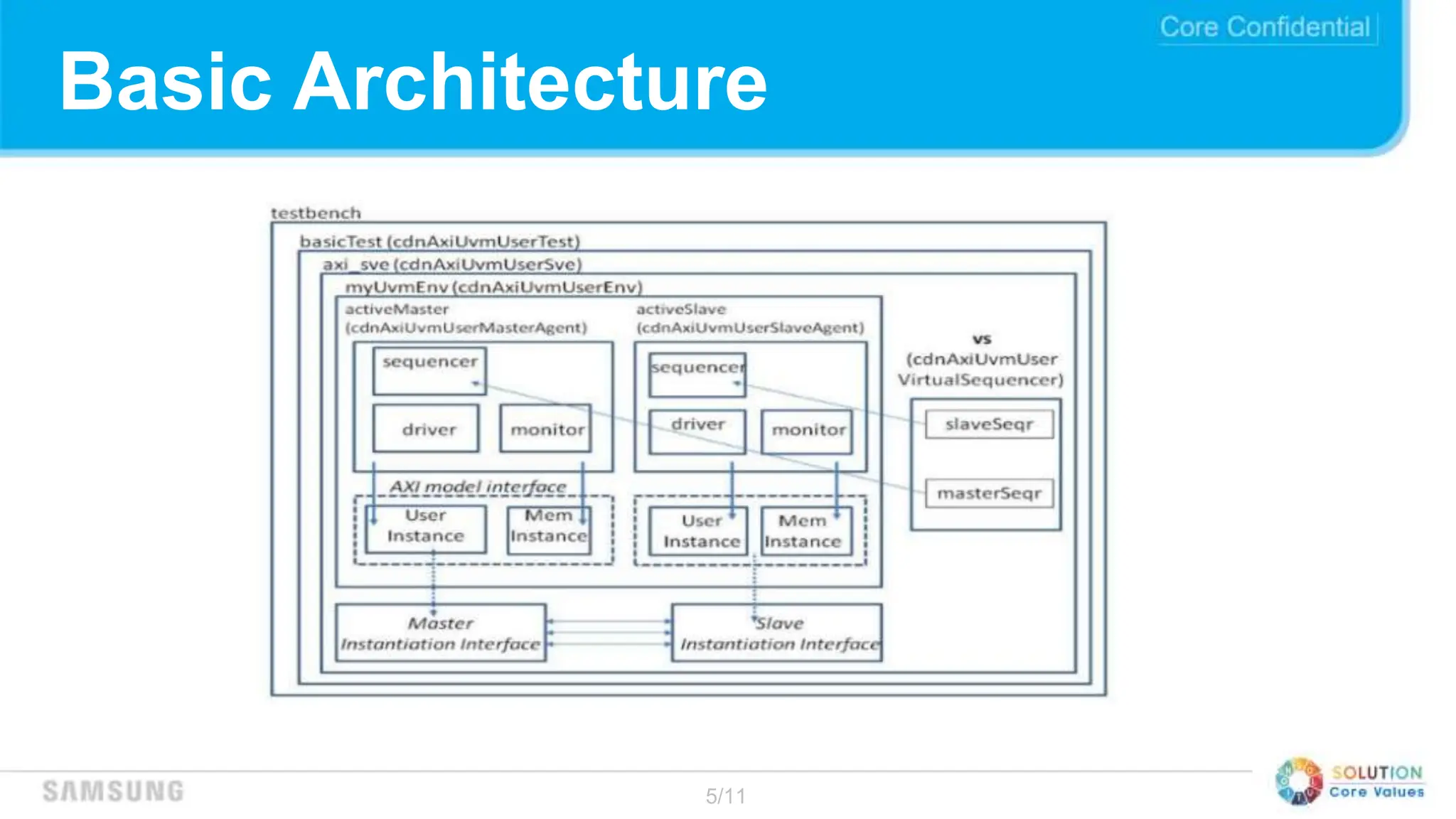

Case Studies and Simulation Results

Section

AXI Bus Matrix:

32 Master and 32 Slaves

AHB Bus Matrix:16 Masters and 16

Slaves

Automation Manual Automation Manual

Custom Standard Input format

creation time(A)

2 hours

(partial scripting involved)

Not Applicable 1 hours

(partial scripting

involved)

Not Applicable

Verification Environment creation(B)

Scripts create all these

components

(20 seconds approx.)

24 hours

Scripts create all

these components

(10 seconds approx.)

12 hours

Tb Top Creation(C) 24 hours 12 hours

Scoreboard Creation(D) 8 hours 4 hours

Test Case coding(E) 8 hours 4 hours

Configuration Inputs and simulation

script creation(F)

6 hours 3 hours

Simulation time to attain 100%

coverage(G)

72 hours 96 hours 56 hours 82 hours

Verification time for 1 Cycle [A:G] 74 hours 166 hours 57 hours 117 hours

Verification time for SoC Project

[A:G]+[A,D:G]x3

296 hours 592 hours 228 hours 432 hours

Saved Verification Time 500 hours!

Results:

• Tried and tested for ELAN SSD Bus Matrix

Deployed Successfully in ELAN E2E

verification. Verification productivity

improved by more than 70% (Complete E2E

verification done in 3 weeks compared to 3

months earlier)

1 document bug and 8 RTL bugs are caught

immediately within 1 week of verification

for just 2 iterations of RTL version. This proves the

effectiveness of test-suite and capabilities of

auto-generated test-bench.

Future Enhancements

Currently E2E Automation is deployed for SoC

NOC/NIC verification. It shall be extended to

SRAM SECDED E2E verification and other bus

matrix verification of similar nature.

Currently supports protocols like AXI, AHB, APB.

Can be extended to other extensive buses.](https://image.slidesharecdn.com/osvcmeta-databasedsimulationautomationtoovercomeverificationchallengesofsocinterconnectbusmatrix-240426082511-867022d7/75/OSVC_Meta-Data-based-Simulation-Automation-to-overcome-Verification-Challenges-of-SoC-Interconnect-Bus-Matrix-pptx-7-2048.jpg)