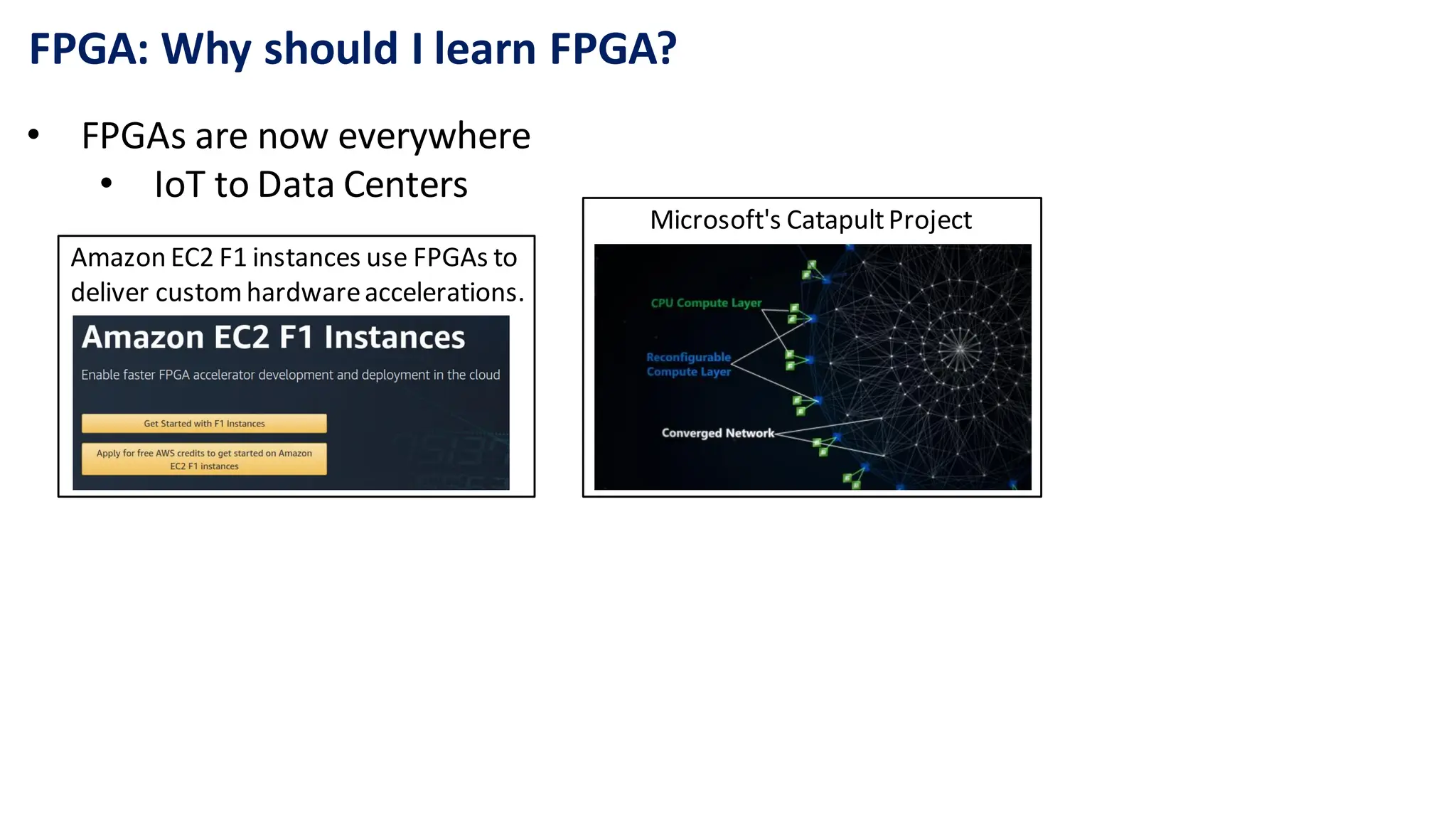

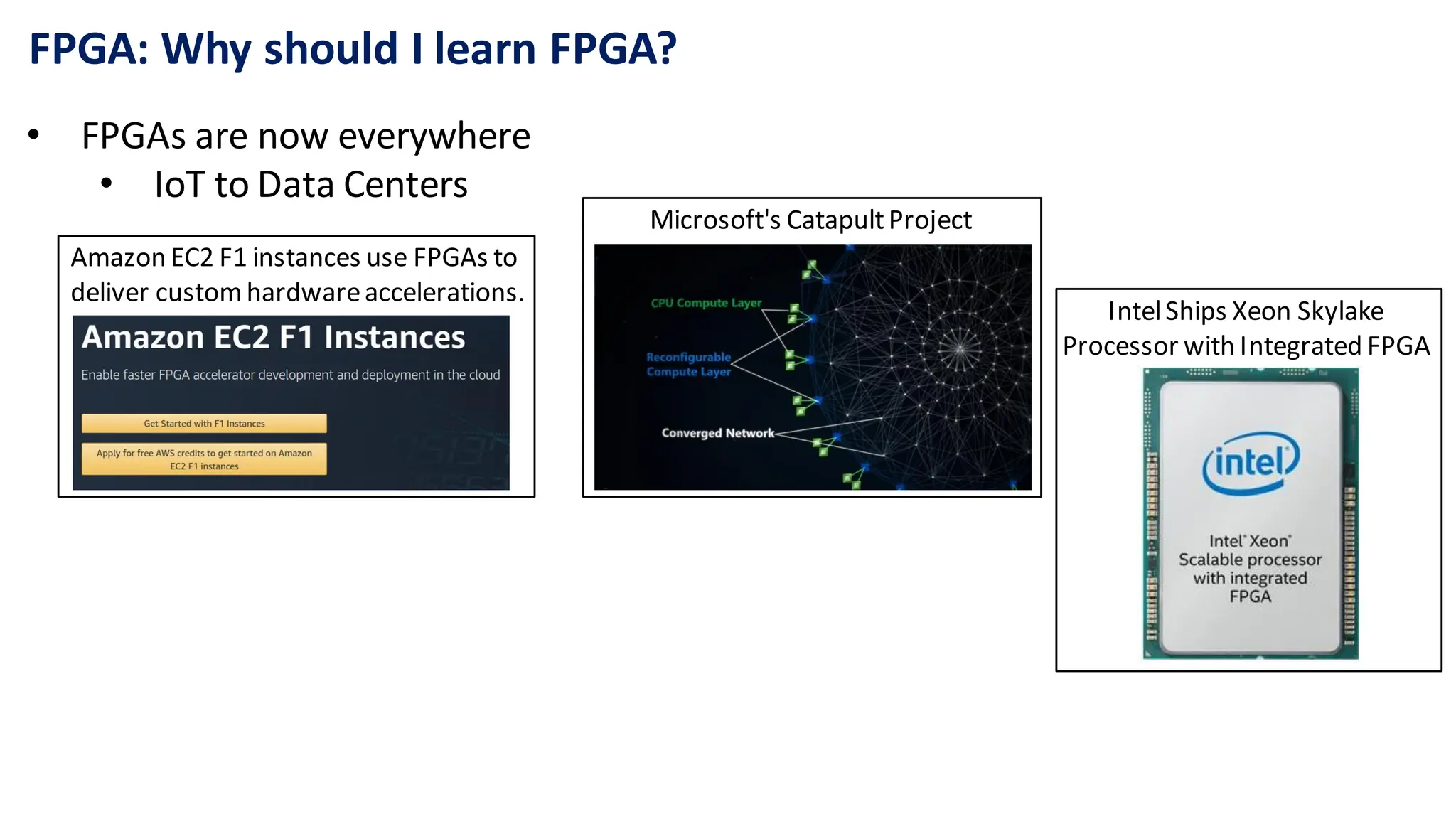

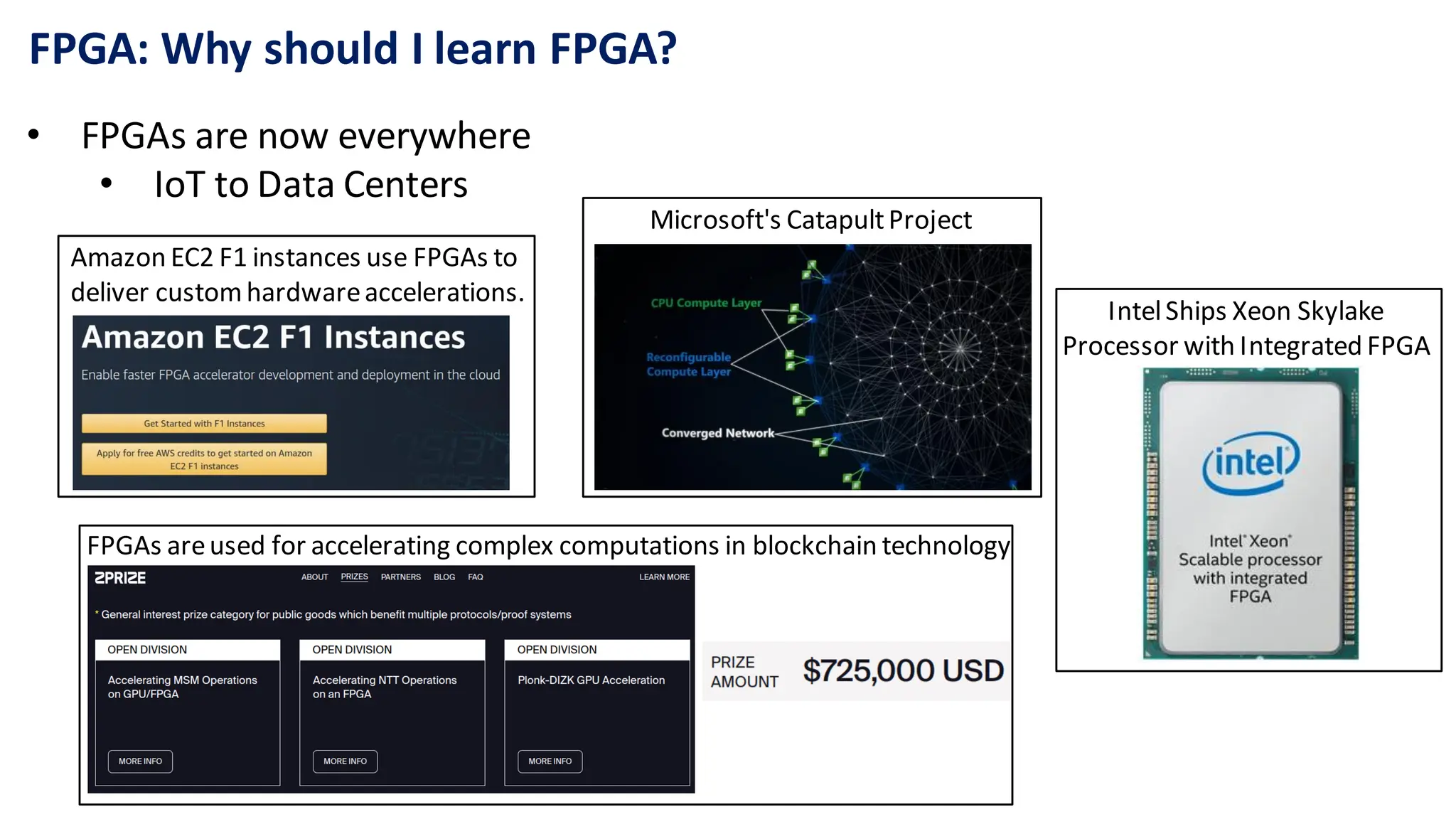

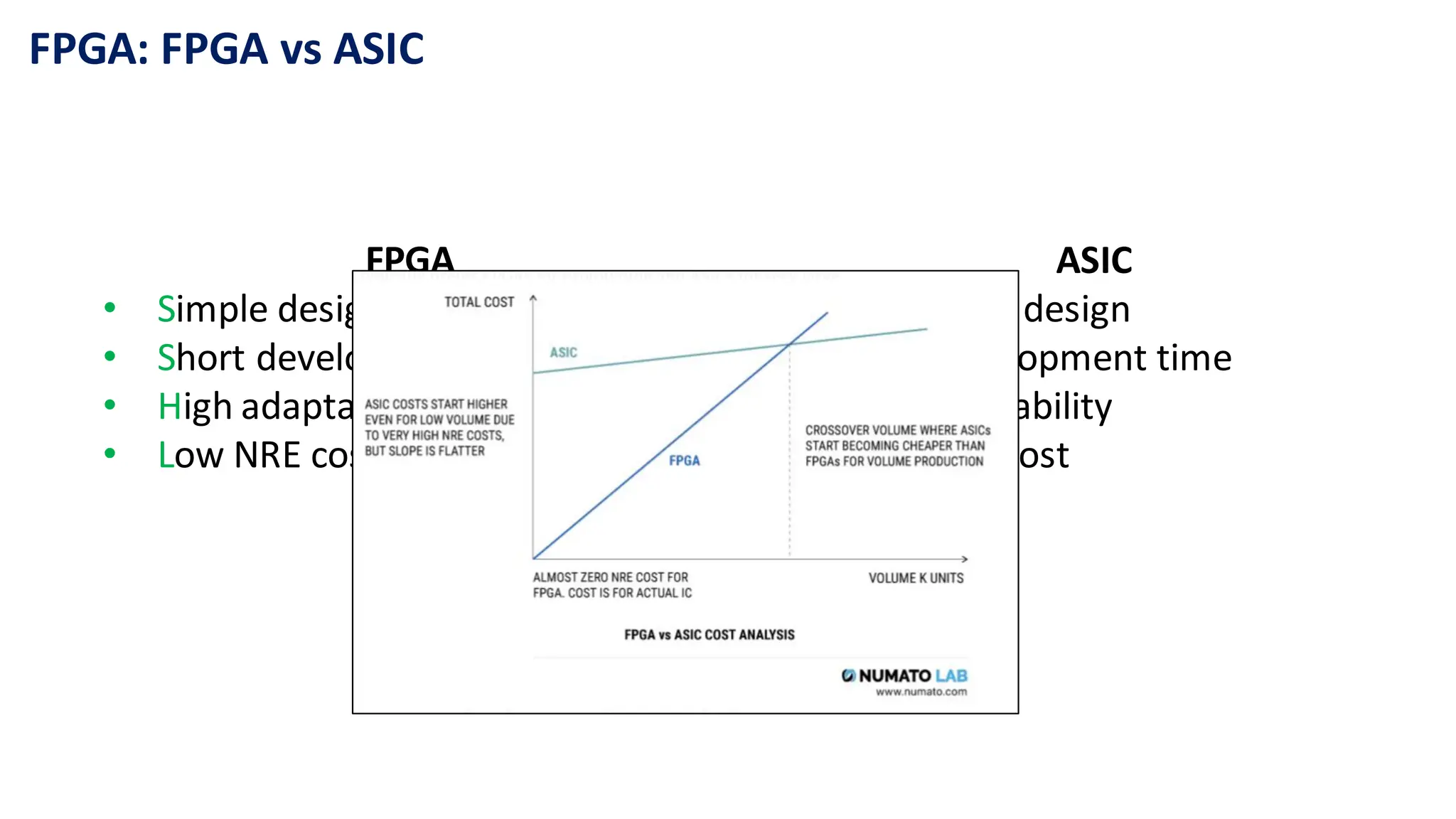

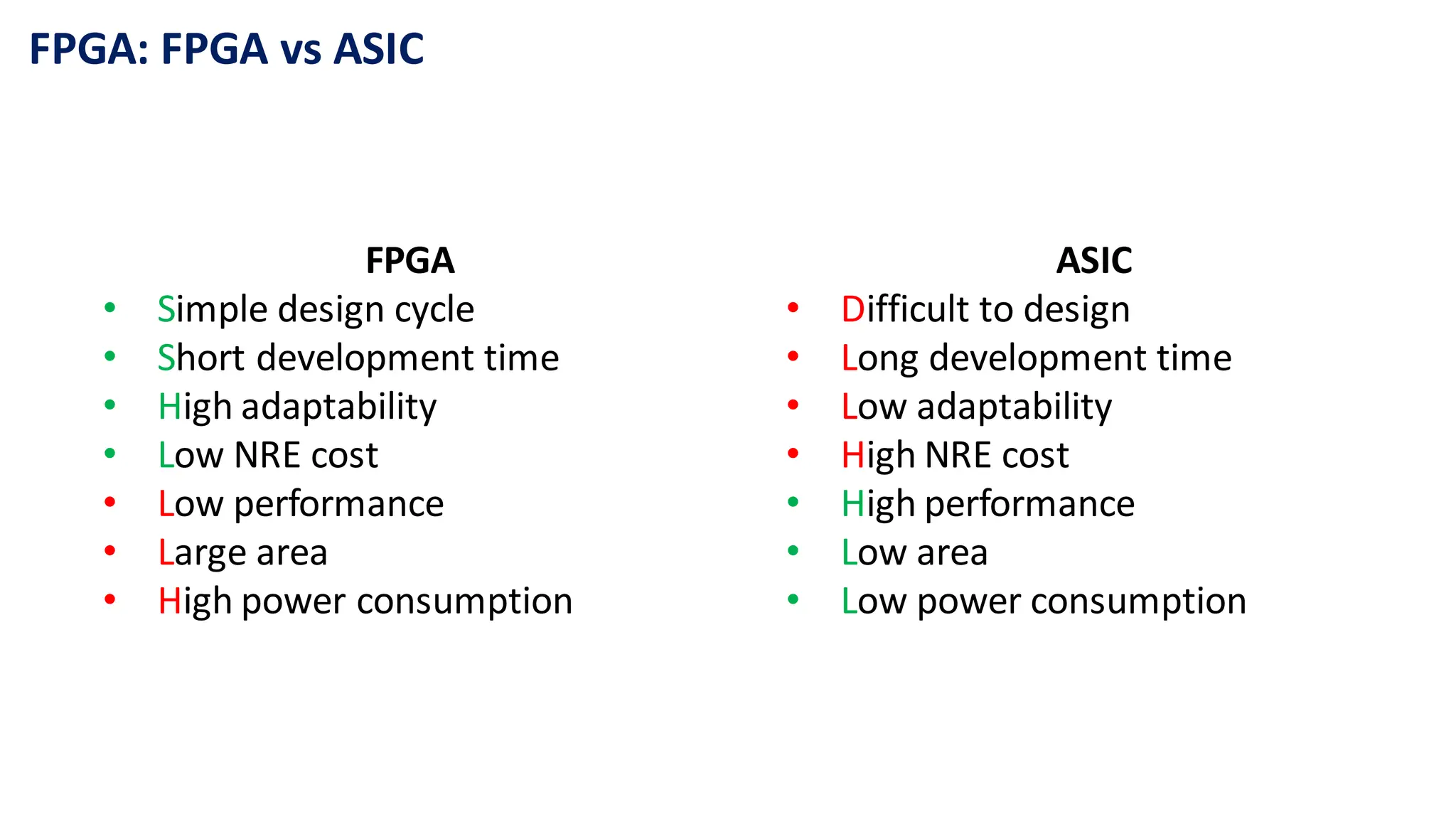

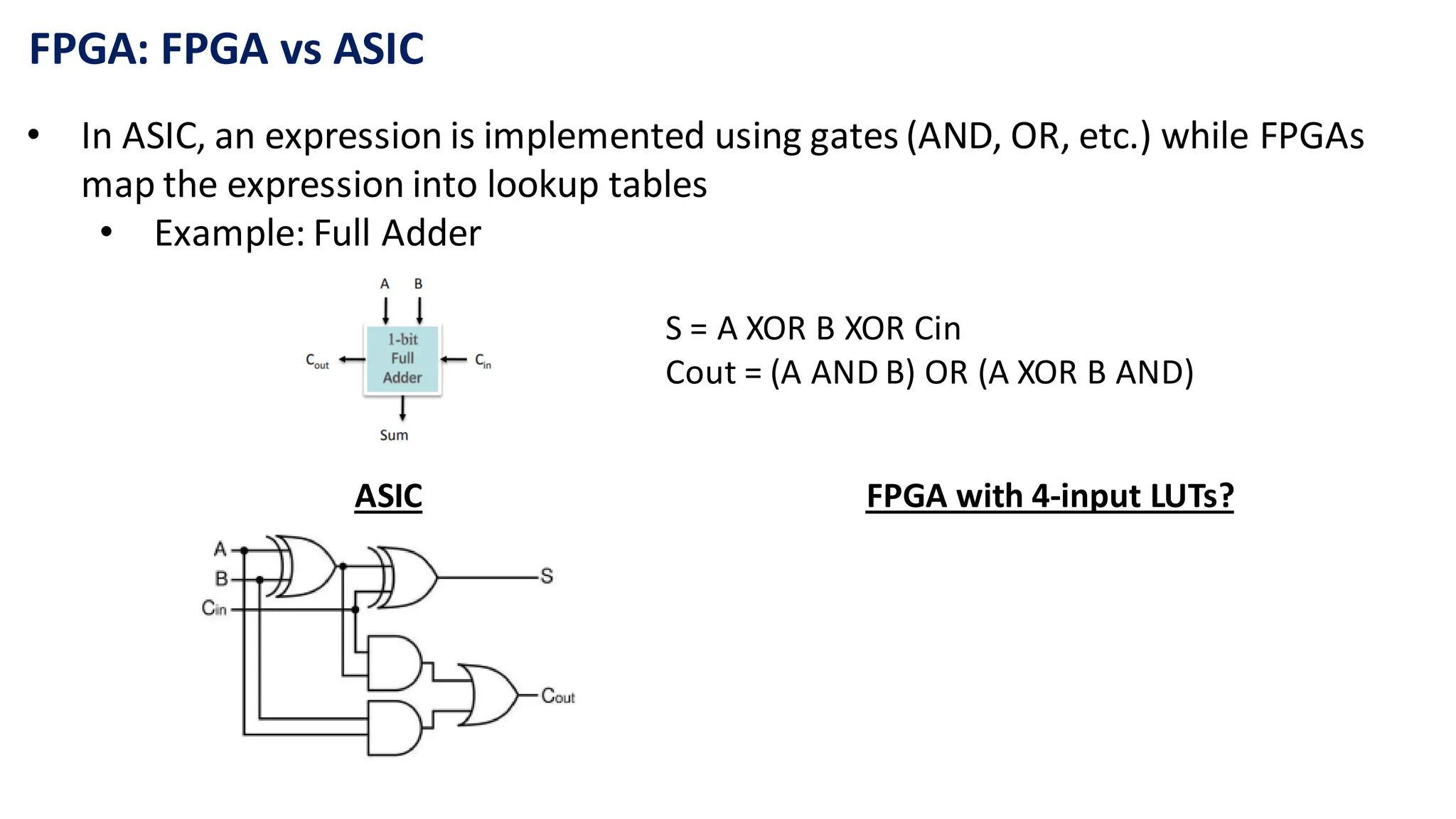

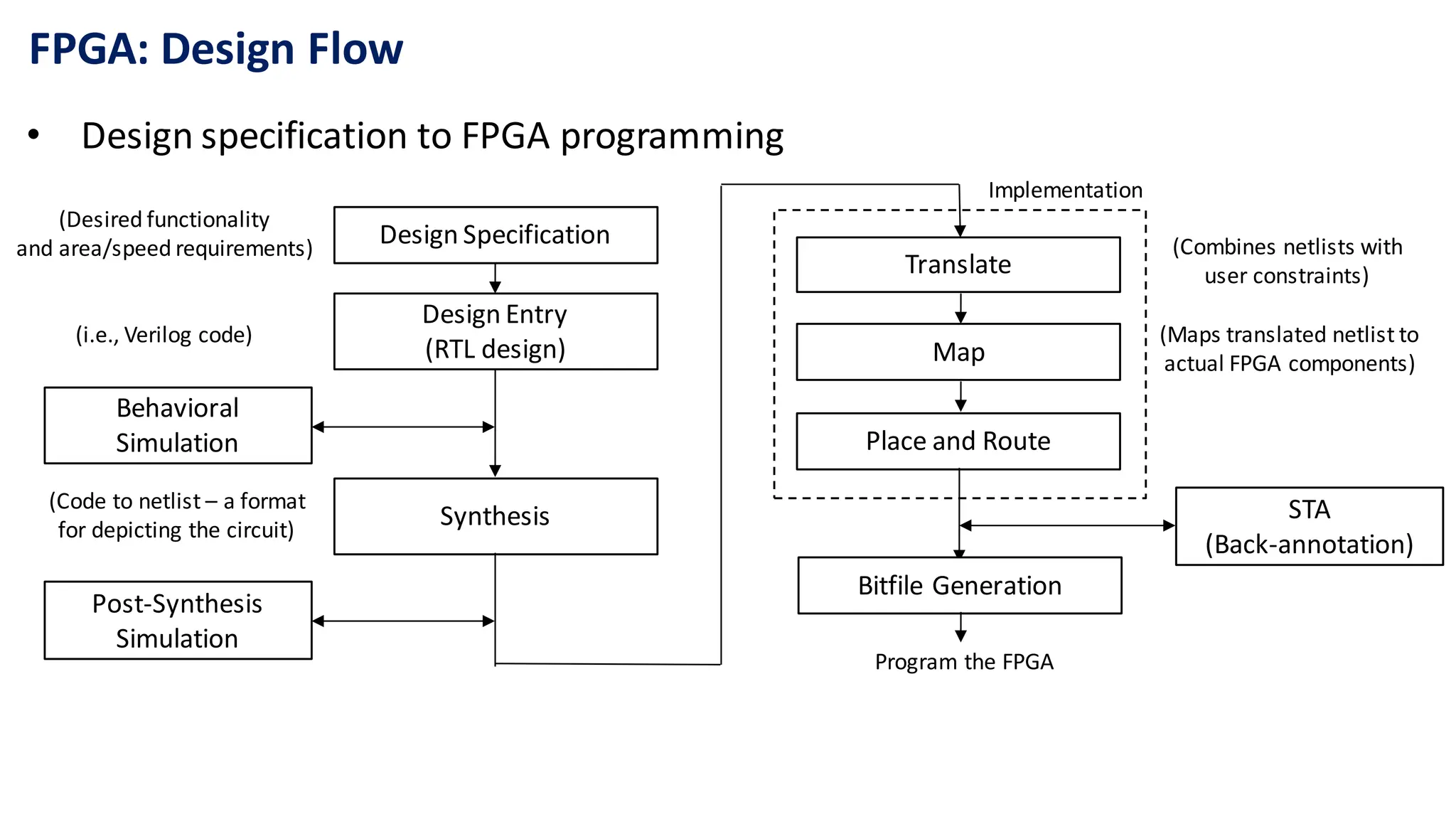

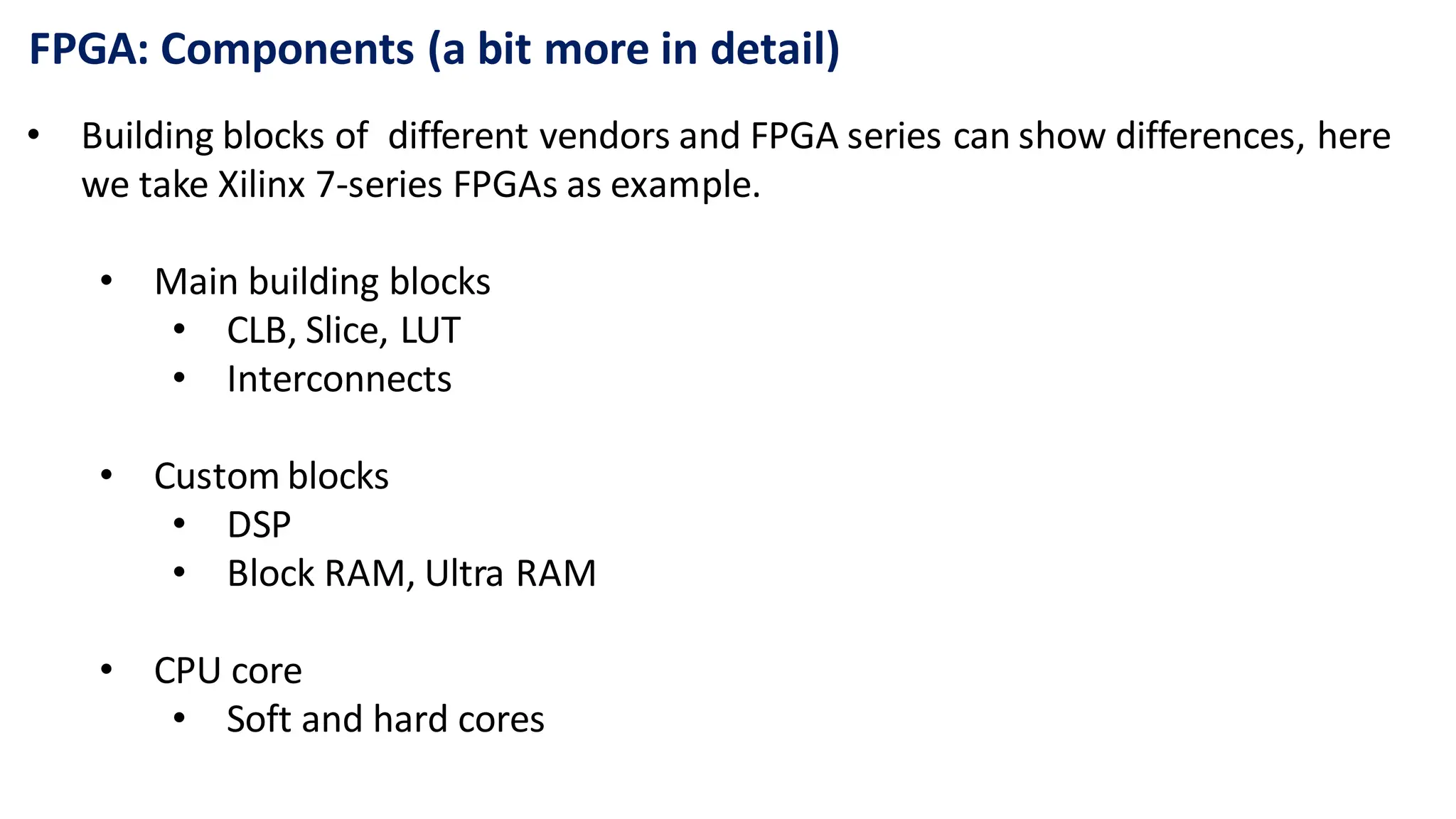

The document provides an introduction to Field Programmable Gate Arrays (FPGAs), outlining their definitions, functionalities, historical developments, and components. It covers the evolution of FPGAs from early programmable devices to modern high-capacity configurations and highlights their usage in various applications such as IoT, data centers, and machine learning. The text discusses the advantages and disadvantages of FPGAs compared to Application-Specific Integrated Circuits (ASICs) and the design flow for programming FPGAs.

![FPGA: Definition

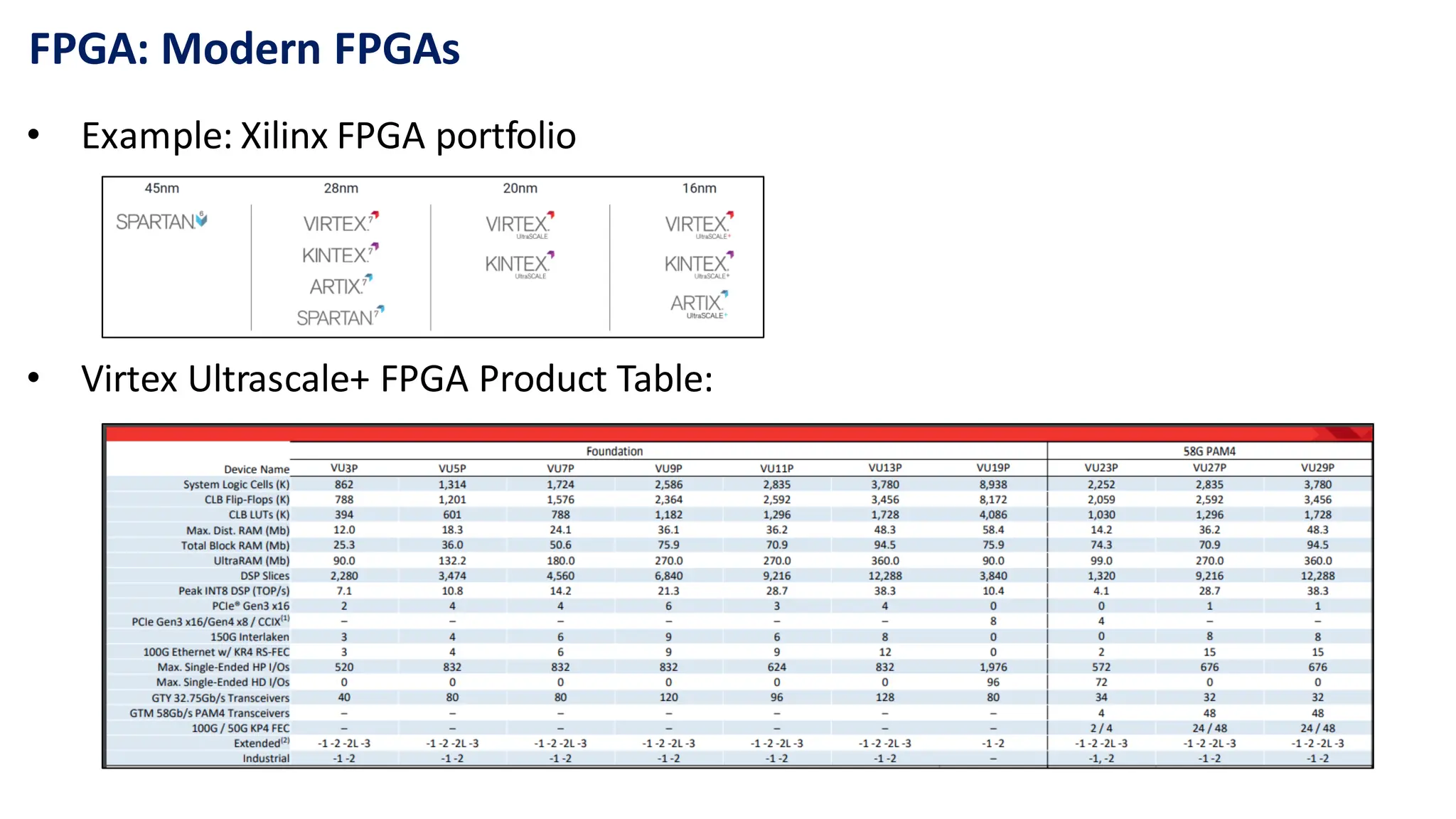

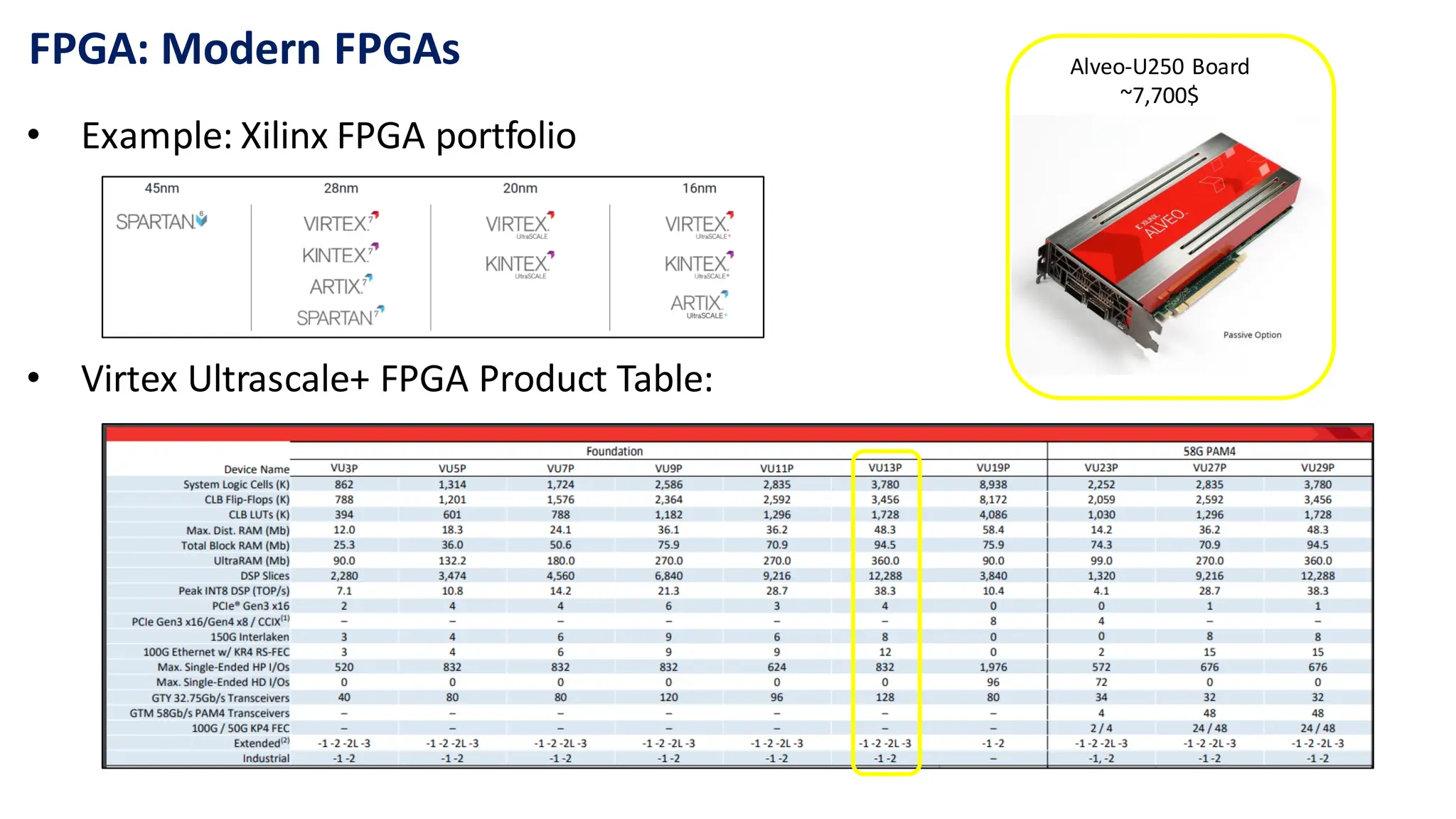

• FPGA: Field Programmable Gate Arrays

• ConfigurableLogic Blocks (CLBs)

• Programmable Interconnects

• Programmable I/O blocks

• Other functionalblocks: DSPs, Block RAMs, Ultra RAMs, ...

Image is retrieved from [https://towardsdatascience.com/introduction-to-fpga-and-its-architecture-20a62c14421c]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-3-2048.jpg)

![FPGA: A Brief History of FPGAs

• Some major inventions that led to FPGAs

• 1957 – PROM (programmable read-only memory)

• 1960 – MOSFETs (metal–oxide–semiconductor field-effect transistor)

• 1965 – Moore's Law

Image is retrieved from [https://en.wikipedia.org/wiki/Moore%27s_law]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-5-2048.jpg)

![FPGA: A Brief History of FPGAs

• Some major inventions that led to FPGAs

• 1957 – PROM (programmable read-only memory)

• 1960 – MOSFETs (metal–oxide–semiconductor field-effect transistor)

• 1965 – Moore's Law

• 1970 – EPROM

• 1975 – PLA (Programmable Logic Array)

• 1977 – PAL (Programmable Array Logic)

Image is retrieved from [https://www.electronics-tutorial.net/programmable-logic-devices/programmable-array-logic/]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-7-2048.jpg)

![FPGA: First FPGA

• First FPGA: XC2064

• 8x8 grid of CLBs (Image from the Patent is a simplified 3x3 version)

• Each CLB has 4 inputs and 2 outputs

• Comb. Logic (Lookup Table – LUT)

• D-FF

• Multiplexers (MUX)

FPGA connections from Xilinx FPGA Patent

Images are retrieved from [https://semiwiki.com/fpga/290990-reverse-engineering-the-first-fpga-chip-xilinx-xc2064/]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-10-2048.jpg)

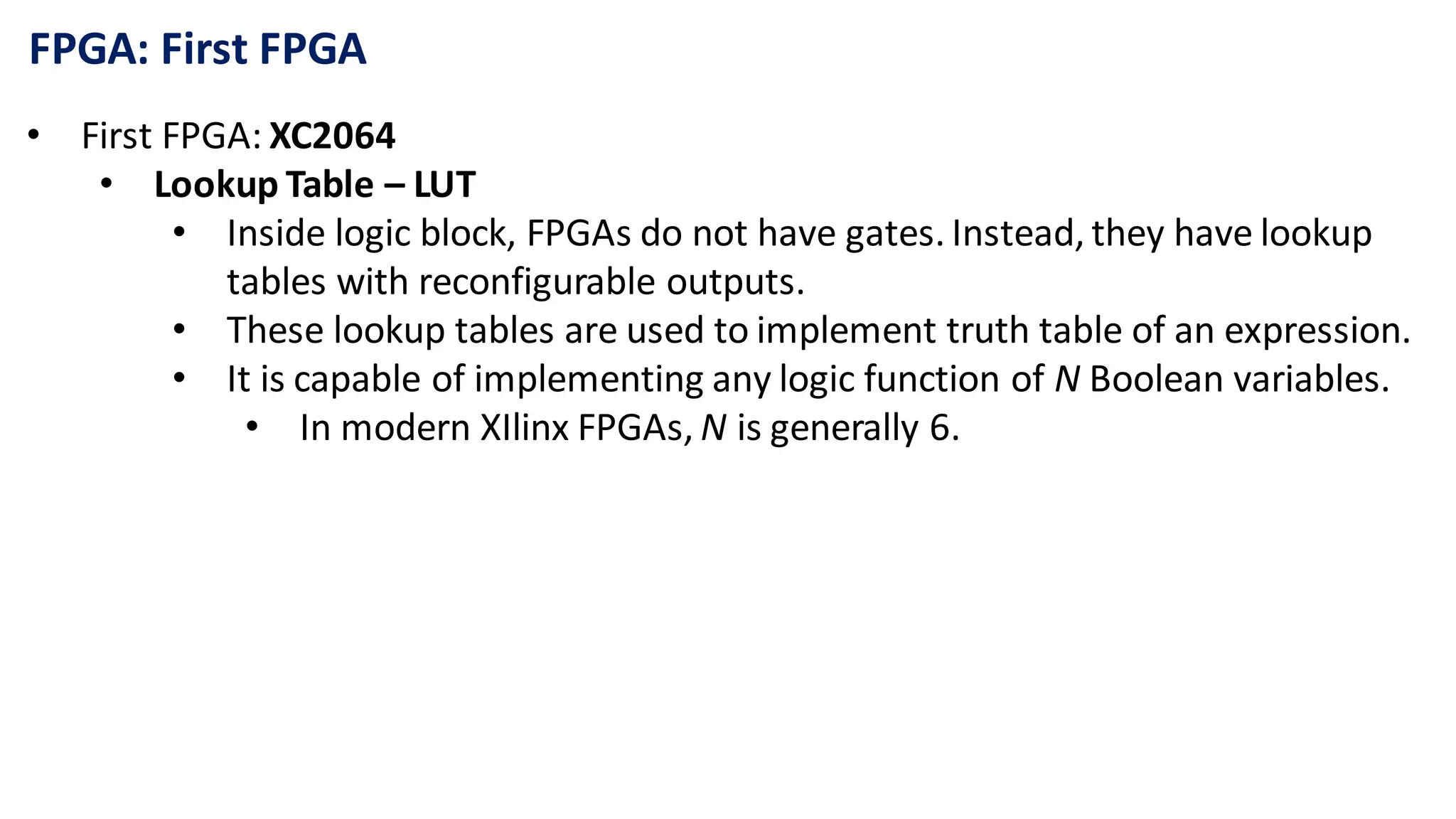

![FPGA: First FPGA

• First FPGA: XC2064

• The interconnects

• There are several horizontal and vertical line segments.

• Interconnect points allow connections to be made between a horizontal

line and a vertical line, allowing arbitrary paths to be created.

• Switch matrices

Images are retrieved from [https://semiwiki.com/fpga/290990-reverse-engineering-the-first-fpga-chip-xilinx-xc2064/]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-13-2048.jpg)

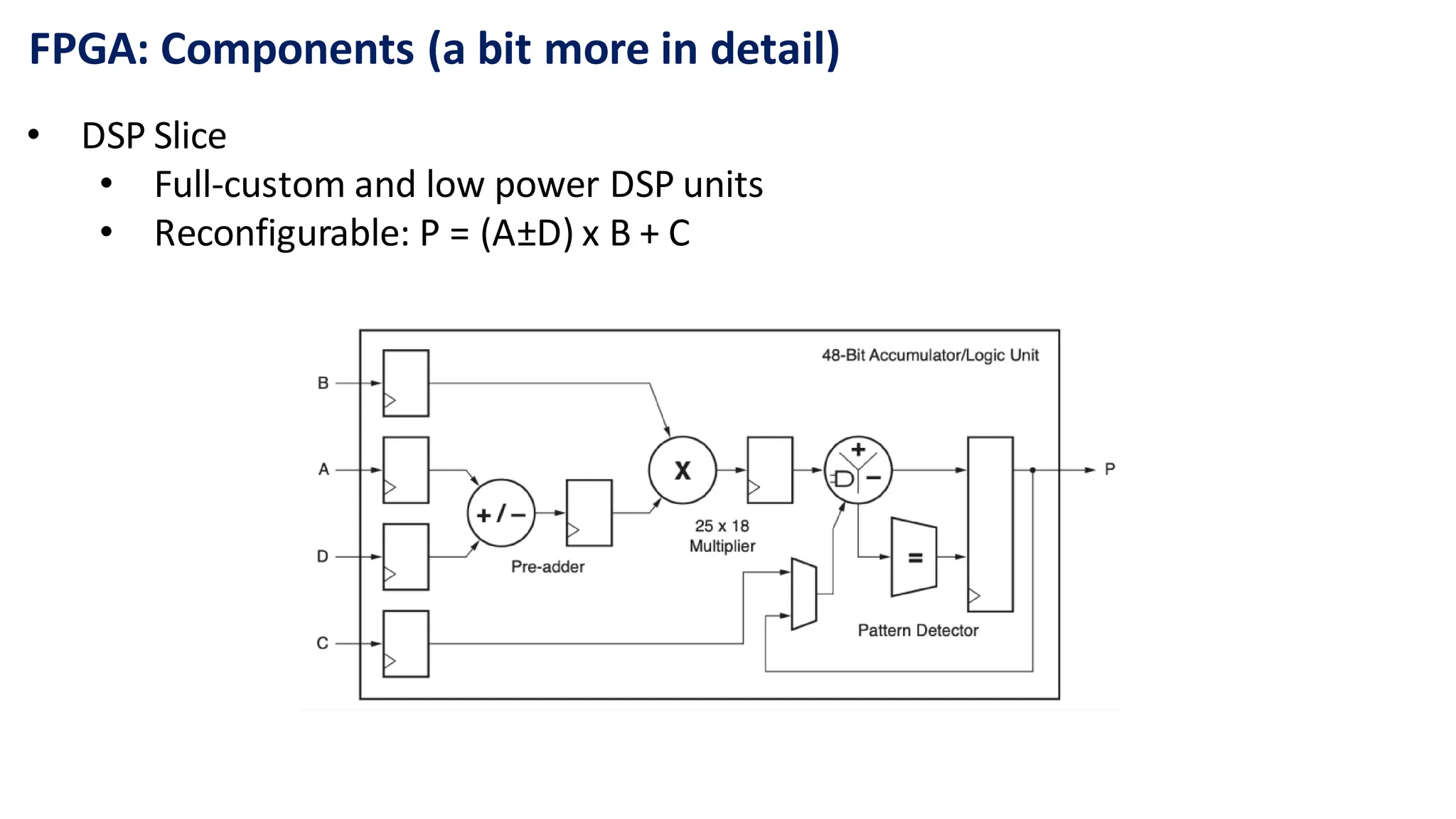

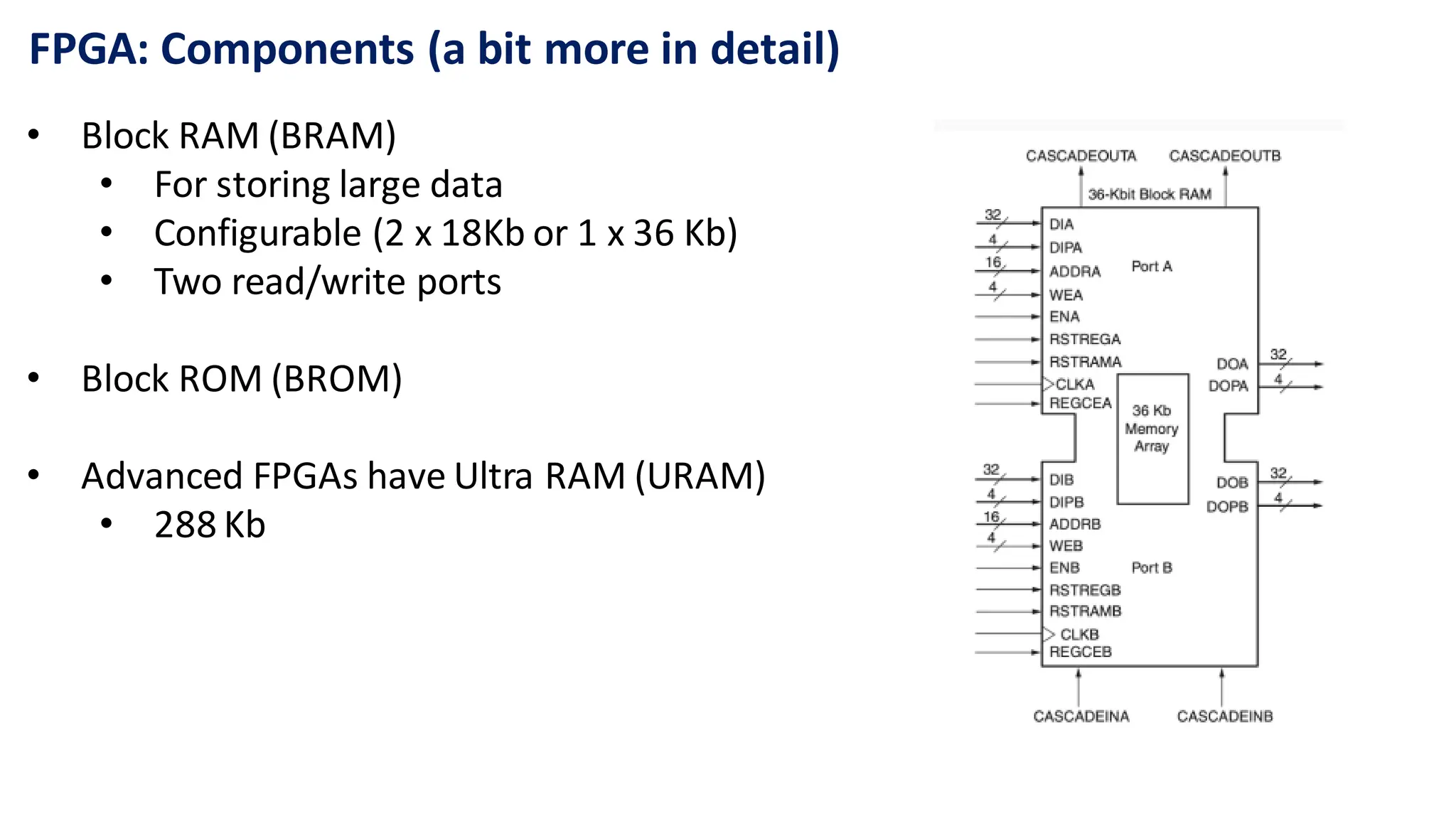

![FPGA: Components (a bit more in detail)

• FPGA: Field Programmable Gate Arrays

• ConfigurableLogic Blocks (CLBs)

• Programmable Interconnects

• Programmable I/O blocks

• Other functionalblocks: DSPs, Block RAMs, Ultra RAMs, ...

Image is retrieved from [https://towardsdatascience.com/introduction-to-fpga-and-its-architecture-20a62c14421c]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-30-2048.jpg)

![FPGA: Components (a bit more in detail)

• 7-series overview (Artix-7)

• Modern FPGAs have diverse resources

Image is retrieved from [https://xilinx.eetrend.com/files-eetrend-xilinx/forum/201509/9204-20390-7_series_architecture_overview.pdf]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-32-2048.jpg)

![FPGA: Components (a bit more in detail)

• Configurable Logic Block (CLB)

• Has 2 slices

• SLICEM (LUT can be used for logic and memory)

• SLICEL (LUT can be used only for logic)

• Connected to interconnect through switch matrix

Image is retrieved from [https://xilinx.eetrend.com/files-eetrend-xilinx/forum/201509/9204-20390-7_series_architecture_overview.pdf]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-33-2048.jpg)

![FPGA: Components (a bit more in detail)

• CLB Slices

• Four 6-input LUTs

• D-FFs

• Multiplexers

Image is retrieved from [https://xilinx.eetrend.com/files-eetrend-xilinx/forum/201509/9204-20390-7_series_architecture_overview.pdf]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-34-2048.jpg)

![FPGA: Components (a bit more in detail)

• CLB Slices

• Four 6-input LUTs

• D-FFs

• Multiplexers

Image is retrieved from [https://xilinx.eetrend.com/files-eetrend-xilinx/forum/201509/9204-20390-7_series_architecture_overview.pdf]](https://image.slidesharecdn.com/01fpga-240423002401-ef27073b/75/Field-programmable-Gate-Arrays-Chapter-6-pdf-35-2048.jpg)