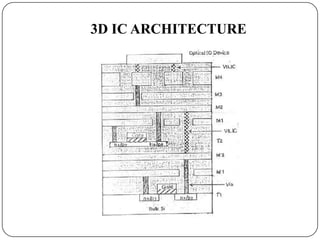

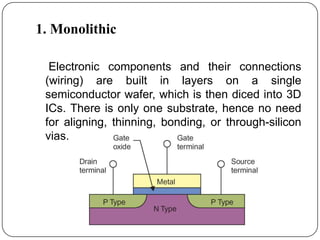

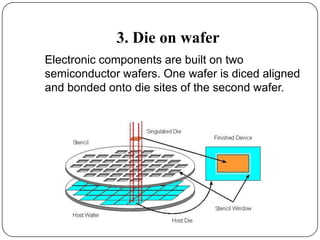

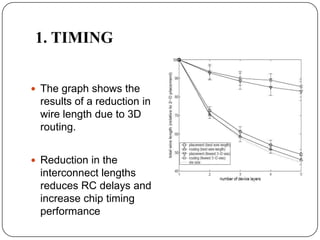

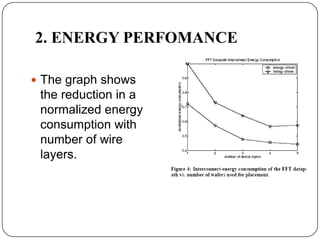

The document presents information on 3D integrated circuits (3D ICs). It discusses the idea for 3D ICs to reduce delays and power consumption compared to 2D chips. It describes 3D IC architecture as stacking layers of active components vertically and horizontally. The manufacturing technologies for 3D ICs include monolithic, wafer on wafer, die on wafer, and die on die approaches. Advantages of 3D ICs include reduced wiring, capacitances, power dissipation, and improved performance. Concerns include thermal and reliability issues. Research is ongoing to introduce cheaper 3D ICs for applications like memory.