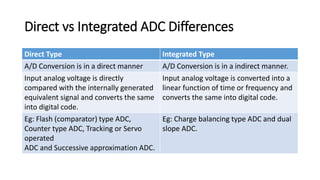

Direct ADCs directly compare the input analog voltage to an internally generated reference voltage and output a digital code. Integrated ADCs first convert the input voltage into a linear function of time or frequency before outputting a digital code.

A flash ADC is a direct ADC that uses parallel comparators to simultaneously compare the input voltage to different reference levels and output a digital code in a single step. However, it requires an exponentially increasing number of comparators for higher resolution.

A dual-slope ADC is an integrated ADC that uses an integrator to convert the input voltage into a linear ramp over time. It then integrates a reference voltage into a ramp of the opposite polarity until the two ramps cancel out, at which point