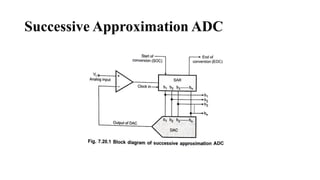

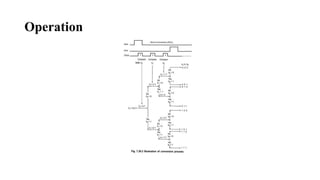

The document discusses successive approximation analog-to-digital conversion (ADC). It operates by using a binary search strategy to iteratively adjust the output of a digital-to-analog converter (DAC) until it approximates the input voltage within half a least significant bit. Over the course of n clock cycles, where n is the resolution in bits, the successive approximation register determines the n-bit digital code representing the input voltage. The conversion time is equal to the clock period multiplied by the number of bits plus one clock cycle to reset the register before the next conversion.