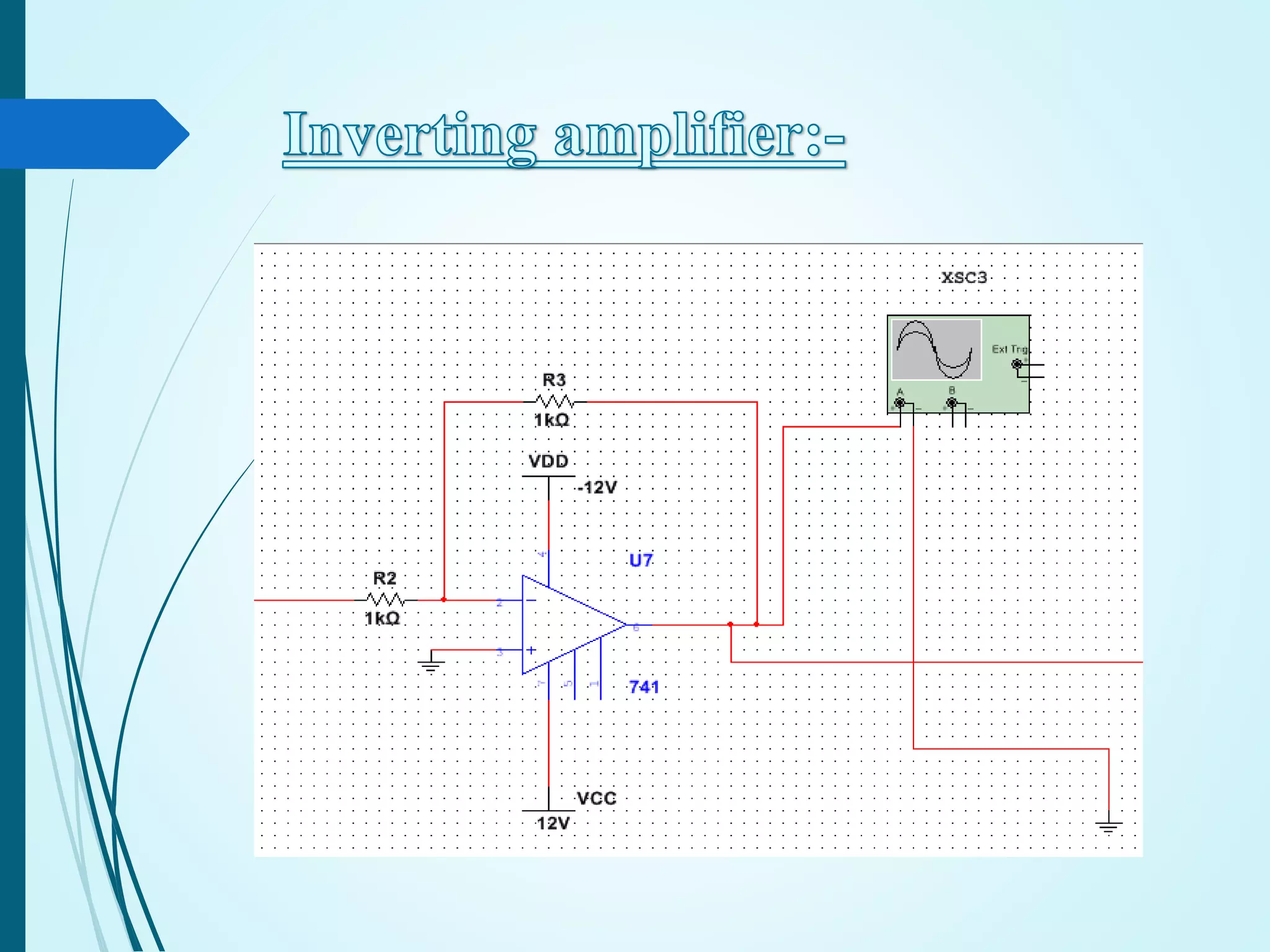

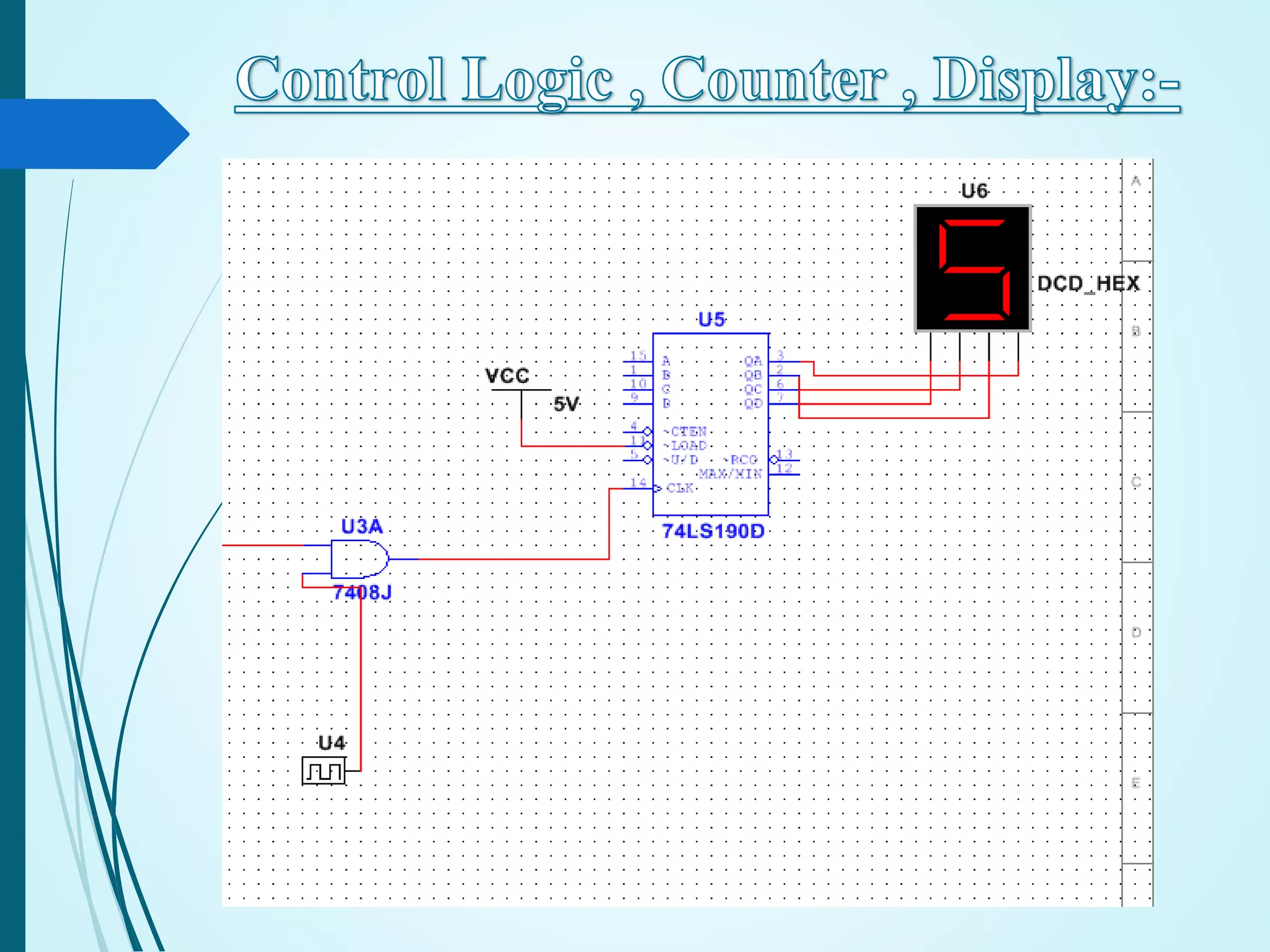

The document discusses the design and implementation of an analog to digital converter using a single slope ADC technique. It details the components involved, including the integrator, sample and hold circuit, comparator, and the process by which the counter outputs the digital representation of the analog voltage. It highlights the applications, advantages, and disadvantages of this method, noting its use in high-resolution and low-cost applications, while also mentioning performance characteristics like resolution and conversion speed.