Embed presentation

Downloaded 255 times

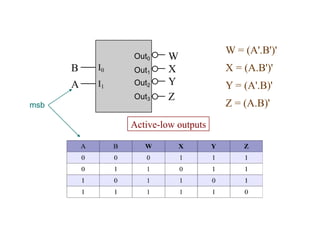

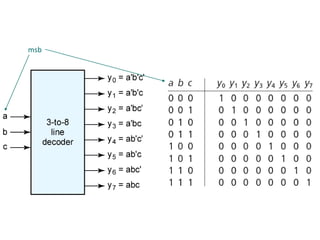

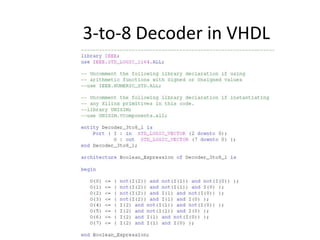

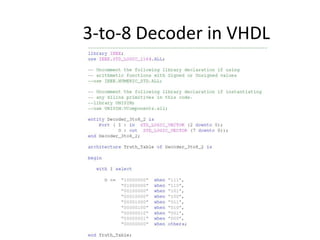

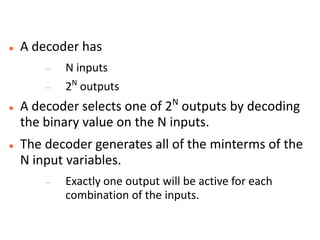

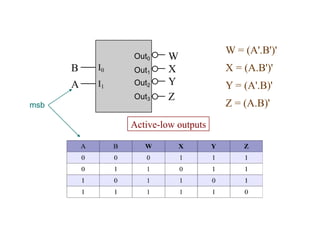

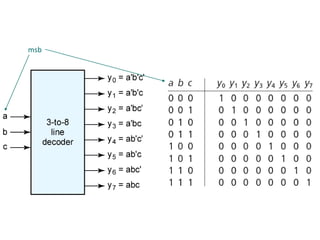

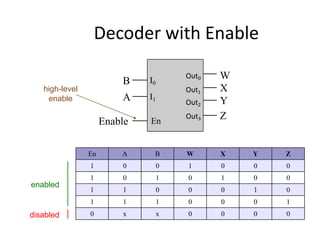

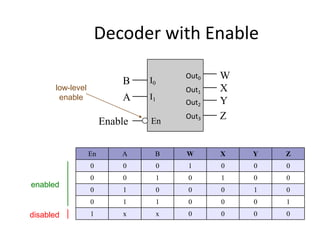

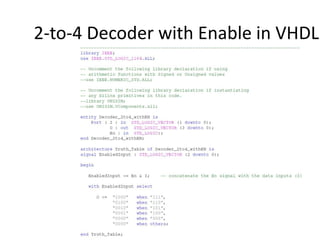

A decoder is a digital circuit that takes binary inputs and selects one of multiple outputs. It has N inputs and 2N outputs. The decoder decodes the binary value on its N inputs and activates exactly one output corresponding to that input combination. Decoders generate all possible combinations or "minterms" of the input variables.