Embed presentation

Downloaded 133 times

![CPU Architecture -

Advanced

Yong Heui Cho @ Mokwon University

Some of slides are referred to:

[1] 3.3 Computer Architectures, slideshare.](https://image.slidesharecdn.com/7-151023062119-lva1-app6892/85/CPU-Architecture-Advanced-1-320.jpg)

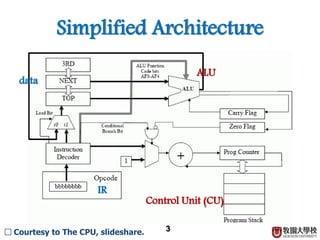

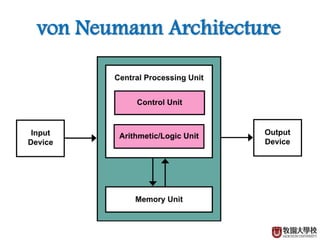

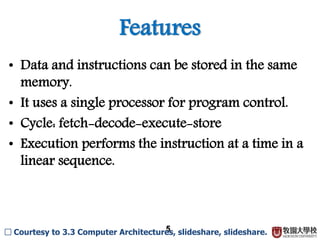

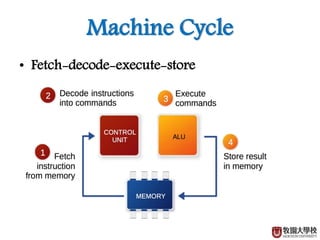

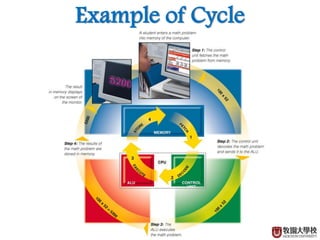

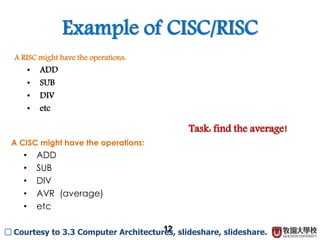

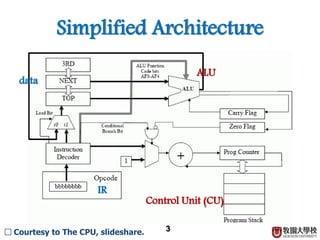

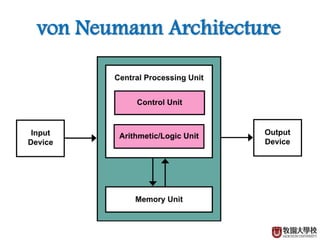

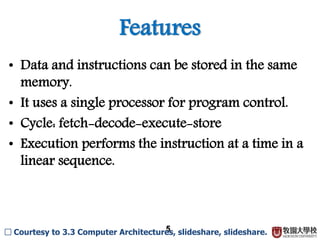

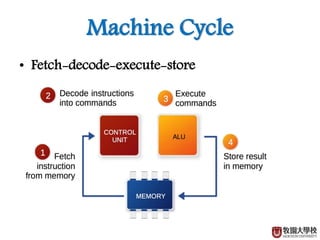

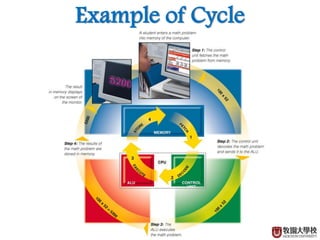

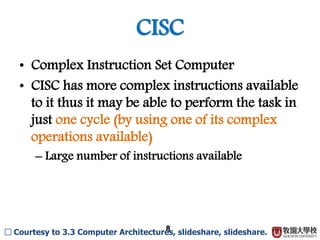

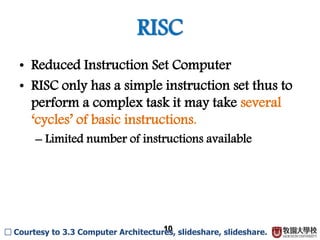

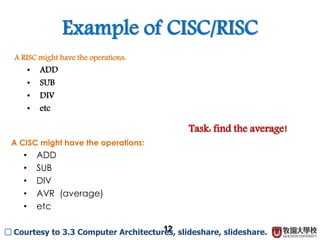

The document discusses advanced CPU architecture. It describes the von Neumann architecture which uses a single processor for program control and follows a fetch-decode-execute-store cycle to process instructions one at a time in a linear sequence from memory. It also describes the differences between CISC (Complex Instruction Set Computer) and RISC (Reduced Instruction Set Computer), with CISC having more complex instructions that can perform tasks in one cycle while RISC uses simpler instructions that may require multiple cycles to complete complex tasks. An example is provided to illustrate how a RISC would take more cycles than a CISC to compute an average.

![CPU Architecture -

Advanced

Yong Heui Cho @ Mokwon University

Some of slides are referred to:

[1] 3.3 Computer Architectures, slideshare.](https://image.slidesharecdn.com/7-151023062119-lva1-app6892/85/CPU-Architecture-Advanced-1-320.jpg)