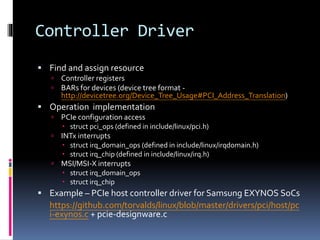

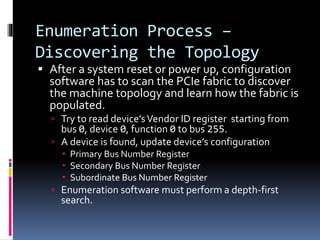

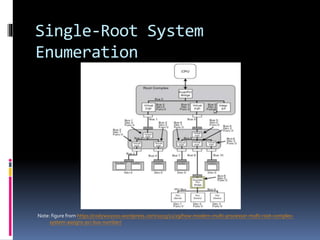

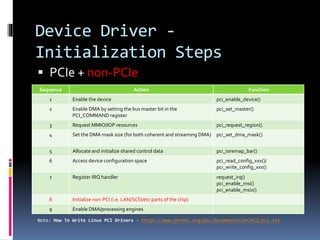

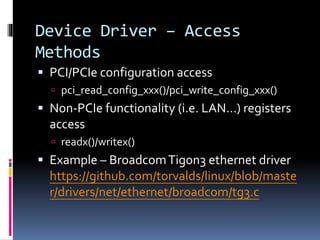

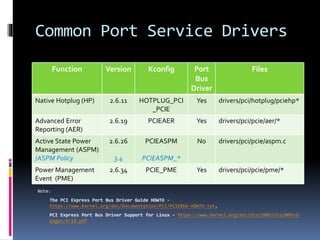

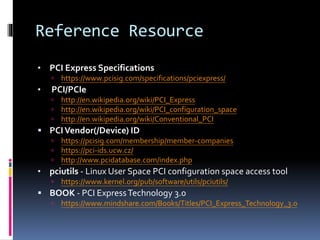

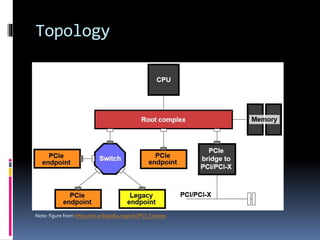

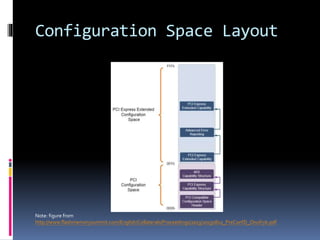

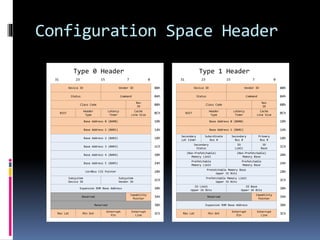

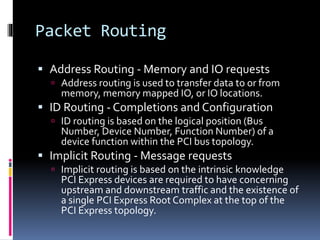

This document provides an overview of Linux PCI Express drivers, including PCIe topology, configuration space, driver initialization, and common port service drivers. It describes the PCIe standard for replacing older PCI standards and how PCIe preserves backward compatibility at the software level. It also outlines the device enumeration process, driver access methods, and reference resources for PCIe specifications and Linux PCIe documentation.

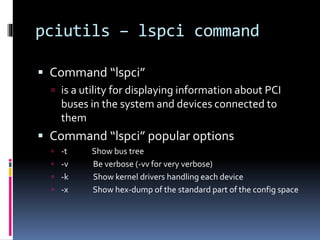

![pciutils – lspci example

lspci -vkx

02:00.0 Ethernet controller: Broadcom Corporation NetXtreme BCM5720 Gigabit

Ethernet PCIe

Subsystem: Broadcom Corporation Device 2003

Flags: bus master, fast devsel, latency 0, IRQ 16

Memory at f0050000 (64-bit, prefetchable) [size=64K]

Memory at f0040000 (64-bit, prefetchable) [size=64K]

Memory at f0030000 (64-bit, prefetchable) [size=64K]

Expansion ROM at f7c40000 [disabled] [size=256K]

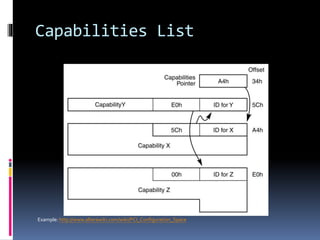

Capabilities: [48] Power Management version 3

Capabilities: [50] Vital Product Data

Capabilities: [58] MSI: Enable- Count=1/8 Maskable- 64bit+

Capabilities: [a0] MSI-X: Enable- Count=17 Masked-

Capabilities: [ac] Express Endpoint, MSI 00

Capabilities: [100] Advanced Error Reporting

Capabilities: [13c] Device Serial Number 00-00-00-0a-f7-82-bf-82

Capabilities: [150] Power Budgeting <?>

Capabilities: [160] Virtual Channel

Kernel driver in use: tg3

00: e4 14 5f 16 06 00 10 00 00 00 00 02 10 00 80 00

10: 0c 00 05 f0 00 00 00 00 0c 00 04 f0 00 00 00 00

20: 0c 00 03 f0 00 00 00 00 00 00 00 00 e4 14 03 20

30: 00 00 c4 f7 48 00 00 00 00 00 00 00 0b 01 00 00](https://image.slidesharecdn.com/slideshare-pcie-151225103853/85/Slideshare-PCIe-13-320.jpg)