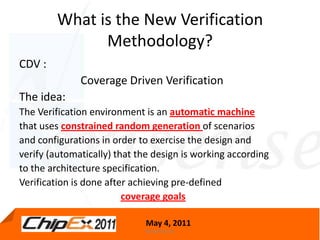

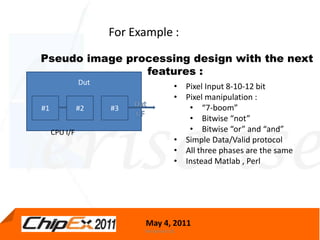

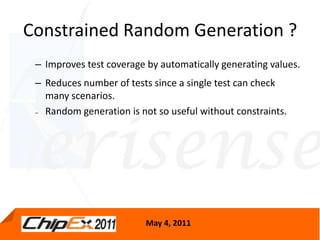

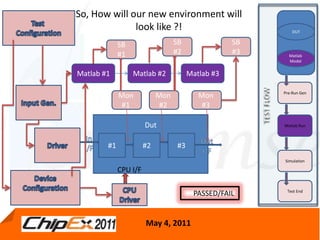

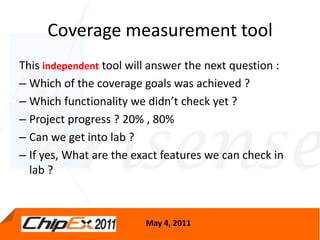

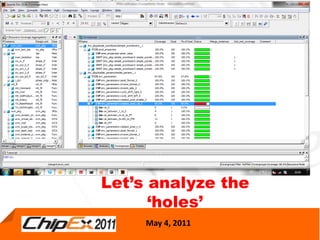

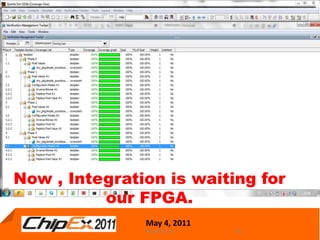

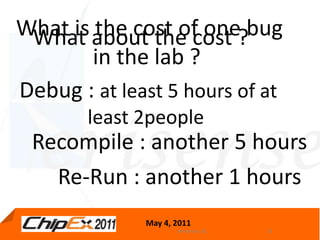

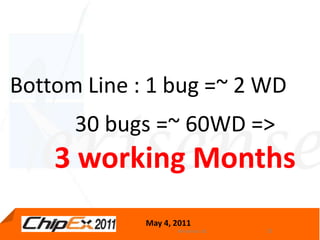

The document discusses the need for advanced verification in FPGA-based logic design. It argues that FPGAs have similar complexity issues as ASICs for high-quality applications. While FPGAs allow for reprogramming, current FPGA verification relies on manual testing and debugging which has long cycle times and lacks visibility into test quality. The document proposes a new coverage-driven verification methodology using constrained random testing to improve productivity, quality, and certification. It demonstrates this methodology and discusses how it can find more bugs than manual testing while being less expensive.