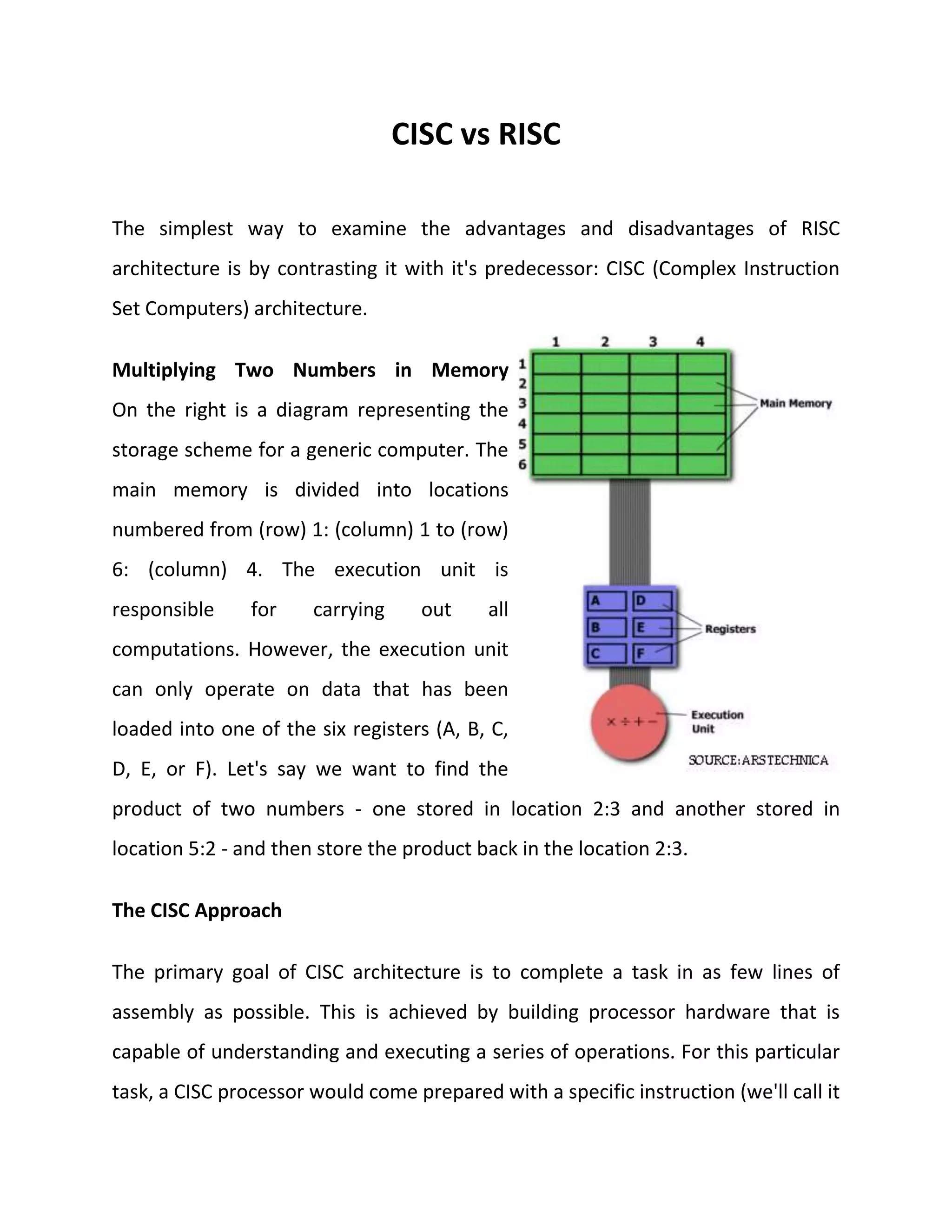

RISC and CISC architectures take different approaches to processing instructions. CISC emphasizes fewer instructions by incorporating complex operations like "MULT" that perform multiplication in one instruction. RISC breaks operations into simpler load, operate, store instructions that each take one clock cycle, requiring more instructions but allowing for faster parallel processing. While CISC code is more compact, RISC reduces processing time at the cost of larger code size.