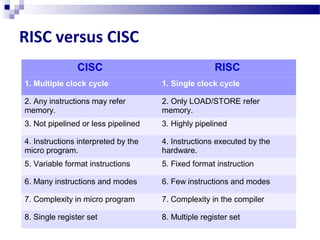

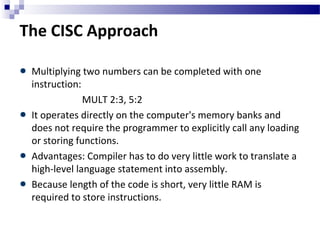

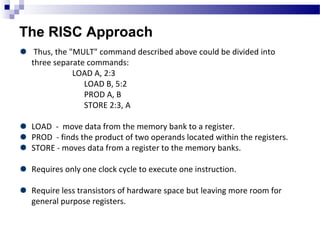

This document discusses RISC processors and compares them to CISC processors. It covers the history of RISC, including the development of RISC concepts in the 1970s. The key differences between RISC and CISC are that RISC uses fixed-length instructions that perform in one clock cycle, while CISC has variable-length instructions that may take multiple cycles. The document also outlines RISC design principles like simple instructions, register-to-register operations, and large register sets. Examples of popular RISC architectures like MIPS, SPARC, and ARM are provided.