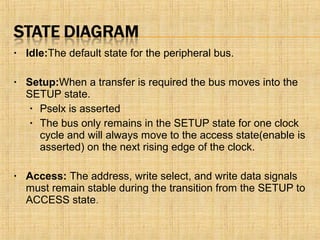

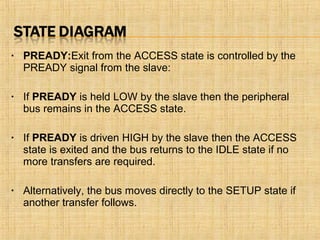

This document discusses the Advanced Peripheral Bus (APB) which is part of the Advanced Microcontroller Bus Architecture (AMBA). It provides three key points:

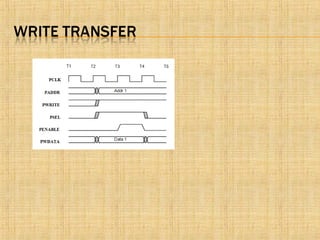

1. The APB is optimized for low power consumption and reduced complexity by interfacing with low bandwidth peripherals. It uses a single clock edge to simplify timing analysis.

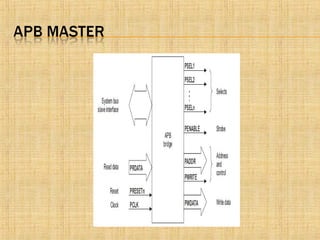

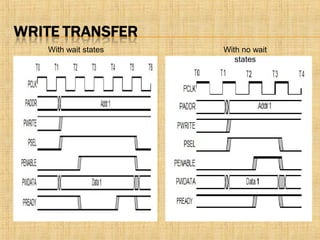

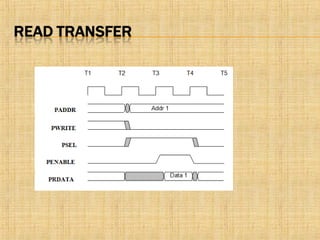

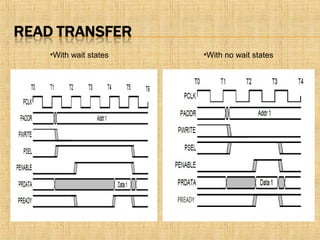

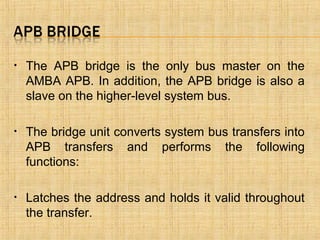

2. The APB bridge acts as the bus master, latching the address and controlling data transfer direction. It generates control signals to select the peripheral and indicate the transfer type (read/write).

3. APB peripherals use a simple interface, latching write data on the clock edge or enable signal. Reads return data when the peripheral is selected and transfer is

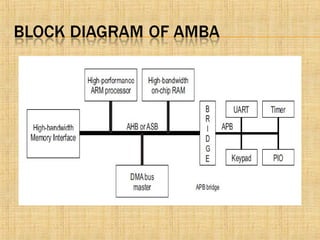

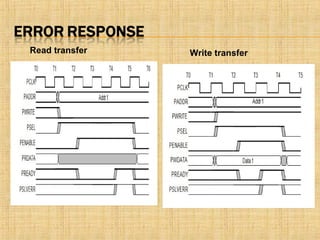

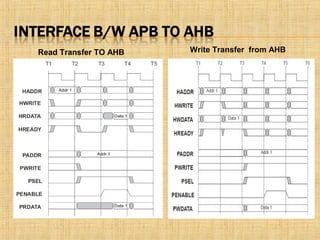

![• From AHB to APB PSLVERR is mapped back to

HRESP[1:0] = ERROR for both reads and writes. This is

achieved by mapping PSLVERR to the AHB signal

HRESP[1:0].

• HRESP[1:0]:OKAY,ERROR,RETRY,SRLIT.](https://image.slidesharecdn.com/baa43515-6df9-4523-8ff6-43640077c493-150127044529-conversion-gate01/85/AMBA_APB_pst-23-320.jpg)