This paper discusses the design and verification of an IP core bridge for interfacing the AMBA AXI-Lite and APB buses, aimed at enhancing communication between different frequency operating buses in System-on-Chip (SoC) systems. The proposed APB bridge operates at a maximum frequency of 168.464 MHz, converting read and write operations from the AXI bus to the APB bus. The document details the design methodology, features of AMBA 4.0, and includes simulation results confirming the functionality of the bridge module.

![Short Paper

Proc. of Int. Conf. on Control, Communication and Power Engineering 2013

Design and Analysis of Xilinx Verified AMBA Bridge

for SoC Systems

Shaila S Math1, Veerabhadrayya Math2

1

BMS Institute of Technology, Department of Electronics and Communication Engineering, Bangalore, India

Email: shaila.s.math@gmail.com

2

Srinivas School of Engineering, Department of Electronics and Communication Engineering, Mangalore, India

Email: veerabhadrayya.math@ymail.com

Abstract: ARM introduced the Advanced Microcontroller Bus

Architecture (AMBA) 4.0 and its specifications define five

buses/interfaces: Advanced eXtensible Interface Bus (AXI),

Advanced High-performance Bus (AHB), Advanced System Bus

(ASB), Advanced Peripheral Bus (APB) and Advanced Trace

Bus (ATB). That means more and more existing Intellectual

Property (IP) must be able to communicate with AMBA4.0

bus. This paper presents an IP core design of APB Bridge, to

provide interface between AXI-Lite bus and APB bus operating

at different frequencies. The maximum operating frequency

of the module is 168.464MHz. Test cases are run to perform

multiple read and write operations. Synthesis and Simulation

is done using Xilinx ISE and Modelsim.

Index Terms: AMBA, AXI, IP, Xilinx

Figure 1. System On-chip Interconnect showing AMBA/

CoreConnect/ Wishbone Buses

I. INTRODUCTION

The AMBA data bus width can be 32, 64, 128 or 256 byte,

address bus width will be 32bits wide. The AMBA AXI4 [5]

specification to interconnect different modules in a SoC was

released in March 2010. The key features of AMBA4 including its all versions (AXI4 and AXI4-Lite) are discussed in

detail in [5]. Few key features used in designing the modules

are discussed here.

In recent years due to the miniaturization of

semiconductor process technology and computation for

survival in the current market conditions constant

customization is required. The semiconductor process

technology is changing at a faster pace during 1971

semiconductor process technology was 10µm [1], during 2010

the technology is reduced to 32nm and future is promising

for a process technology with 10nm. Intel, Toshiba and

Samsung have reported that the process technology would

be further reduced to 10nm in the future. So with decreasing

process technology and increasing consumer design

constraints System-on-Chip (SoC) has evolved, where all the

functional units of a system are modeled on a single chip.

SoC buses are used to interconnect an Intellectual

Property (IP) core to the surrounding interface. These are

not real buses, but they reside in Field Programmable Gate

Array (FPGA). Each bus/interface have different features,

the designer chooses the bus, best suited for his application.

Some challenges faced in SoC buses are latency, high

bandwidth, arbitration schemes, number of masters and slaves

connected on bus and performance of bus according to

different application. Fig. 1 shows the exact picture where

the SoC buses reside in a chip. Masters can be Central

Processing Unit (CPU), Moving Picture Expert Group (MPEG),

where as slaves can be memory, Arithmetic and Logical Unit

(ALU) etc. Currently there are a few publicly available systemon-chip buses such as AMBA from ARM [2], Core Connect

from IBM [3], Wishbone from Silicore [4] and others. The

number of masters and slaves depends on application.

© 2013 ACEEE

DOI: 03.LSCS.2013.2.535

A. AMBA AXI4

Features of AXI4 includes the following:

• Burst lengths up to 256 beats is supported

• Quality of Service (QoS) signaling

• Multiple region interface is supported

• Write response requirements are updated

• Update of AWCACHE and ARCACHE signaling details

• For ordering requirements additional information is provided

• Optional User signaling details

• Locked transactions and write interleaving are removed

B. AMBA AXI4-Lite

Features of AXI4-Lite interface are:

• All transactions burst length is 1

• All data access size is same as width of data bus

• Supports 32-bit or 64-bit data bus width

• All accesses are equivalent to AWCACHE or ARCACHE

equal to b0000

• For exclusive accesses support is not provided.

C. AMBA APB

The APB bus is optimized for minimal power consumption

and reduced interface complexity. The APB peripherals can

32](https://image.slidesharecdn.com/535-140217021803-phpapp02/85/Design-and-Analysis-of-Xilinx-Verified-AMBA-Bridge-for-SoC-Systems-1-320.jpg)

![Short Paper

Proc. of Int. Conf. on Control, Communication and Power Engineering 2013

TABLE 1: SIGNAL D ESCRIPTIONS

be integrated easily to any design flow, with the following

advantages:

• High-frequency operation can be easily achieved

• Use of a single clock edge to simplify the static timing

analysis

• No special considerations are required for automatic test

insertion

• Many Application Specific Integrated Circuit (ASIC) libraries

have a better selection of rising edge registers

• Easy integration with cycle-based simulators.

AMBA B RIDGE

Signal

Input/

Output

Global

Input

AResetn

AWADDR

WSTRB

Global

Master

Master

Input

Input

Input

AWPROT

Master

Input

WDATA

ARADDR

Master

Master

Input

Input

ARPROT

Master

Input

RDATA

Master

Input

AWVALID

Master

Output

AWREADY

Slave

Output

WVALID

ARVALID

RVALID

WREADY

BRESP

RRESP

Master

Slave

Slave

Slave

Slave

Slave

Output

Output

Output

Output

Output

Output

BVALID

Slave

Output

BREADY

RREADY

Master

Master

Output

Output

ARREADY

Slave

Output

PCLK

Global

Input

PRESETn

All five channels of AMBA use the same VALID/READY

handshake to transfer data and control information. Both

master and slave are controlled by this two way mechanism.

When the data or control information is available on the

source it generates VALID signal. The destination generates

the READY signal to indicate that it accepts the data or

control information. When both the VALID and READY

signals are HIGH transfers will occur. On both master and

slave interfaces there must be no combinatorial paths between

input and output signals. Table 1 gives the information of

signals used in the complete design of the module.

Fig. 2 to Fig. 4 show examples of the handshake sequence.

In Fig. 2, the source drives the VALID signal HIGH when it

gets data or control information. The destination drives

READY signal HIGH if it is ready to accept the data or

information sent by the source. The arrow shows when the

transfer occurs. It is not permitted to wait until READY is

asserted before asserting VALID. Once VALID is asserted it

must remain asserted until the handshake occurs.

Source:

master/

slave/APB

Bridge

Aclk

D. Handshake Mechanisms of AXI-Lite and APB

Global

APB

bridge

APB

bridge

APB

bridge

APB

bridge

Input

Global clock

signal.

Global reset signal

Write address

Write burst type

Write protection

type

Write data

Read address

Read Protection

type

Read data

Write address

valid

Write address

ready

Write valid

Read address valid

Read valid

Write ready

Write response.

Read response.

Write response

valid.

Response ready.

Master ready.

Read address

ready.

Global clock

signal

Global reset signal

Input

APB address bus

Input

Protection type

PADDR

PPROT

PSELx

PENABLE

PWRITE

Figure 2. VALID before READY handshake

PWDATA

In Fig. 3, before the data or control information is valid,

destination drives READY HIGH. The data or control

information is accepted in a single cycle, as soon as it becomes

valid. The arrow shows when the transfer occurs. It is

permitted to wait for VALID to be asserted before the

corresponding READY is asserted. If READY is asserted, it

is permitted to de assert READY before VALID is asserted.

In Fig. 4, both the source and destination drives READY

and VALID signal at the same cycle. Here the transfer can be

data or control information. In this case the transfer occurs

immediately. The arrow shows when the transfer occurs.

In this paper interfacing bridge of AXI4-Lite and APB [6]

is designed and verified. Here we used Verilog HDL [7] (Hardware Description Language) for designing the RTL (Register

Transfer Level) code. Synthesis and Simulation is done using Xilinx ISE and Modelsim [8]. The rest of the paper is

organized as follows: Section 2 discusses related work. Sec

© 2013 ACEEE

DOI: 03.LSCS.2013.2.535

OF

PSTRB

PREADY

PRDATA

PSLVERR

Input

Input

APB

bridge

APB

bridge

APB

bridge

Slave

interface

Slave

interface

Slave

interface

Description

Select line for

Slave

Enable signal

indicates the

second and

subsequent cycles

of an APB transfer

Input

Direction

Input

Write data

Input

Write strobes size

Output

Response ready

Input

Read data

Output

Transfer failure

Figure 3. READY before VALID handshake

33](https://image.slidesharecdn.com/535-140217021803-phpapp02/85/Design-and-Analysis-of-Xilinx-Verified-AMBA-Bridge-for-SoC-Systems-2-320.jpg)

![Short Paper

Proc. of Int. Conf. on Control, Communication and Power Engineering 2013

Lite of the AMBA on the simulator Riviera was discussed in

[24]. IP solutions for AMBA interconnect was discussed in

[25].

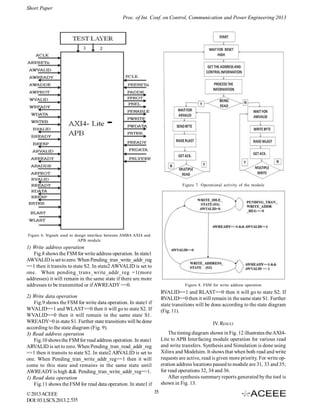

III. PROPOSED WORK

In this work an IP core of APB bridge is designed to provide interface between AXI-Lite bus and APB bus operating

at different frequencies. The maximum operating frequency

of the module is 168.464MHz. The APB bridge provides an

interface between the high-performance AXI domain and the

low-power APB domain. It appears as a slave on AXI bus but

as a master on APB that can access up to sixteen slave peripherals. Read and write transfers on the AXI bus are converted into corresponding transfers on the APB. The AXI4Lite to APB Interfacing module block diagram is shown in

Fig. 5. The test layer shown in the Fig. 5 tests the module for

multiple read and write operations.

Figure 4. VALID with READY handshake

tion 3 of this paper, discusses proposed work. In Section 4,

simulation parameters and results are discussed. Future scope

and concluding remarks are given in Section 5.

II. RELATED WORK

Milica Miti and et al gives the survey of various buses

On-Chip Buses [9]. Computer architecture [10] defines the

physical structure of the CA. Types of computer architecture

are single shared bus, hierarchical bus, token ring bus,

crossbar bus or custom networks. Protocols are defined for

communication channels/buses. Each bus/interface have

different features, the designer chooses the bus, best suited

for his application. Various on-chip bridging techniques in

short are discussed in this section.

AMBA’s design methodology and set of specifications

that will aid designers in making detailed comparisons with

other buses was discussed in detail in [11].

Designing AHB/PCI bridge was discussed in [12]. Here

function of AHB/PCI bridges to map various control signals

and address spaces from one bus into those of another was

explained in detail.

On-chip communication architectures for reconfigurable

System-on-Chip [13] surveys existing solutions for SoC and

analyses the suitability for SoC application. In [14] multichannel on-chip-bus architectures for system-on-chips were

discussed. An on-chip bus bridge between heterogeneous

buses with different clock frequencies was discussed in [15].

Design and implementation of AXI bus protocol-based on

MPSoC architecture was discussed in [16] which uses Altera

Stratix II EP2S180 Field Programmable Gate Array (FPGA).

An IP core of APB bridge, which translates the AXI4.0-lite

transactions into APB 4.0 transactions was discussed in detail

in [17] and [18].

In [19] the analysis was carried out by simulating a multicore platform with a shared-link AXI backbone running a

video phone application. The performance was evaluated in

terms of bandwidth utilization, average transaction latency

and system task completion time. Design of AHB2APB bridge

simulated using Xilinx and Modelsim was discussed in [20].

AMBA to SoCWire network-on-chip bridge [21] presents an

efficient connection between a SoCWire network and a LEON

processor bus systems. Direct memory access enables the

AHB2SOCW bridge to operate efficiently. Design and

analysis of AMBA AXI4 system for various read and write

operations using VCS tool [22] by Synopsis was discussed

in [23]. The system level modelling of the Advanced AHB© 2013 ACEEE

DOI: 03.LSCS.2013.2.535

Figure 5. Block diagram of AXI4-LITE and APB interface

A. Signal Description

Fig. 6 shows the master and slave component signal

connections. The Interfacing module uses AMBA AXI-Lite

signals and APB signals as described in the AMBA protocol

specification. The read and write operation signals

B. Finite State Machines (FSM)

Fig. 7 shows FSM [26] for operational activities of the

module for read and write operation. When reset signal goes

high the module gets address and data information from test

layer. Either it is read or write operation, the module will wait

for VALID signal.

For read operation the data is read and on reading the last

byte RLAST signal is raised. Acknowledgement signal is

received on end of the operation to master module. If it is a

multiple read operation, than the process is continued or else

new address and data information is received from the test

layer. For write operation the data is written to the destination

location and on writing the last byte WLAST signal is raised.

Acknowledgement signal is received on end of the operation

to master module. If it is a multiple write operation, than the

process is continued or else new address and data information

is received from the test layer.

34](https://image.slidesharecdn.com/535-140217021803-phpapp02/85/Design-and-Analysis-of-Xilinx-Verified-AMBA-Bridge-for-SoC-Systems-3-320.jpg)

![Short Paper

Proc. of Int. Conf. on Control, Communication and Power Engineering 2013

length of 16 beats. These are the drawbacks of AMBA AXI4

system which need to be overcome.

[14] Sanghun Lee, Chanho Lee, Hyuk-Jae Lee, “A new multi-channel

on-chip-bus architecture for system-on-chips,” in Proceedings

of the IEEE International SOC Conference, pp.20-27,

September 2004.

[15] Sangik Choi and Shinwook Kang, Mobile SamsungElectronics

Co.,Ltd, “Implementation of an On-Chip Bus Bridge between

Heterogeneous Buses with Different Clock Frequencies”. IEEE,

IDEAS’05, pp. 530-534, July 2005

[16] Fu-ming Xiao, Dong-sheng Li ; Gao-ming Du ; Yu-kun Song

; Duo-li Zhang ; Ming-lun Gao “Design of AXI bus based

MPSoC on FPGA”3rd IEEE international conference on Anticounterfeiting, Security, and Identification in Communication,

ASID 2009, pp. 560-564, August 2009

[17] Jaehoon Song, Juhee Han ; Dooyoung Kim ; Hyunbean Yi ;

Sungju Park “Design Reuse of on/off-Chip Bus Bridge for

Efficient Test Access to AMBA-based SoC”, 16th Asian Test

Symposium, pp. 193 – 198, October 2007.

[18] Chenghai Ma, Zhijun Liu ; Xiaoyue Ma “Design and

implementation of APB bridge based on AMBA 4.0”,

International Conference on Consumer Electronics,

Communications and Networks (CECNet), pp.193 – 196, April

2011

[19] N.Y.C. Chang, Y.Z. Liao, T.S. Chang, “Analysis of shared-link

AXI” IET Computer Digit. Tech., vol. 3, no. 4, pp. 373–383,

July 2009

[20] Vani.R.M and M.Roopa “Design of AMBA Based AHB2APB

Bridge” IJCSNS International Journal of Computer Science

and Network Security, vol.10 no.11, pp. 14-18, November

2010

[21] H. Michel, F. Bubenhagen, B.Fiethe, H.Michalik,B.Osterloh,

W.Sullivan, A.Wishart, J.Ilstad, S.A.Habinc, “AMBA to

SoCWire network on Chip bridge as a backbone for a Dynamic

Reconfigurable Processing unit” NASA/ESA Conference on

Adaptive Hardware and Systems (AHS), pp.227 – 233 June

2011,

[22] Synopsys, VCS / VCSi User Guide Version 10.3, , Available

at, www.synopsys.com, March 2008

[23] Shaila S Math, Manjula R.B,S S Manvi, P. Kaunds, “Data

transactions on system-on-chip bus using AXI4 protocol” in

Proceedings of the IEEE International Conference on Recent

Advancements in Electrical, Electronics and Control

Engineering (ICONRAEeCE), pp. 423 – 427, Dec 2011

[24] Richa Sinha, Akhilesh Kumar and Archana Kumari Sinha

“Verification analysis of AHB-Lite protocol with coverage”

International Journal of Advances in Engineering & Technology,

Vol. 2, Issue 1, pp. 121-128, Jan 2012

[25] “DesignWare IP solutions for AMBA interconnect” Synopsis

Inc. Available at http://www.synopsys.com/products/

designware/amba_solutions.html,2009

[26] Clifford E. Cummings, “Coding And Scripting Techniques for

FSM Designs with Synthesis-Optimized, Glitch-Free

Outputs,” SNUG (Synopsys Users Group Boston, MA 2000)

Proceedings, September 2000.

B. Conclusion

The APB bridge using Verilog HDL to provide interface

between AXI-Lite bus and APB bus operating at different

frequencies has been designed. APB bridge designed has

got following features: APB master interface and 32-bit slave

interfaces are provided; Clock domains PCLK and ACLK are

completely independent; The designed module supports 16

APB peripherals; READY signal of APB is translated to wait

states on AXI; and AXI gives SLVERR signal if error occurs

on read/write response.

REFERENCES

[1] Chifeng Wang; Wen-Hsiang Hu; Bagherzadeh, N. “A Wireless

Network-on-Chip Design for Multicore Platforms” in

Proceedings of the 19 th IEEE Euromicro International

conference on Parallel, Distributed and Network-Based

Processing (PDP), February 2011, pp.409 – 41

[2] “AMBA specifications V2.0”, ARM. Available at http://

www.arm.com, 1999

[3] “The CoreConnect Bus Architecture”, IBM Microelectronics.

Available at http://www.ibm.com/chips/products/coreconnect

[4] “Wishbone system-on-chip (soc) interconnection architecture

for portable IP cores, revision: B.3,” OPENCORES. Available

at http://cdn.opencores.org/downloads/wbspec_b3.pdf, 2002

[5] “AMBA AXI Protocol Specification” (Rev 2.0), ARM.

Available at http://www.arm.com, 2010

[6] IP AXI to APB Bridge (v1.00a) DS788, LogiCORE, Product

Specification, June 2011

[7] Samir Palnitkar, Verilog HDL: A Guide to Digital Design and

synthesis, 2nd ed, Prentice Hall PTR Publication, 2003

[8] Xilinx ISE Synthesis and Verification Design Guide Available at

www.xilinx.com, 2008

[9] Milica Miti´c and Mile Stoj¡cev., “ An Overview of On-Chip

Buses”, FACTA UNIVERSITATIS, 2006, pp. 405-428

[10] J. Hennessey and D. Patterson, Computer Architecture—A

Quantitative Approach, 2nd ed., Morgan Kaufmann, San

Mateo, Calif., 1996.

[11] Flynn, D. Adv. RISC Machines Ltd., Cambridge, “AMBA:

enabling reusable on-chip designs”, IEEE Micro, Publication,

pp. 20-27, Jul/Aug 1997.

[12] Wang Zhonghai,Ye Yizheng,Wang Jinxing, and Yu Mingyan,

“Designing AHB/PCI Bridge,”in Proceedings of 4 th IEEE

International Conference on ASIC, pp.578-580, October 2001.

[13] A.S. Lee, N.W. Bergmann “On-chip communication

architectures for reconfigurable System-on-Chip” in

Proceedings of 2003 IEEE International Conference on FieldProgrammable Technology (FPT), pp.332-335, December

2003.

© 2013 ACEEE

DOI: 03.LSCS.2013.2.535

37](https://image.slidesharecdn.com/535-140217021803-phpapp02/85/Design-and-Analysis-of-Xilinx-Verified-AMBA-Bridge-for-SoC-Systems-6-320.jpg)