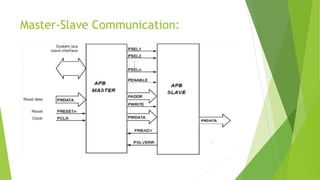

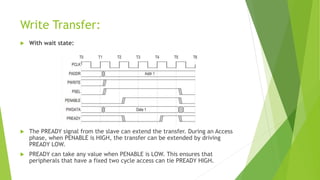

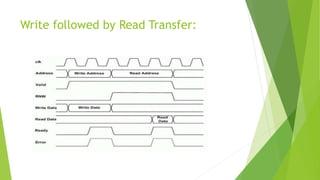

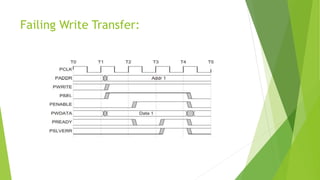

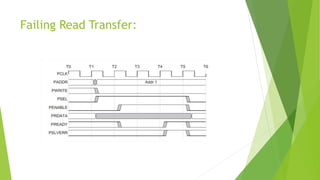

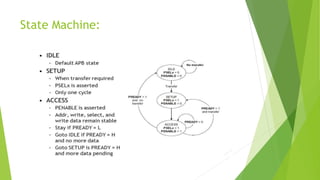

The Advanced Peripheral Bus (APB) is a low-cost, low-power interface defined by ARM for connecting peripherals to processors. It provides an unpipelined bus with signals that only transition on the rising edge of the clock. Peripherals on the APB can extend transfers using the PREADY signal. The APB supports both read and write transfers, and peripherals can indicate transfer errors using the PSLVERR signal.