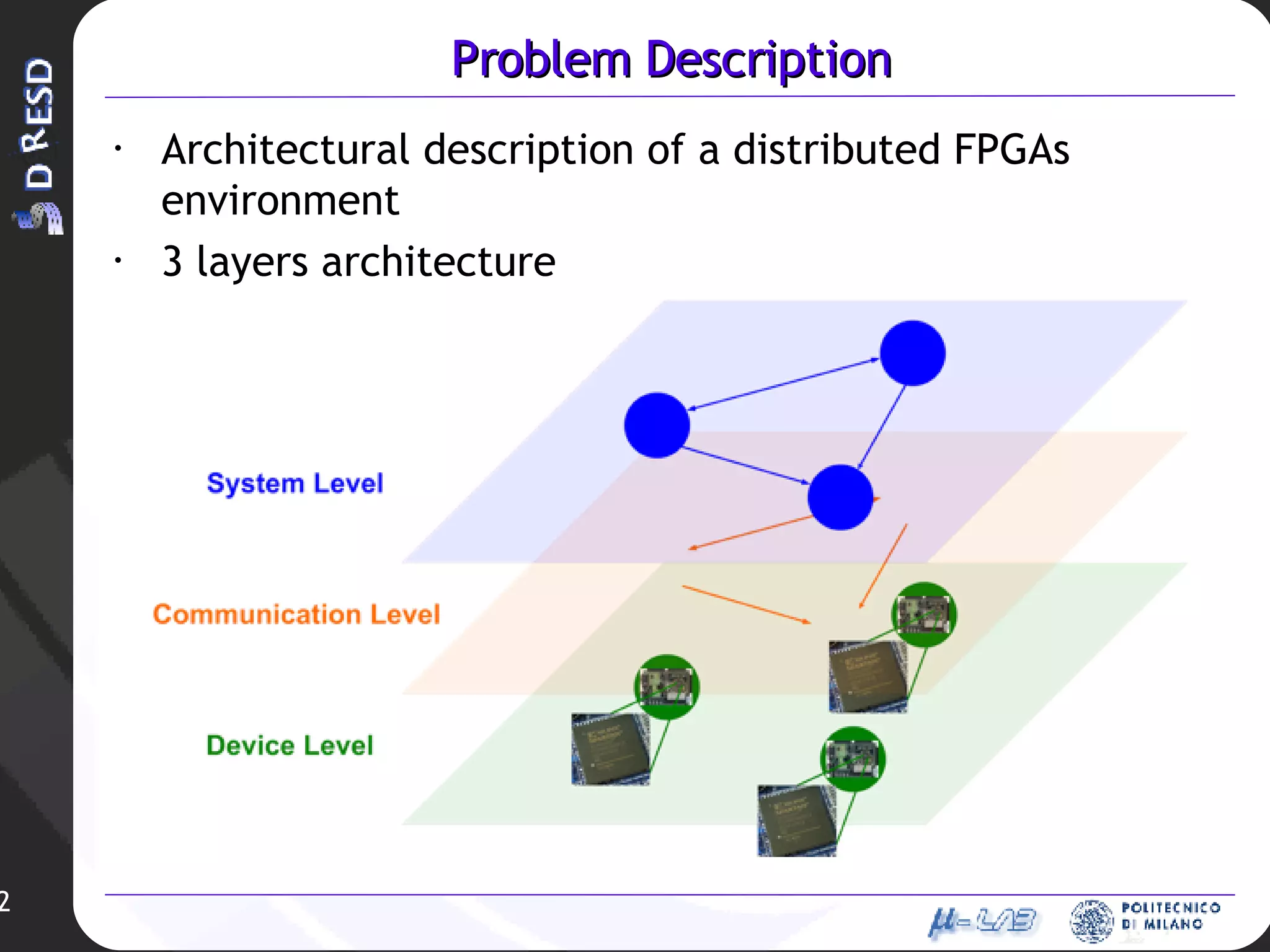

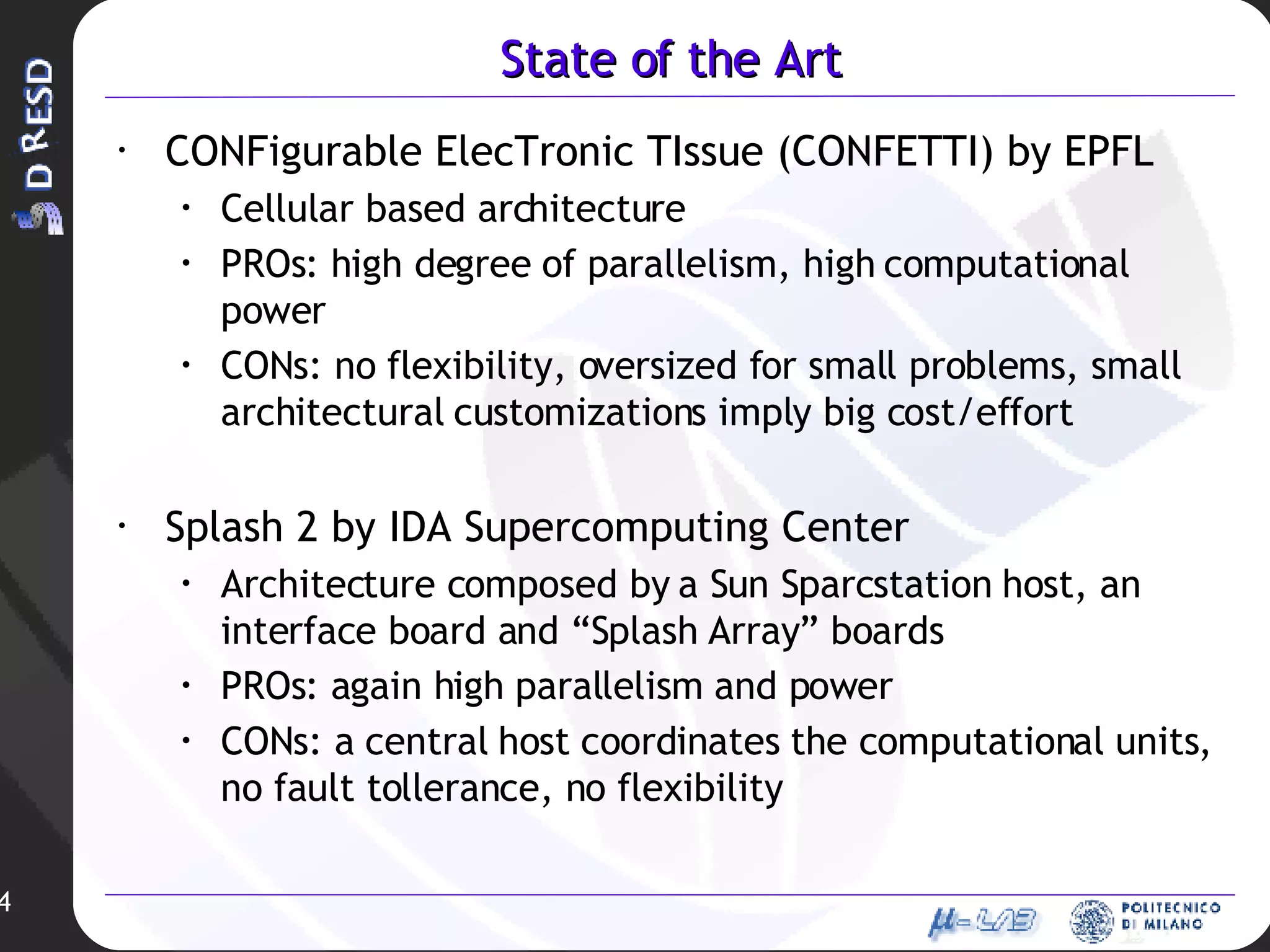

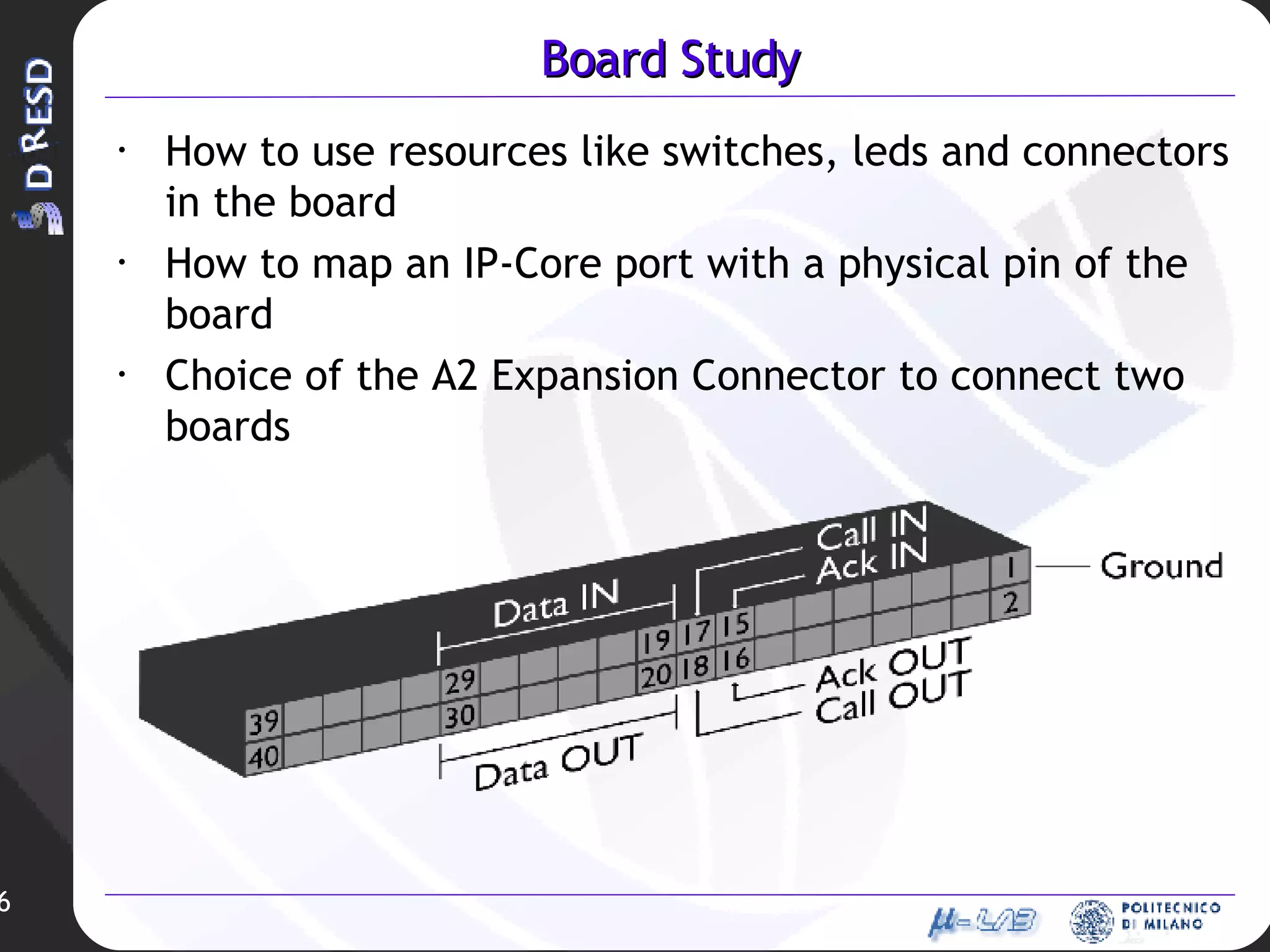

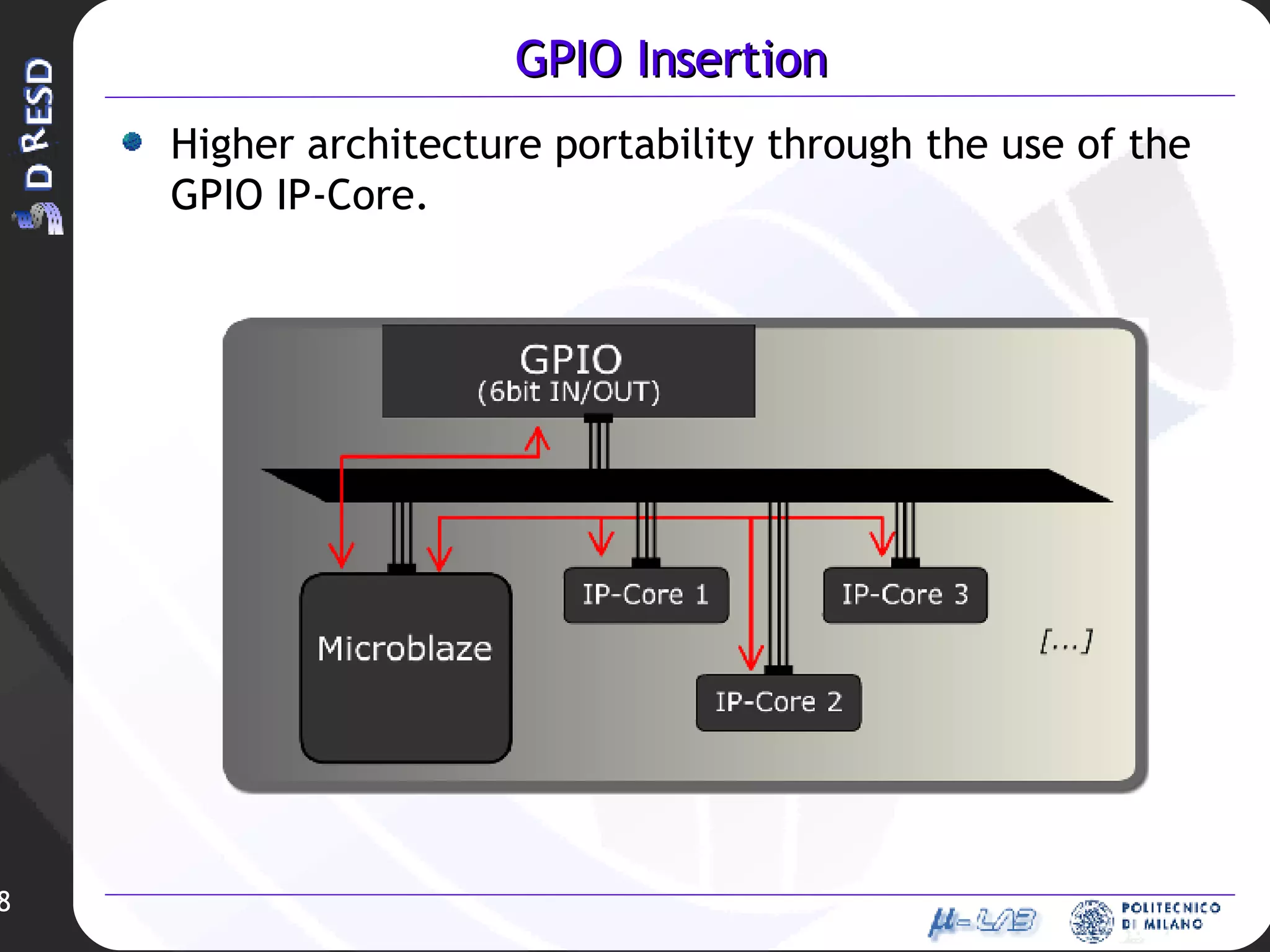

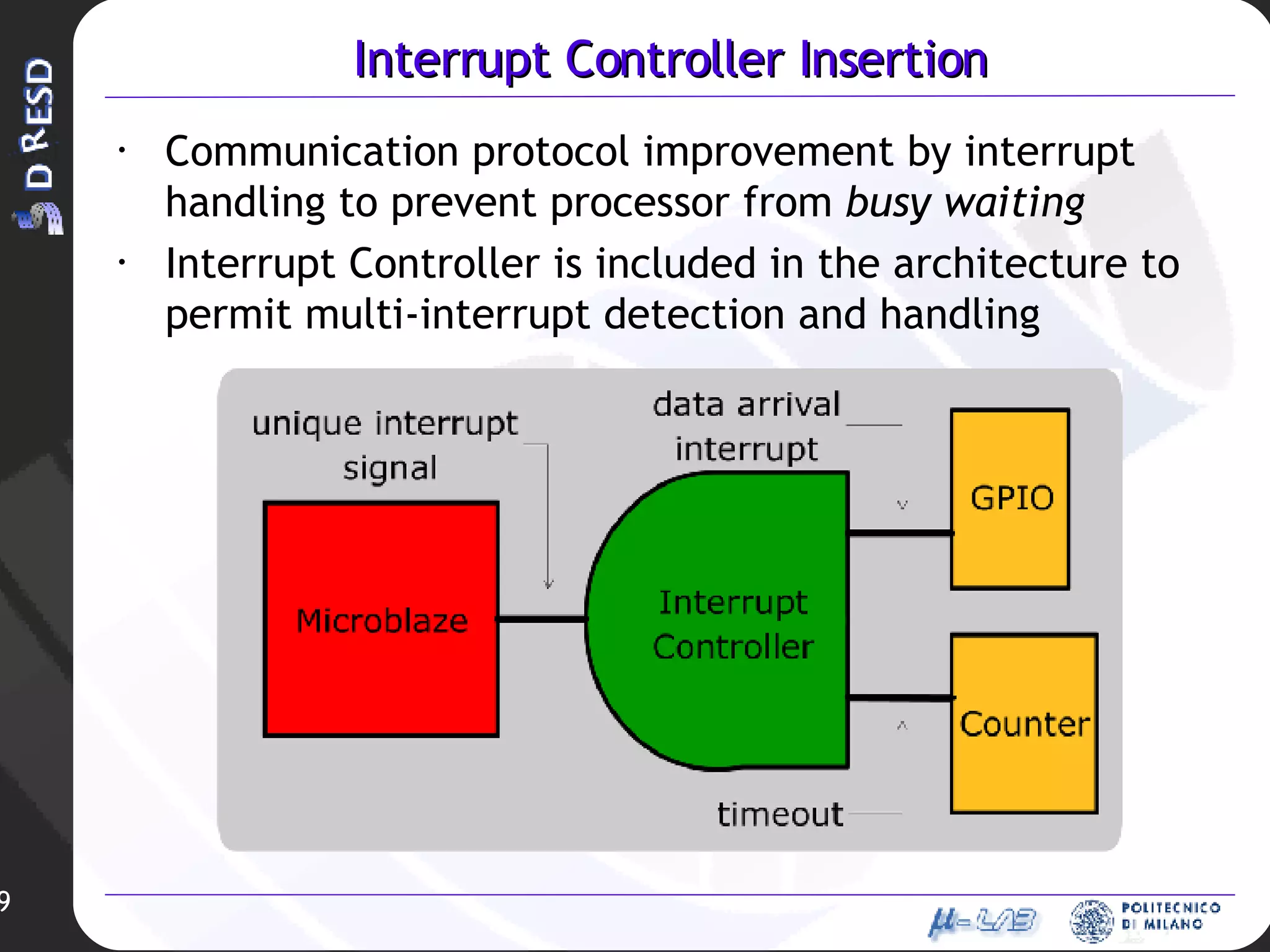

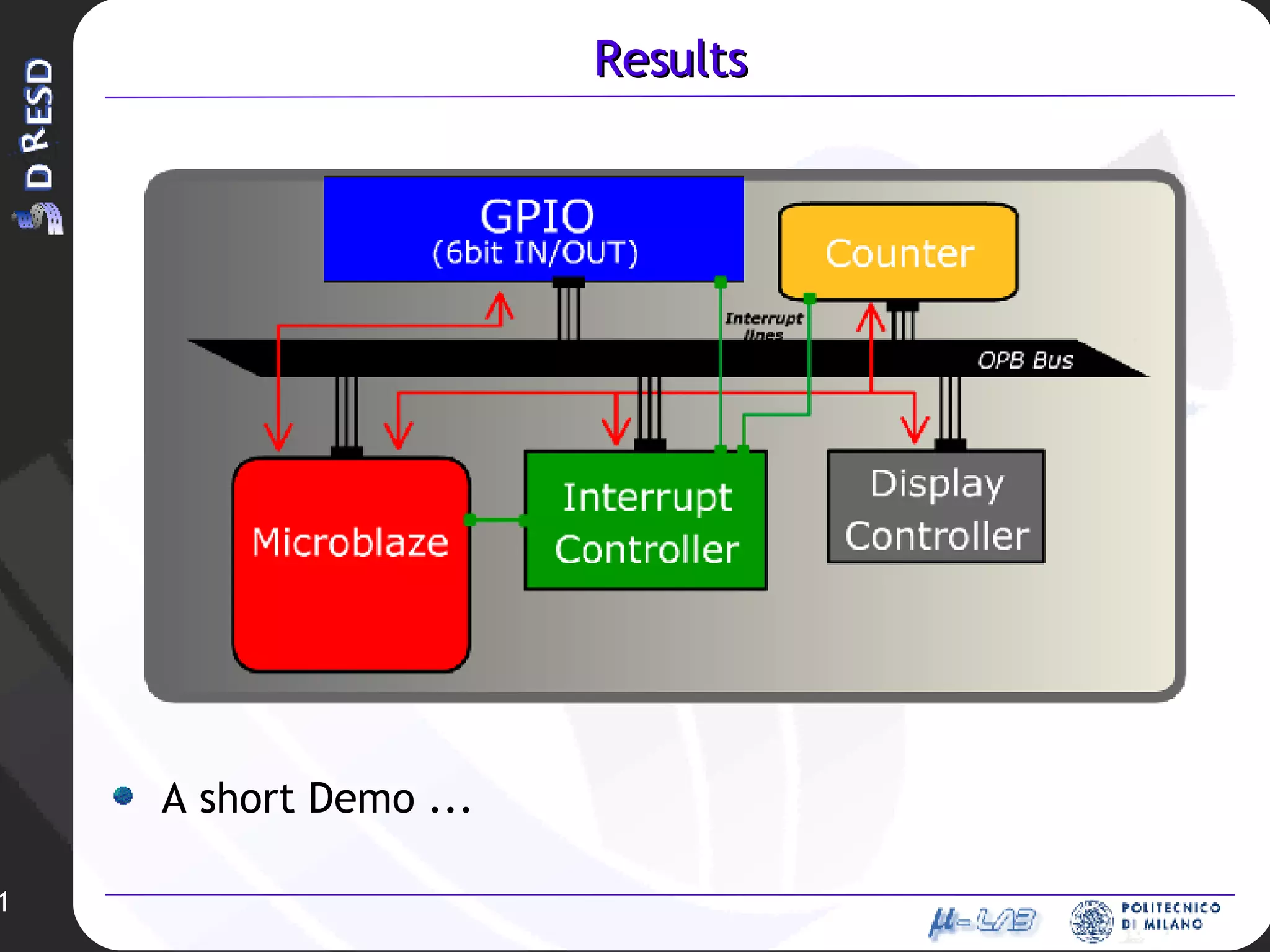

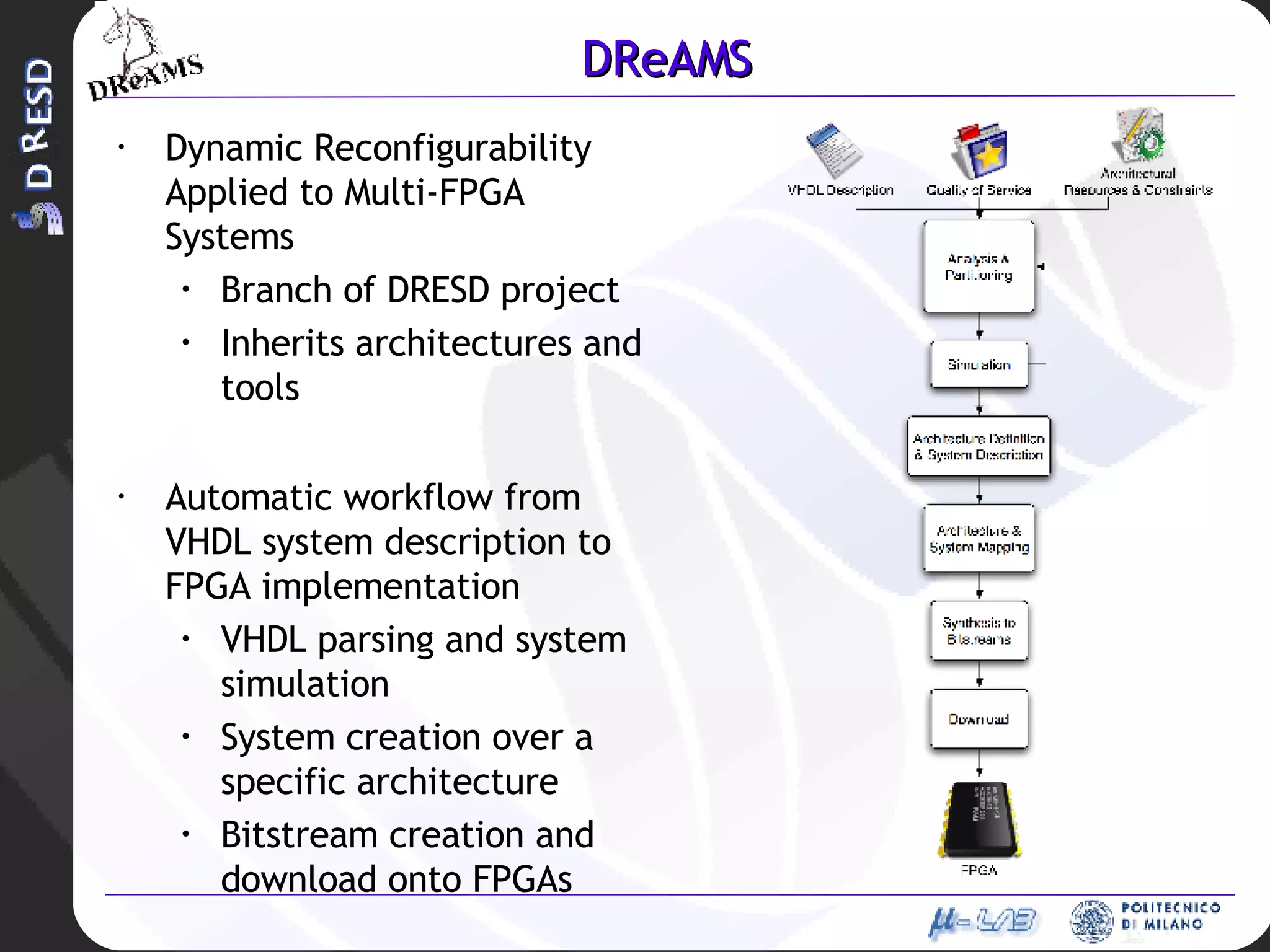

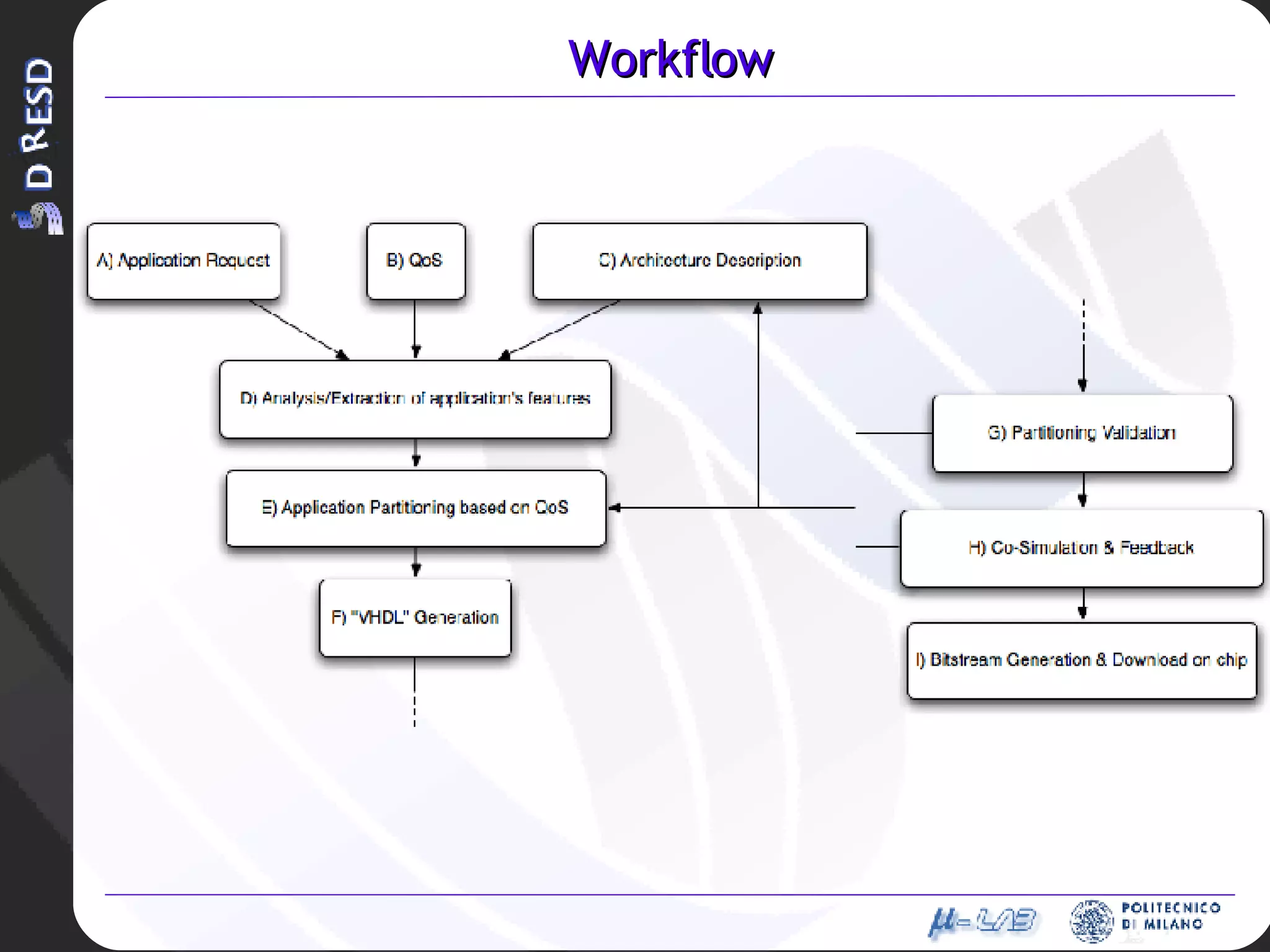

The document describes a multi-FPGA architecture called DReAMS that allows dynamic reconfiguration across multiple FPGAs. It inherits architectures and tools from an existing DRESD project. The workflow involves VHDL system description, simulation, system creation for a specific architecture, and bitstream creation and download onto FPGAs.

![SPartA A novel algorithm for multi-FPGA partitioning Alessandro Panella [email_address]](https://image.slidesharecdn.com/3ddresd-dreams3903/75/3D-DRESD-DReAMS-4-2048.jpg)

![Chimera Multi-FPGAs Architecture Definition Matteo Murgida [email_address]](https://image.slidesharecdn.com/3ddresd-dreams3903/75/3D-DRESD-DReAMS-20-2048.jpg)