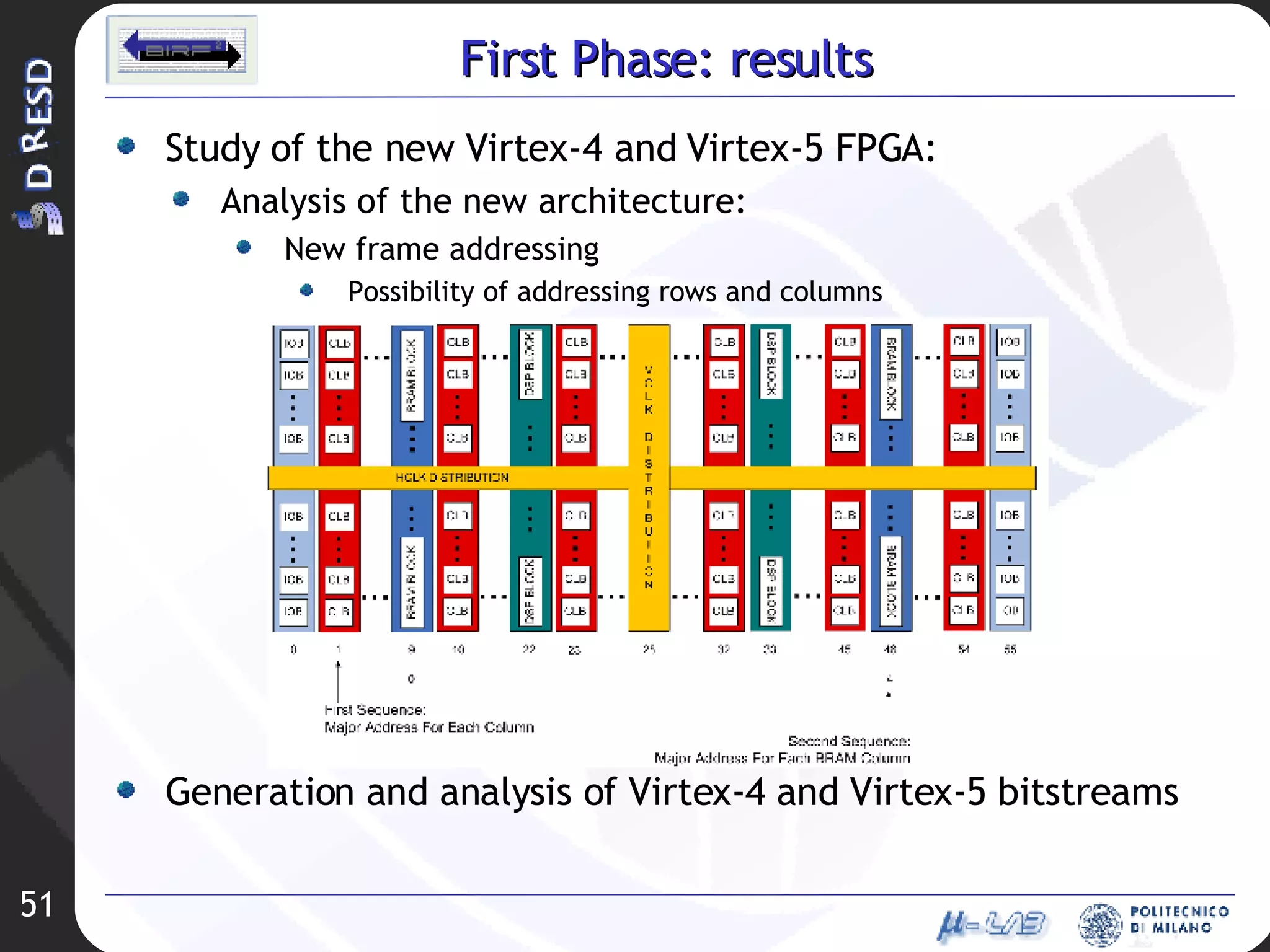

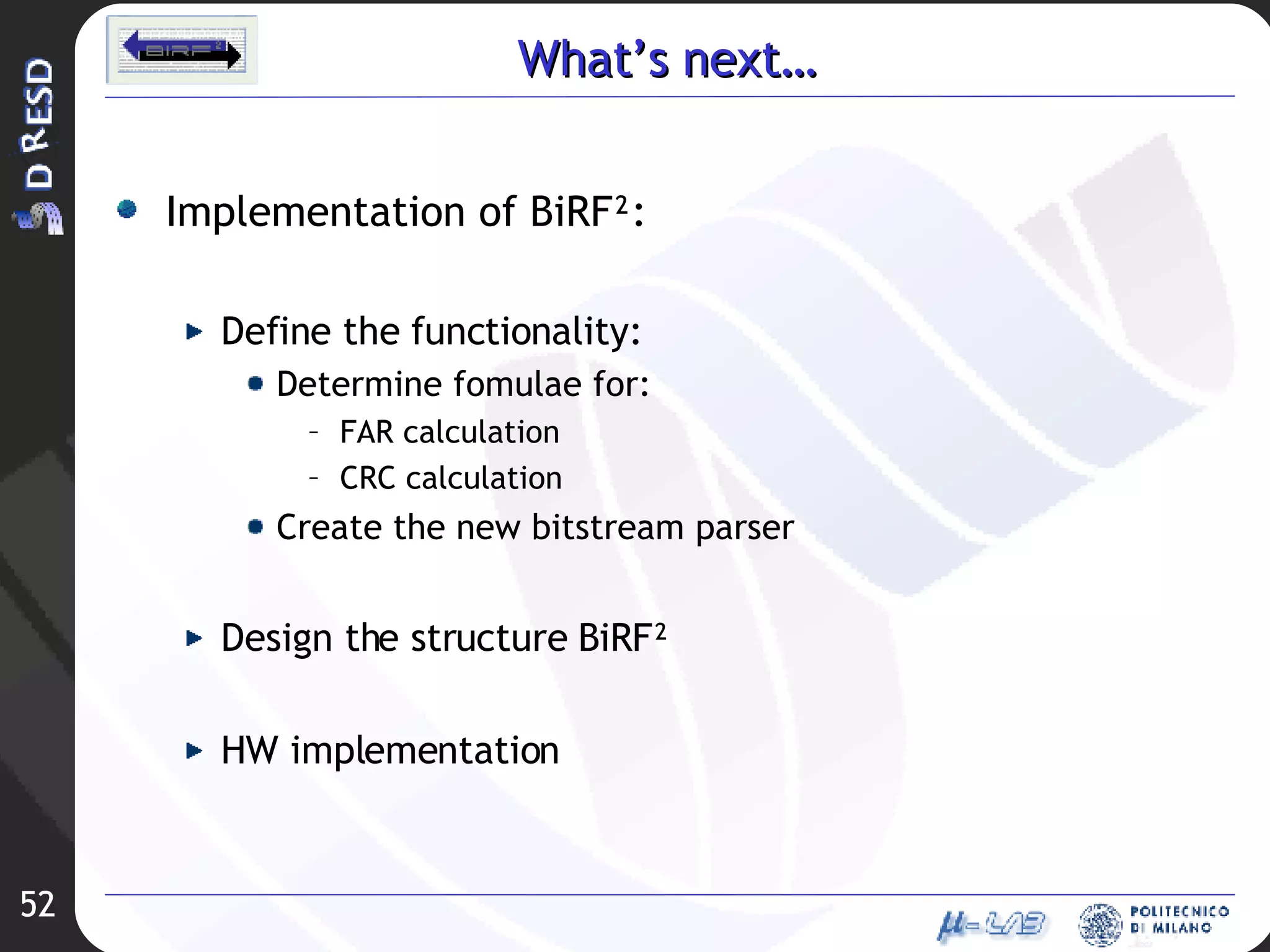

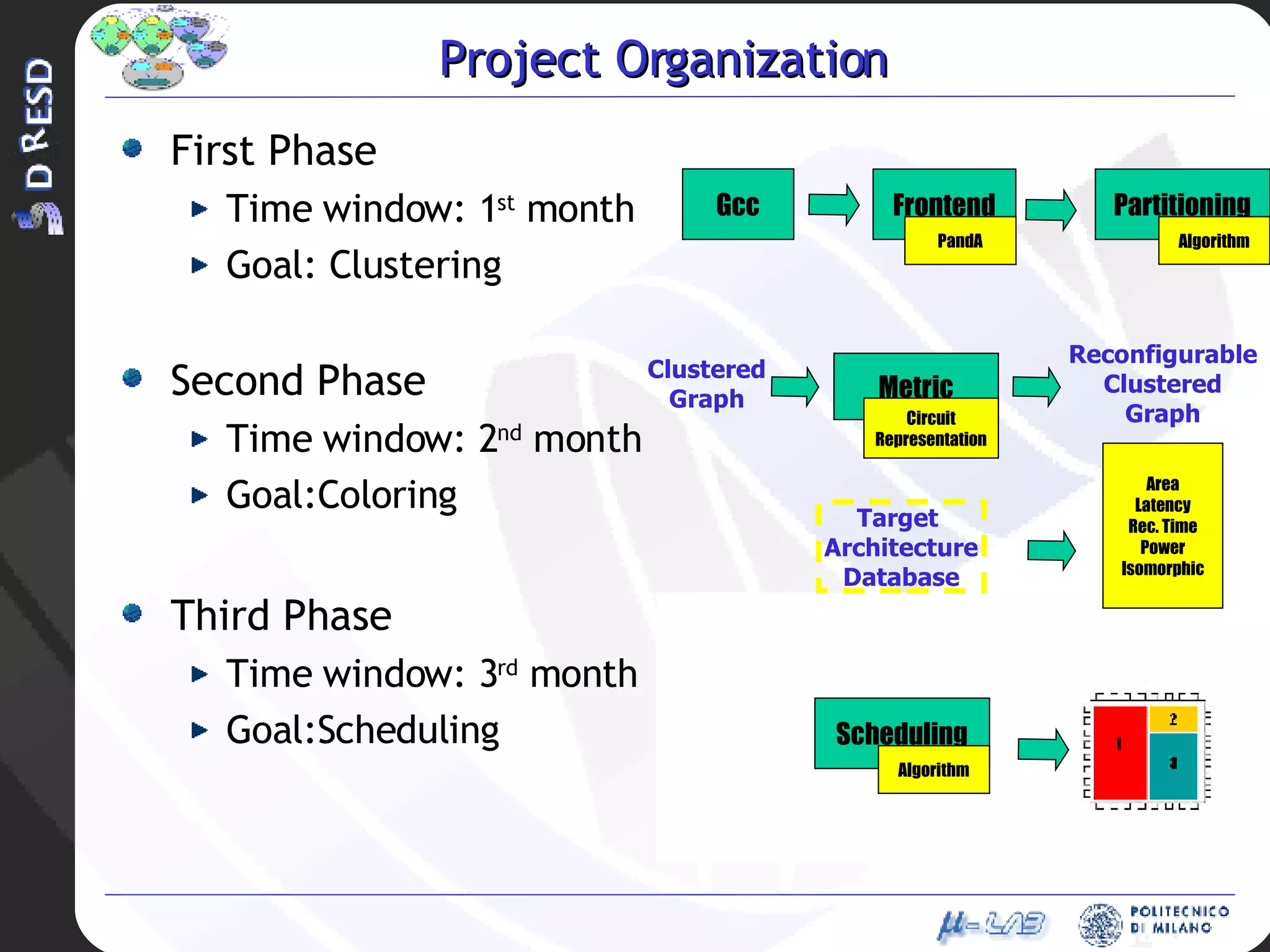

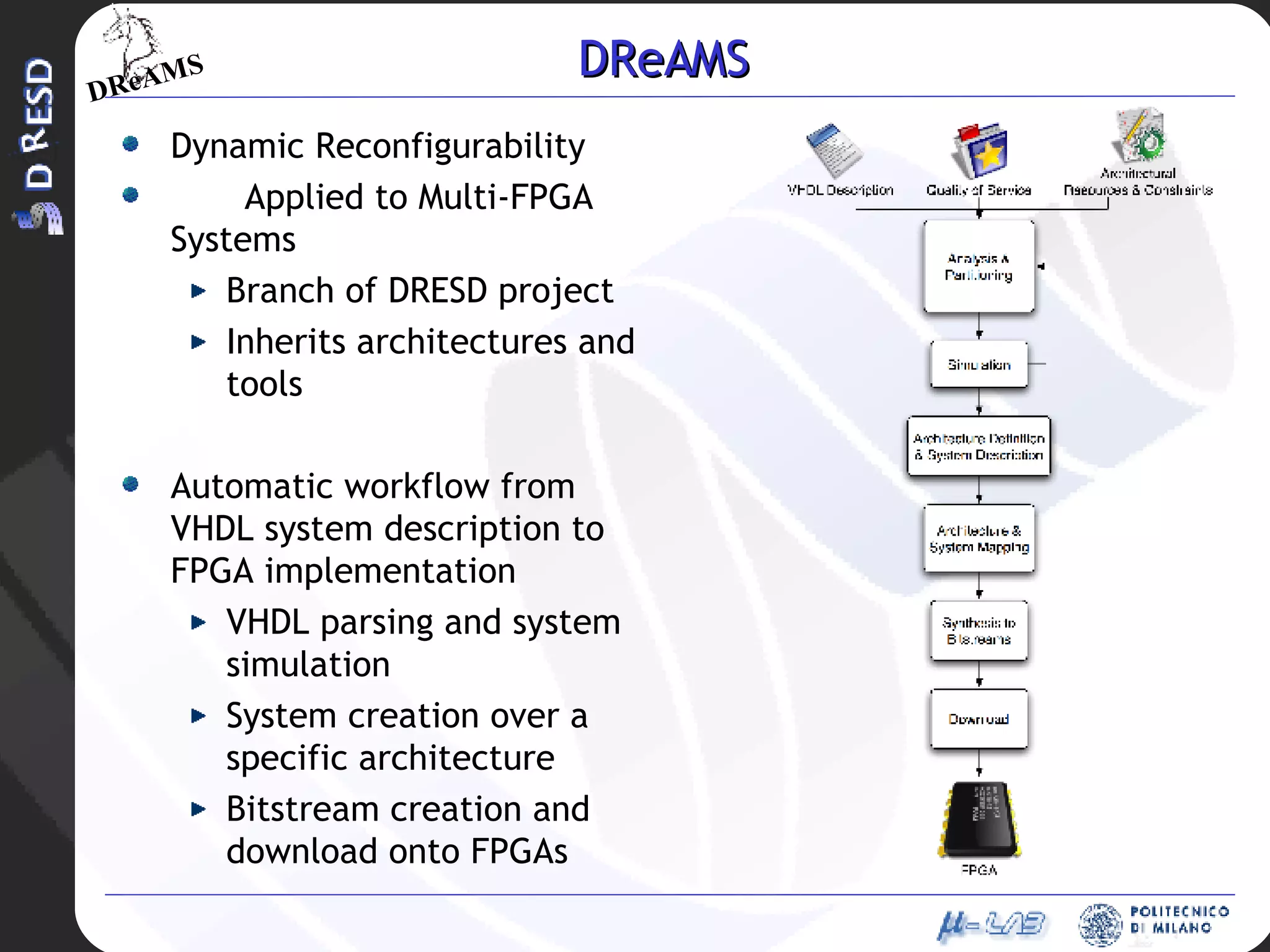

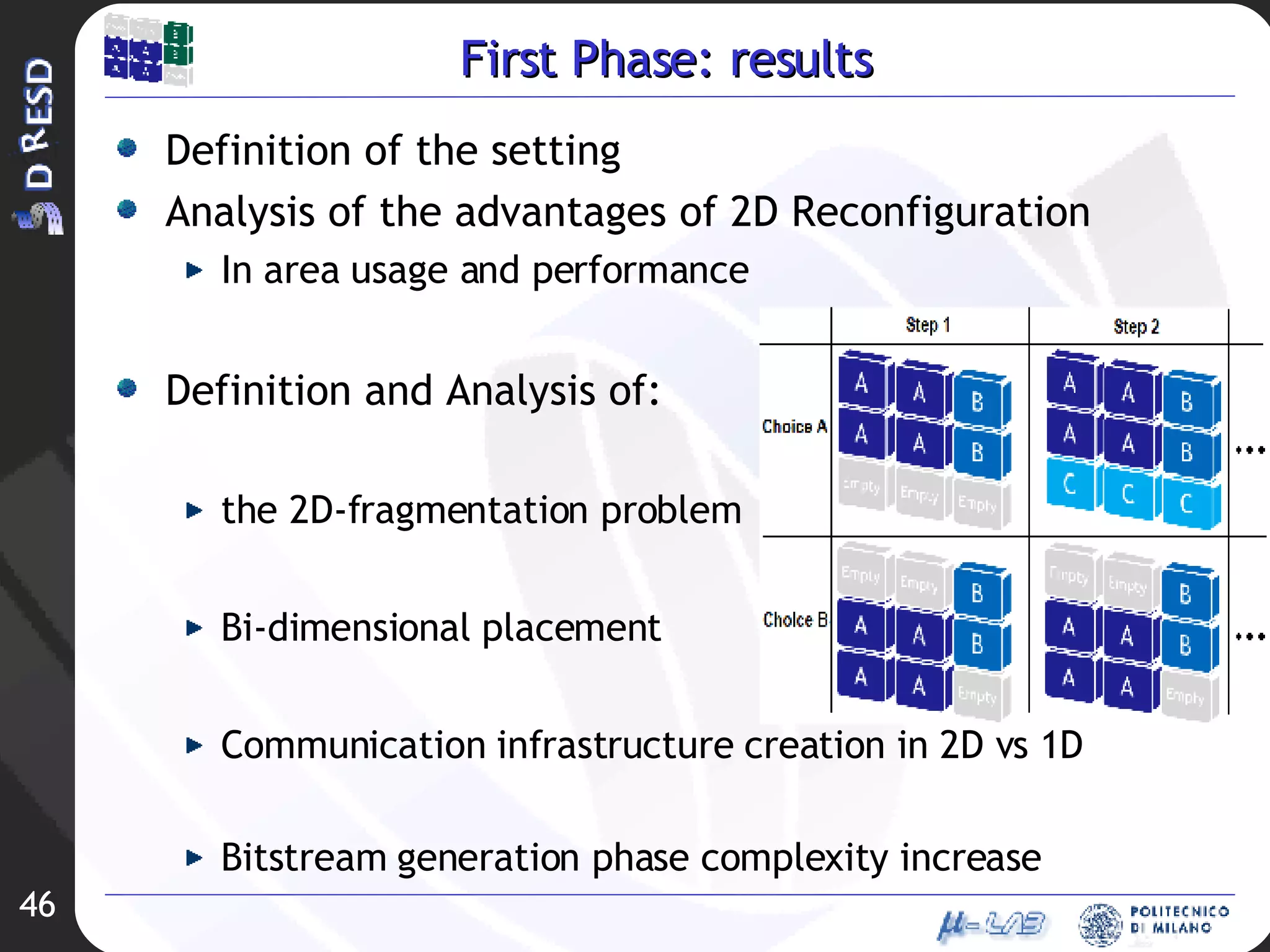

The document outlines several student projects being undertaken as part of a master's program. It provides brief descriptions of each project, including goals, organization into phases, and results from the initial phase. The projects cover topics like dynamic reconfiguration applied to multi-FPGA systems, communication infrastructure for reconfigurable embedded systems, operating system support for dynamic reconfiguration, and effects of 2D reconfiguration.

![Multi-FPGA Partitioning Alessandro Panella [email_address]](https://image.slidesharecdn.com/rev1-hpps-projects-2007-25785/75/Rev1-HPPS-Projects-2007-6-2048.jpg)

![Chimera Multi-FPGAs Architecture Definition Matteo Murgida [email_address]](https://image.slidesharecdn.com/rev1-hpps-projects-2007-25785/75/Rev1-HPPS-Projects-2007-11-2048.jpg)

![P rocessing E lements RE configuration I n R econfigurable A rchitectures Alessio Montone [email_address]](https://image.slidesharecdn.com/rev1-hpps-projects-2007-25785/75/Rev1-HPPS-Projects-2007-18-2048.jpg)

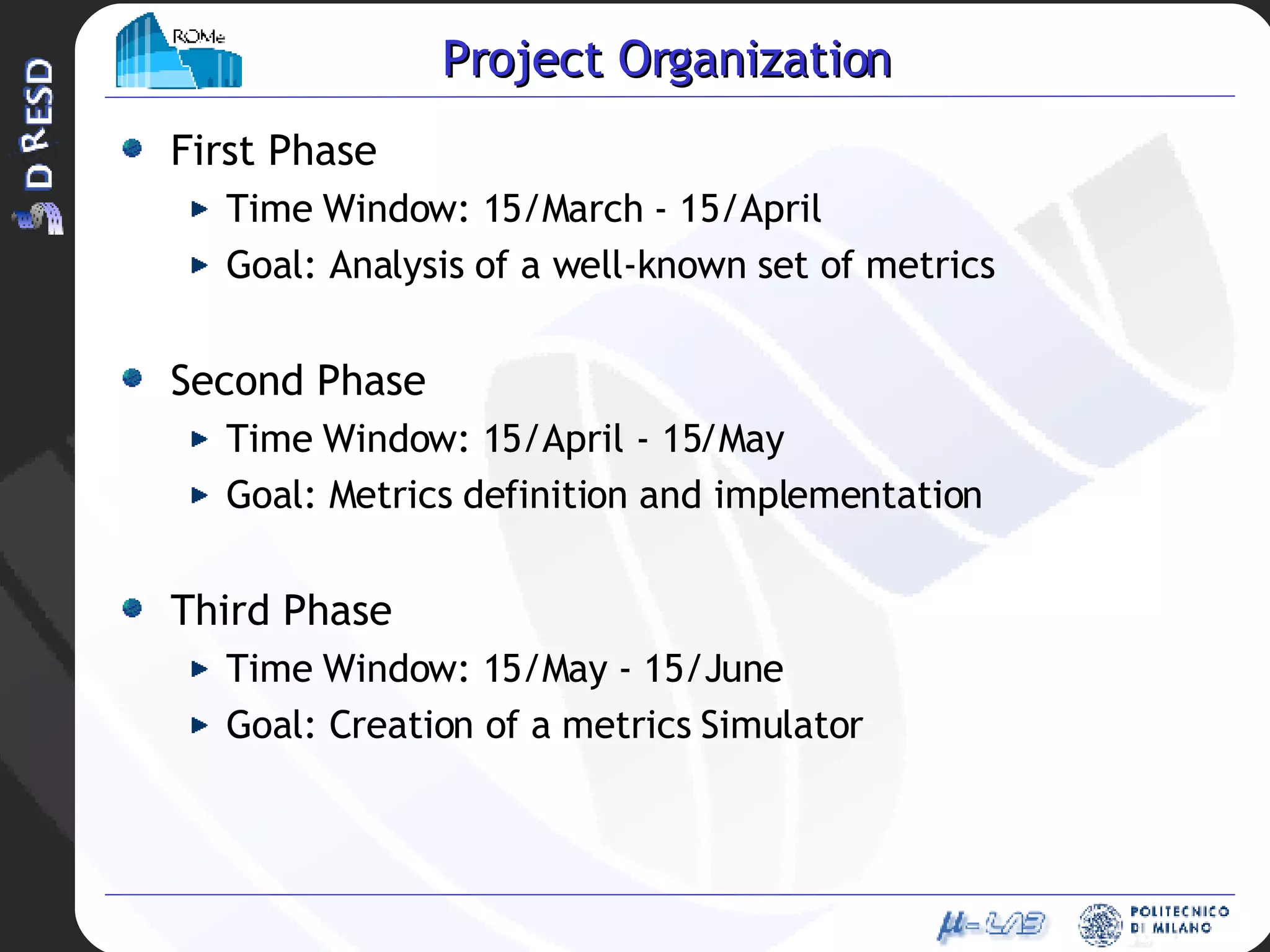

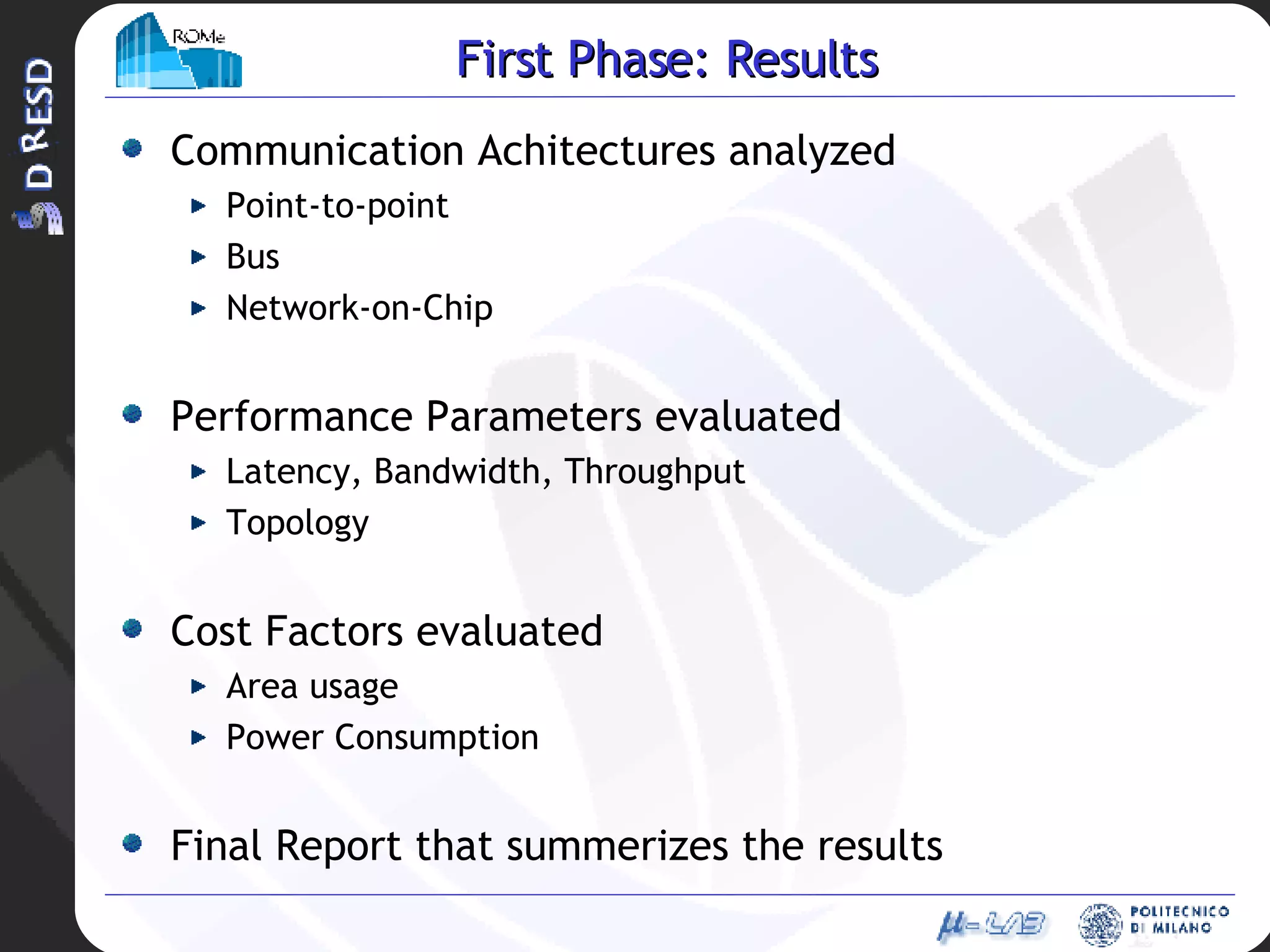

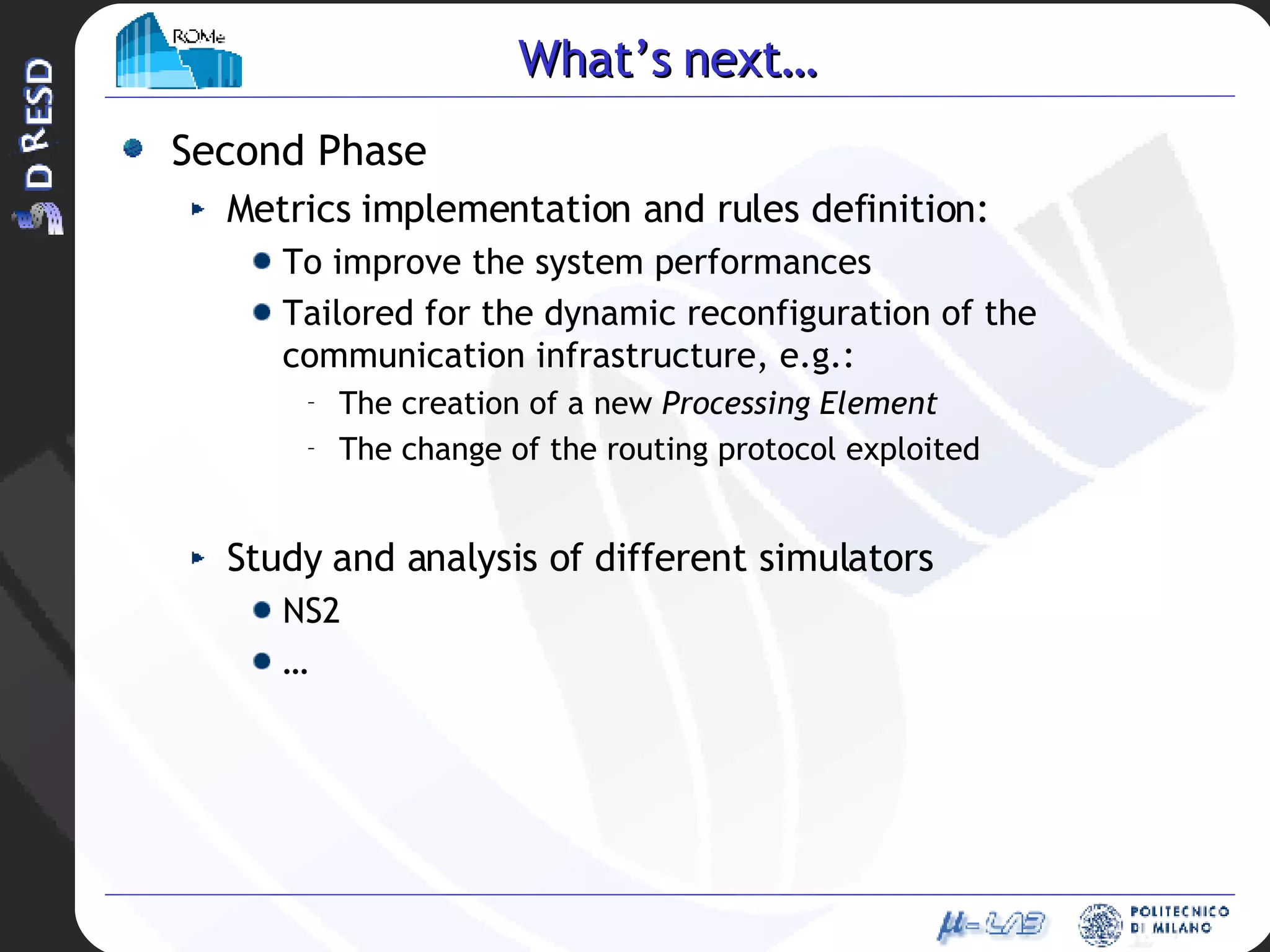

![R econfiguration O riented Me trics Alessandro Meroni [email_address]](https://image.slidesharecdn.com/rev1-hpps-projects-2007-25785/75/Rev1-HPPS-Projects-2007-23-2048.jpg)

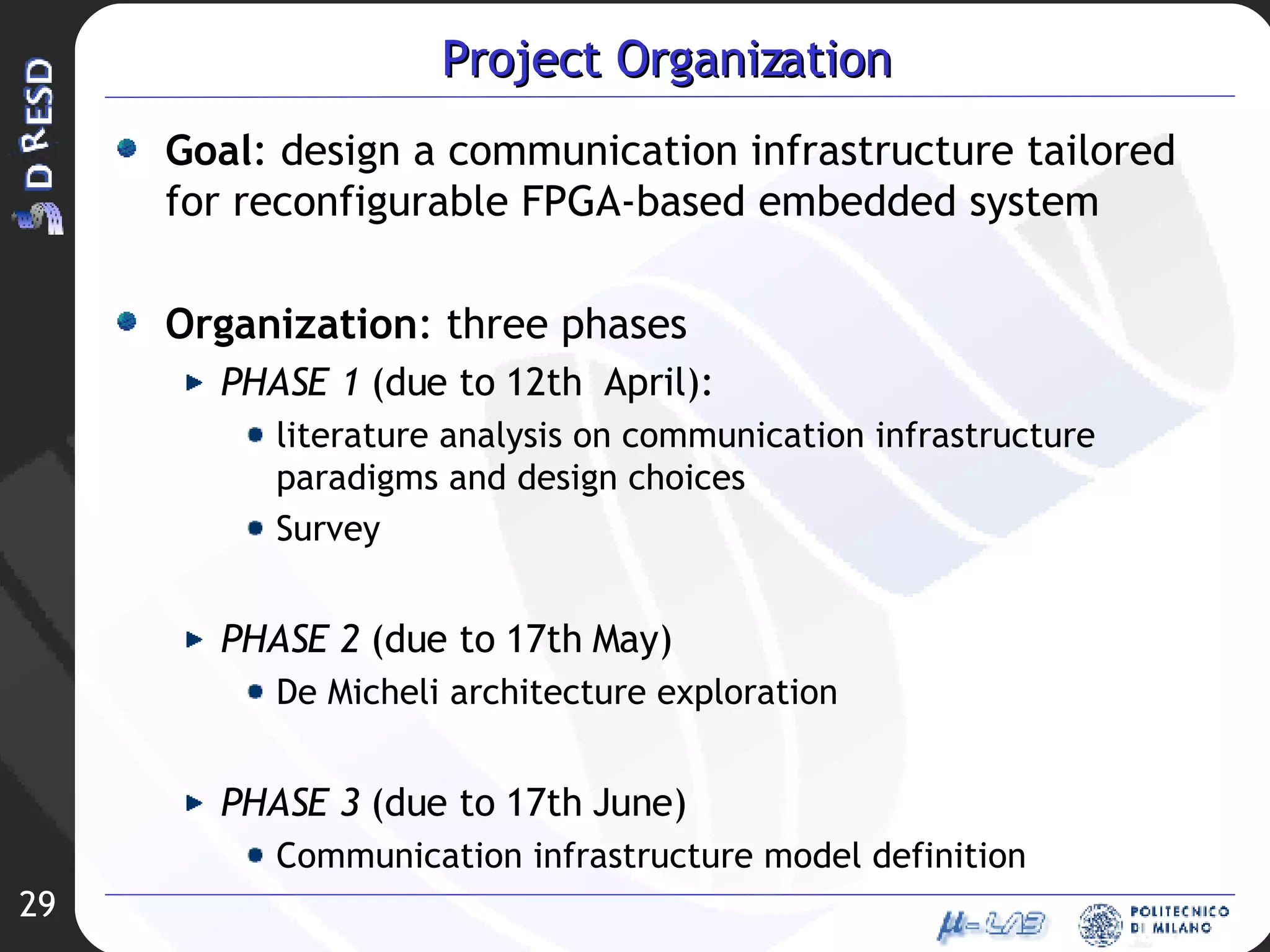

![RE configurable C ommunication I nfrastructure F or E mbedded-systems Simone Corbetta [email_address]](https://image.slidesharecdn.com/rev1-hpps-projects-2007-25785/75/Rev1-HPPS-Projects-2007-28-2048.jpg)

![Development of an OS architecture-independent layer for dynamic reconfiguration Ivan Beretta [email_address]](https://image.slidesharecdn.com/rev1-hpps-projects-2007-25785/75/Rev1-HPPS-Projects-2007-33-2048.jpg)

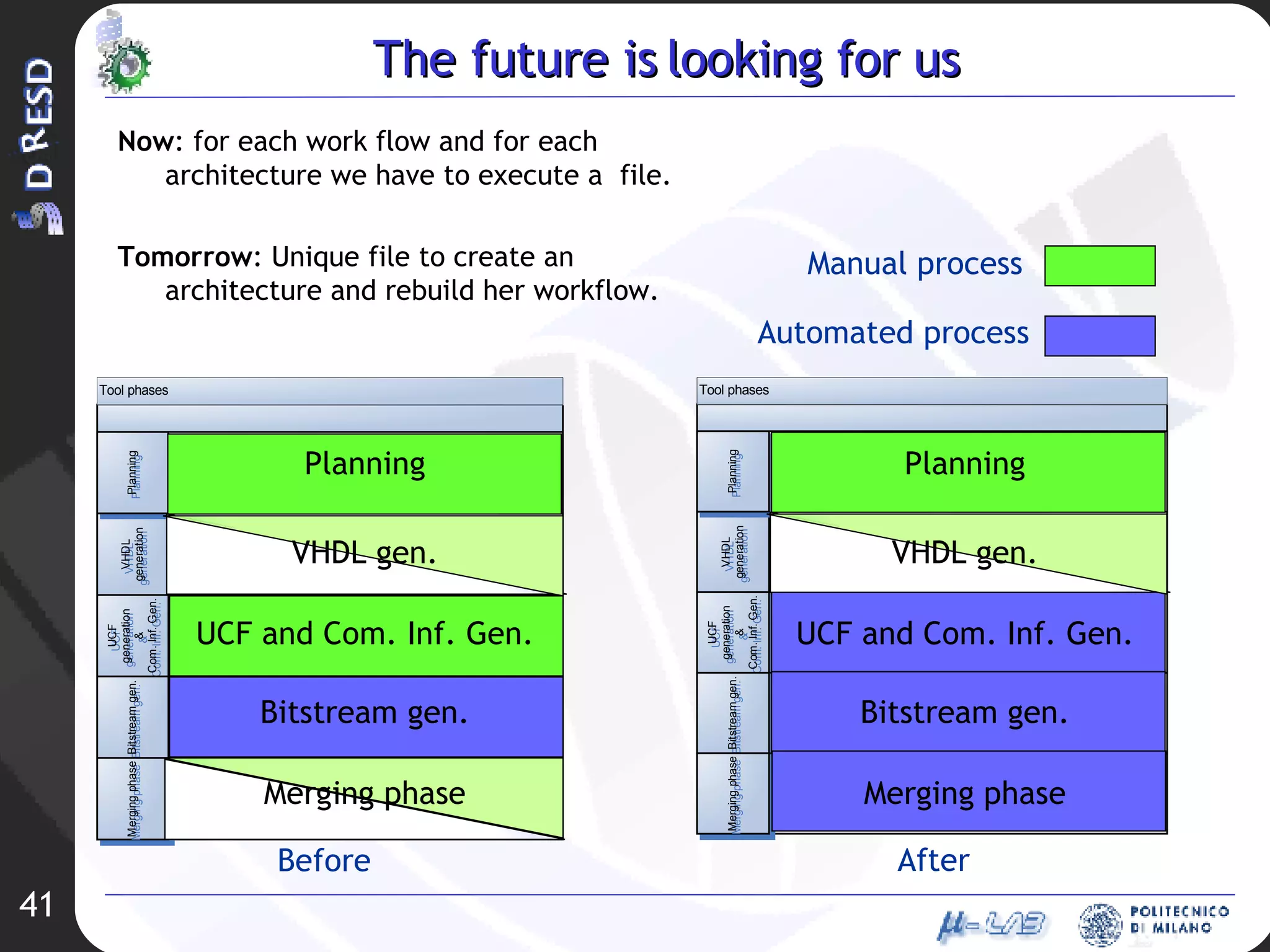

![Design FLow Antonio Piazzi [email_address]](https://image.slidesharecdn.com/rev1-hpps-projects-2007-25785/75/Rev1-HPPS-Projects-2007-38-2048.jpg)

![Effects of 2D Reconfiguration in a Reconfigurable System Massimo Morandi [email_address]](https://image.slidesharecdn.com/rev1-hpps-projects-2007-25785/75/Rev1-HPPS-Projects-2007-44-2048.jpg)

![Relocation for 2D Reconfigurable Systems Marco Novati [email_address]](https://image.slidesharecdn.com/rev1-hpps-projects-2007-25785/75/Rev1-HPPS-Projects-2007-49-2048.jpg)