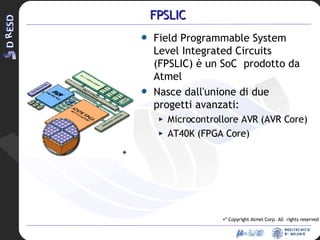

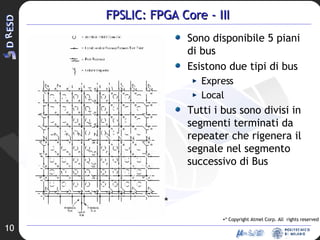

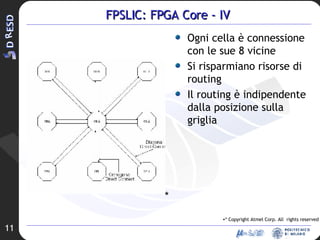

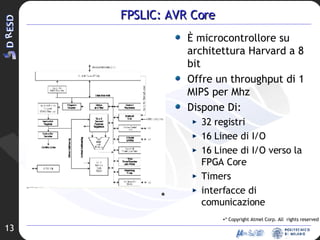

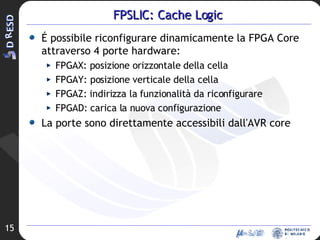

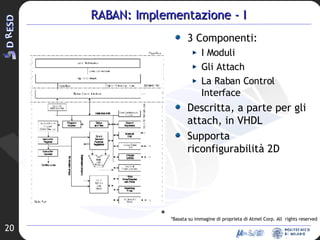

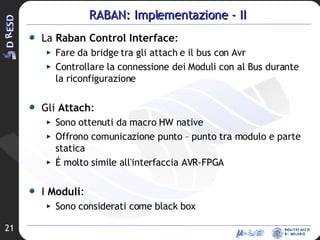

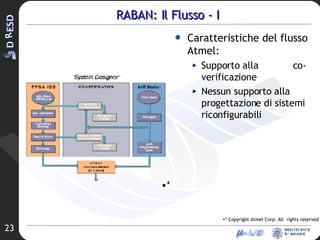

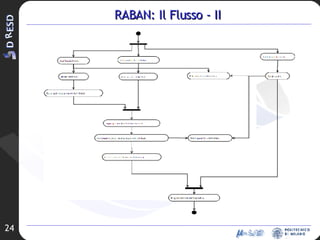

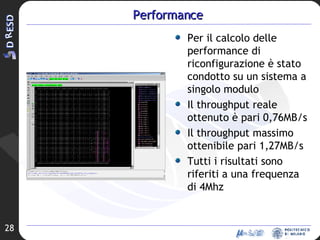

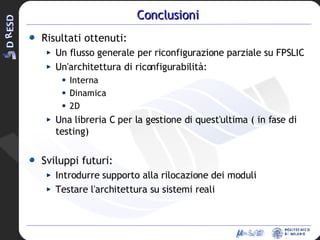

Il documento descrive una reconfigurazione per dispositivi Atmel basata sul core n-module AT94K, proponendo un flusso alternativo rispetto a Xilinx. Presenta l'architettura FPSLIC, che combina microcontrollore AVR e FPGA, e discute le modalità di riconfigurazione dinamica. Viene inoltre analizzato il flusso di implementazione, le prestazioni ottenute e le conclusioni riguardanti sviluppi futuri.