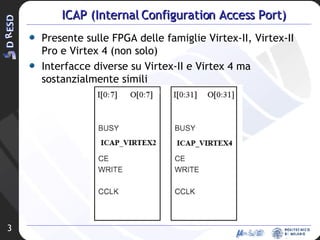

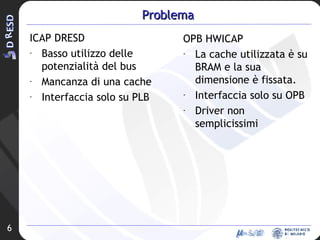

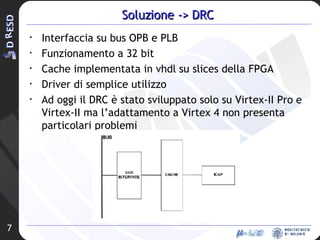

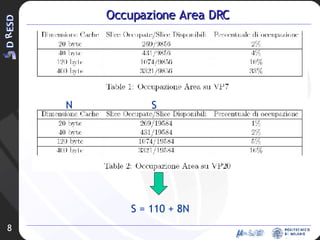

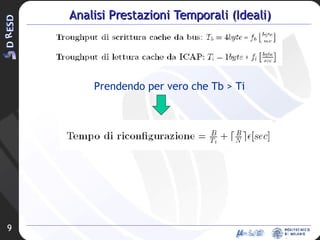

Il documento discute il DRC (Dresd Reconfiguration Controller) per FPGA della famiglia Virtex, confrontando ICAP e OPB HWiCAP, evidenziando i problemi e le limitazioni di ciascuno. Propone una soluzione con un'interfaccia DRC su bus OPB e PLB, funzionante a 32 bit e con cache implementata in VHDL, che migliora l'usabilità. Nonostante i progressi, il DRC ha ancora limiti relativi al throughput e all'occupazione dell'area, suggerendo potenziali sviluppi futuri, inclusa l'integrazione di un meccanismo DMA.