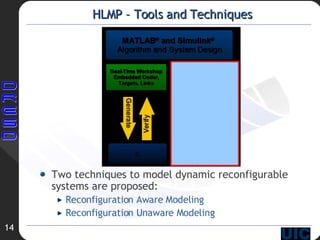

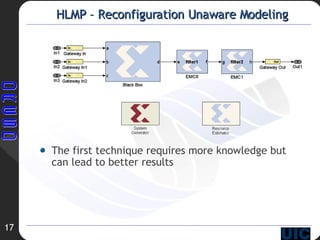

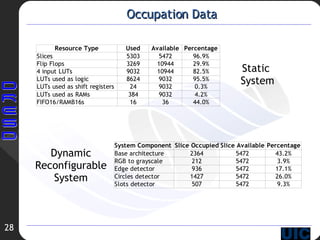

The document summarizes Fabio Cancare's thesis defense about modeling methodologies for dynamic reconfigurable systems. The thesis proposes a model-based design flow to implement large designs onto FPGAs with limited resources. It outlines high-level modeling and low-level implementation phases. A case study implements vision system functionality on an FPGA more efficiently using dynamic reconfiguration compared to a static system.

![General Information Webpage www.dresd.org/?q=hlr Mailing List [email_address] Contact To have more information regarding HLR: [email_address] For a complete list of information on how to contact us: www.dresd.org/?q=contact _hlr](https://image.slidesharecdn.com/uiccancarethesis-1211289969650103-9/85/UIC-Thesis-Cancare-33-320.jpg)