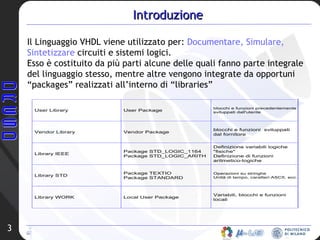

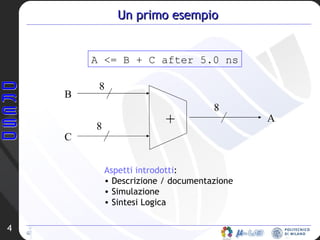

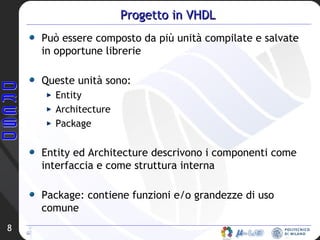

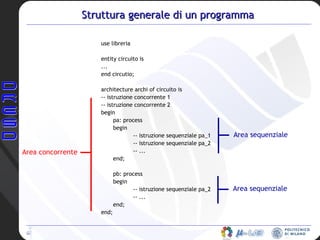

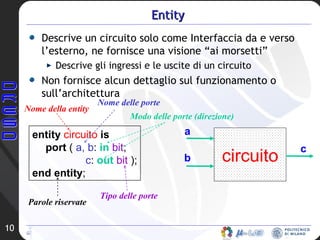

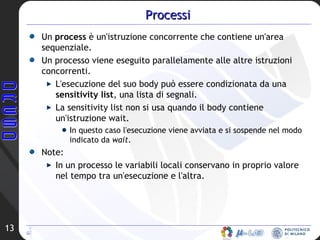

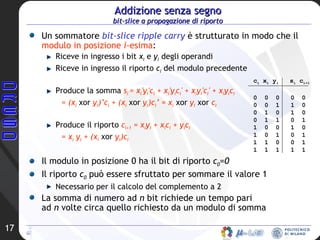

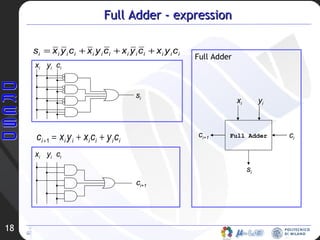

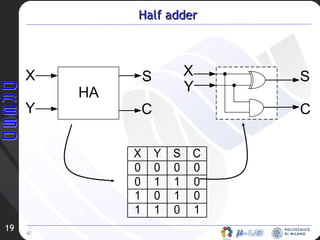

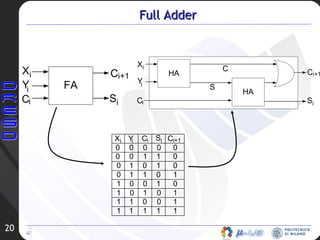

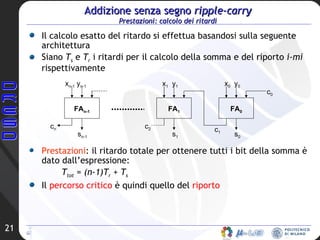

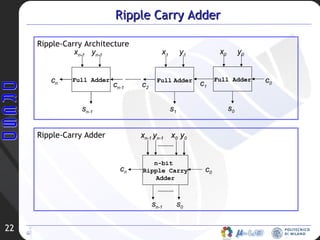

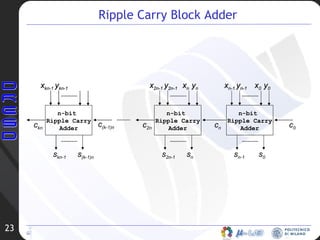

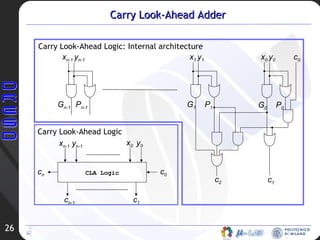

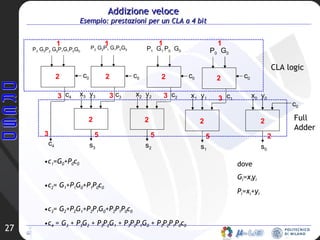

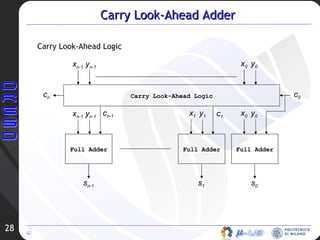

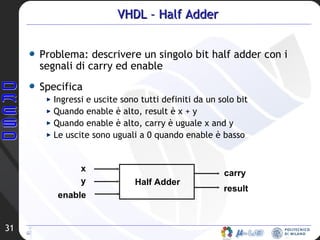

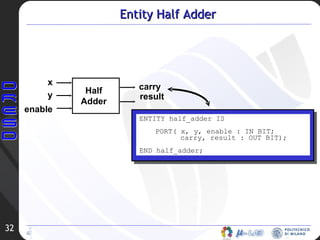

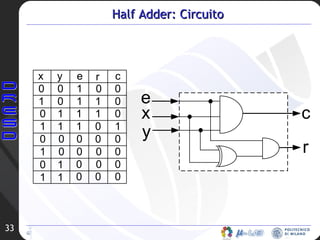

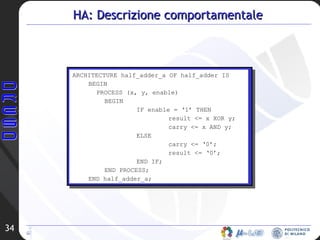

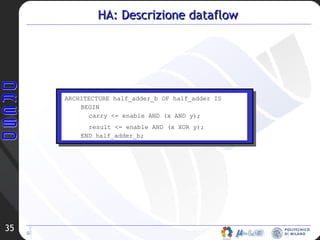

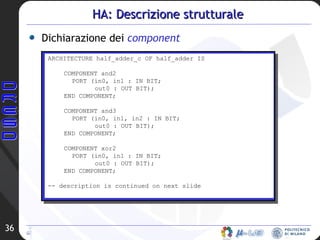

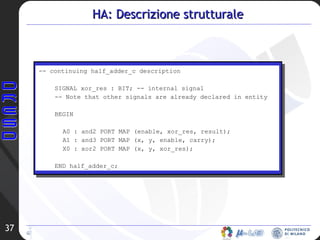

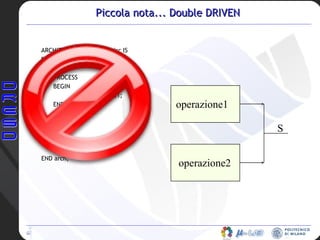

Il documento fornisce una panoramica sul linguaggio VHDL, utilizzato per la documentazione, simulazione e sintesi di circuiti e sistemi logici. Viene descritto come strutturato in unità come entity, architecture e package, con esempi pratici di codifica e la distinzione tra diverse modalità di descrizione (comportamentale, strutturale, dataflow). Si approfondiscono anche tecniche di somma e ritardo nei circuiti, come il sommatore ripple carry e il carry-look-ahead adder.

![VHDL: una breve introduzione DRESD H ow T o (DHow2) – L1 DRESD Team [email_address]](https://image.slidesharecdn.com/l1-1227868839593501-9/75/DHow2-L1-1-2048.jpg)