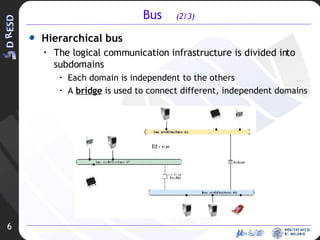

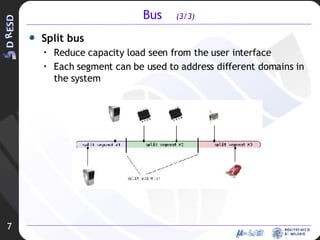

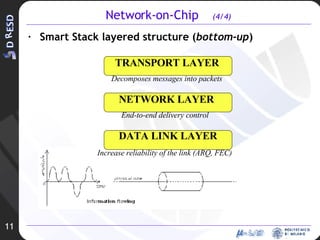

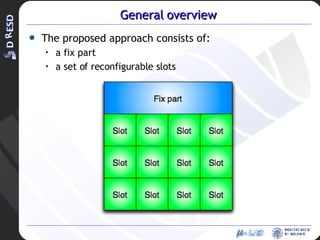

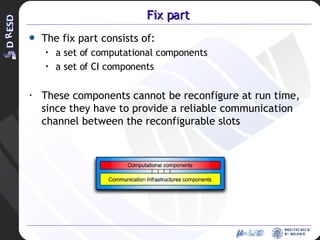

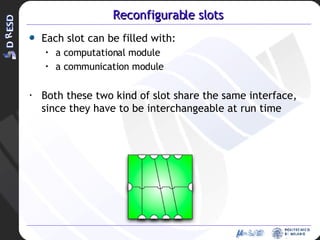

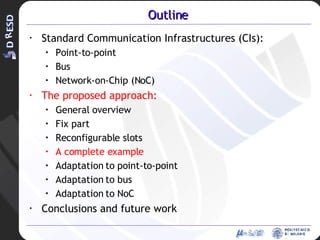

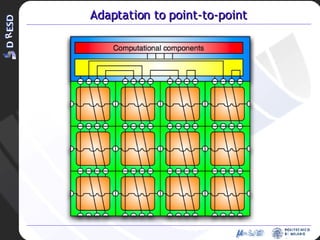

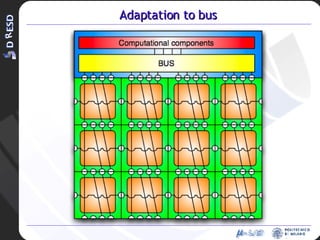

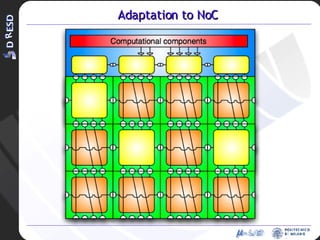

The document discusses different communication infrastructures (CIs) like point-to-point, bus, and Network-on-Chip (NoC). It then proposes an approach that has a fixed part and reconfigurable slots that can be configured with computational or CI modules at runtime to adapt the CI. The approach can adapt to different CIs and is demonstrated with a complete example. Future work includes exploring the sizes of the fixed part, slots, and CIs.