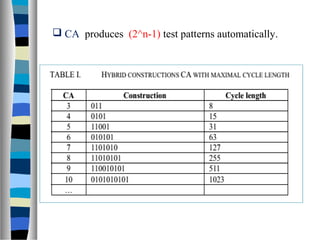

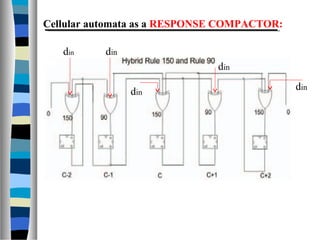

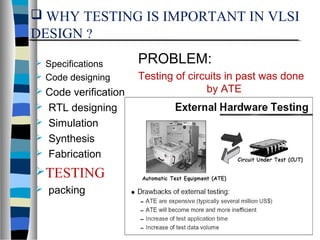

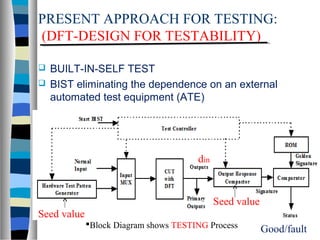

The document outlines a mini-project on implementing hybrid cellular automata for testing patterns and compacting responses in VLSI design. It discusses objectives, working principles, advantages, disadvantages, and potential applications of the technology. Key topics include the importance of testing in VLSI design, the use of built-in self-test methodologies, and future extensions related to self-repair and programmable memory testing.

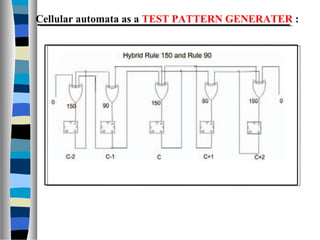

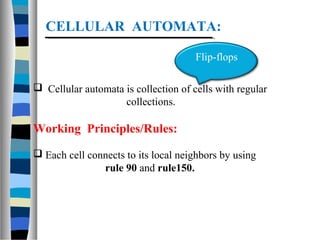

![ Rule 90: Rule 150:

Transition function [rule 90] : Xc(t+1) = Xc-1(t) xor Xc+1(t).

Transition function [rule 150]: Xc(t+1) = Xc-1(t) xor Xc(t) xor Xc+1(t).

C-1 : past

C : present

C+1 : future

Diagrammatic View:](https://image.slidesharecdn.com/1streview-140727055851-phpapp01/85/cellular-automata-as-a-test-pattern-generator-and-output-response-compactor-for-bist-8-320.jpg)