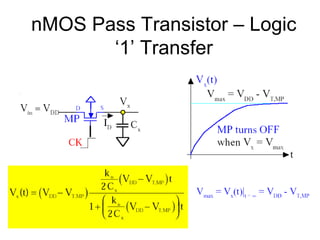

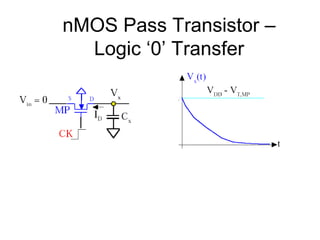

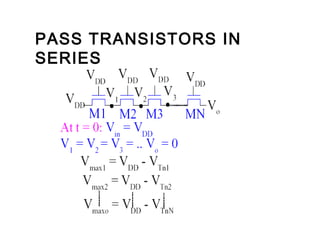

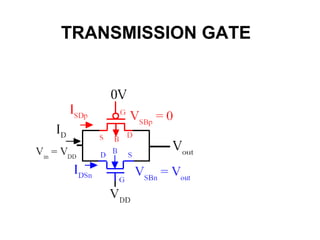

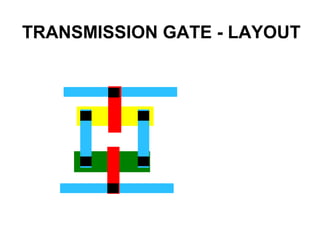

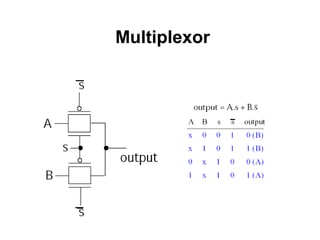

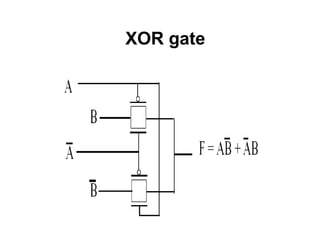

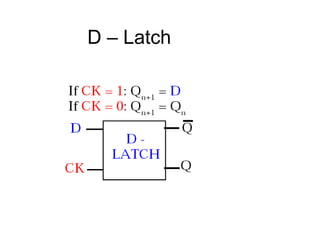

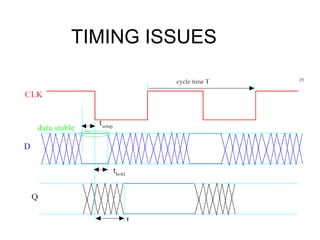

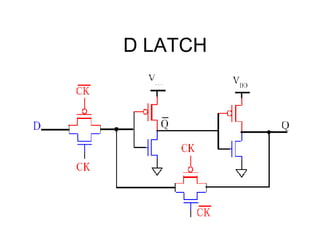

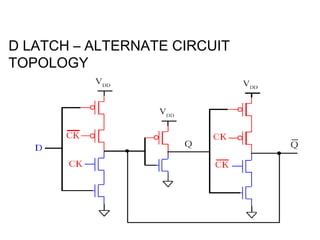

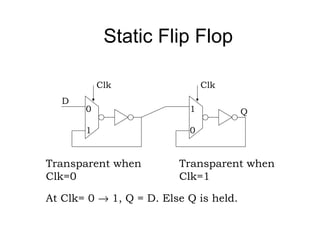

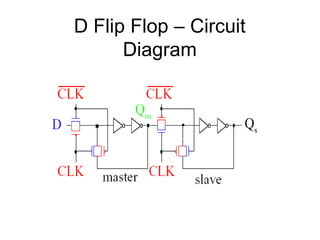

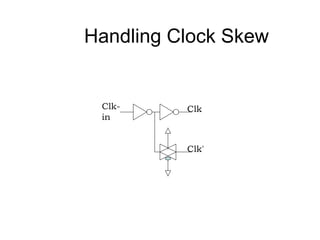

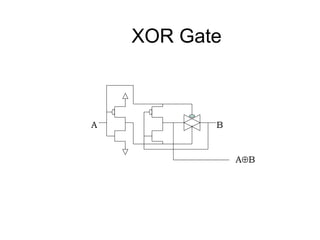

The document discusses pass transistor logic circuits. It introduces nMOS pass transistors and their transmission properties. Transmission gates are described as using an nMOS and PMOS pass transistor together to pass both strong 0s and 1s. Transmission gate applications covered include multiplexers, XOR gates, D latches, and D flip-flops. Clock skew management in pass transistor logic is also discussed. Finally, different pass transistor logic families are presented.