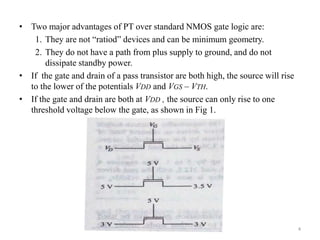

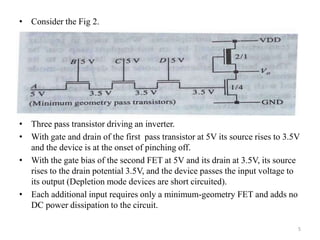

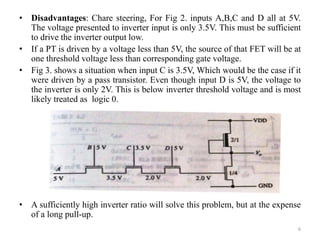

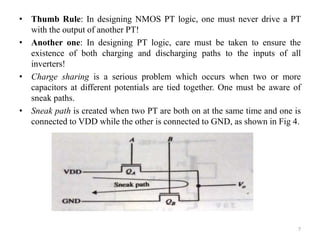

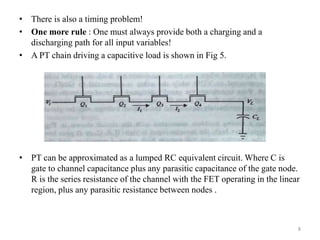

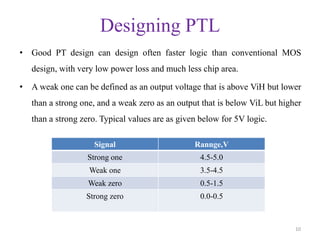

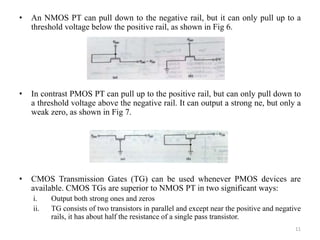

Pass-transistor logic uses transistors as switches to pass logic levels between circuit nodes, rather than connecting directly to power supplies, reducing the number of active devices. It has advantages over standard NMOS gate logic like being minimum geometry and dissipating no standby power. However, voltage differences decrease between logic levels at each stage.

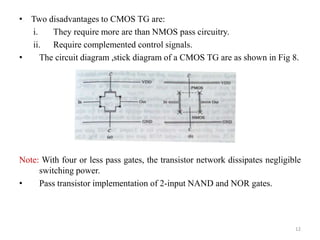

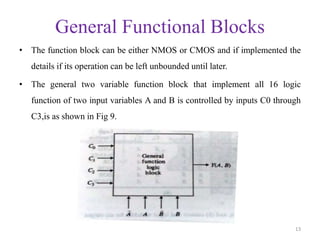

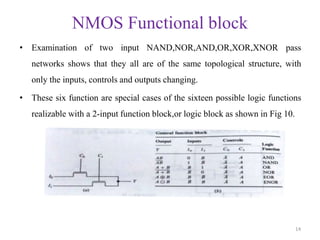

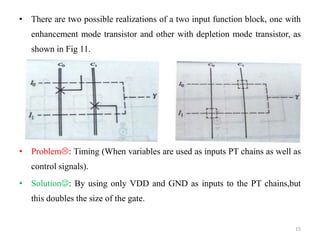

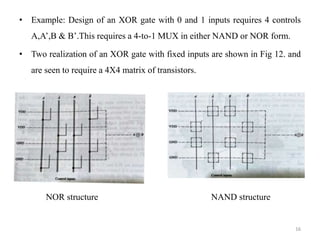

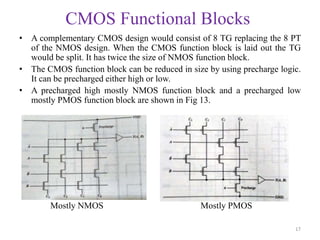

General functional blocks can implement all 16 logic functions of two inputs using NMOS or CMOS pass transistors controlled by four input signals. NMOS blocks pull down to ground but only up to a threshold below power, while CMOS transmission gates can output strong ones and zeros. Precharge logic can reduce the size of CMOS blocks.