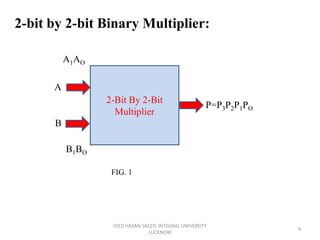

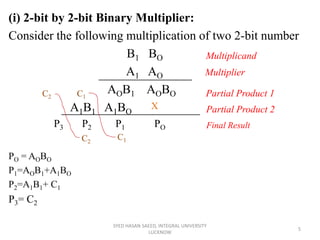

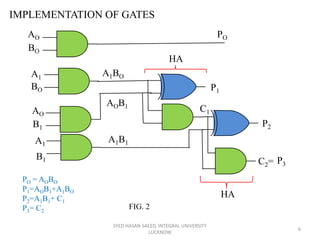

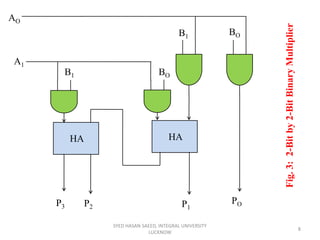

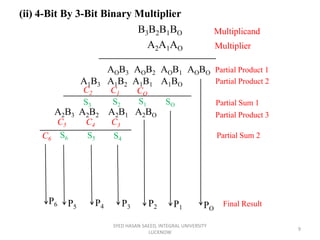

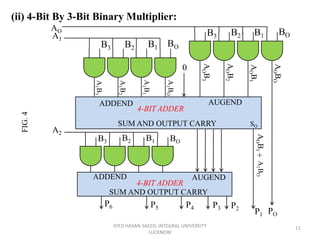

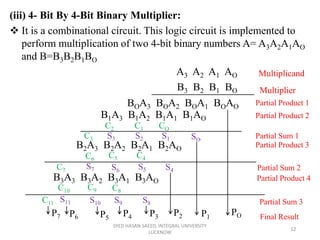

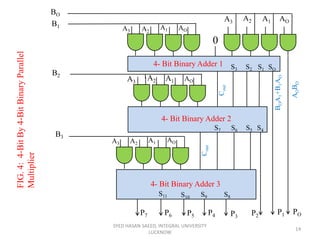

The document discusses binary multipliers. It describes how a combinational multiplier circuit performs multiplication by multiplying the multiplicand by each bit of the multiplier starting from the least significant bit. Each multiplication forms a partial product that is shifted left. The final product is the sum of the partial products. It then provides examples of 2-bit by 2-bit and 4-bit by 3-bit binary multipliers, showing how the partial products are generated using AND gates and added using half adders or full adders.