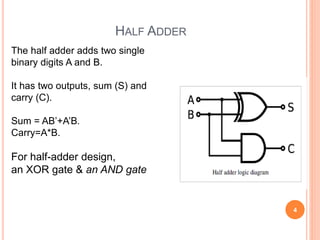

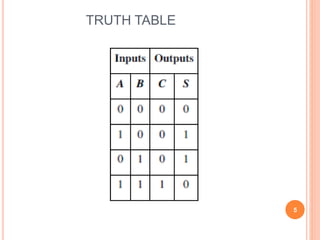

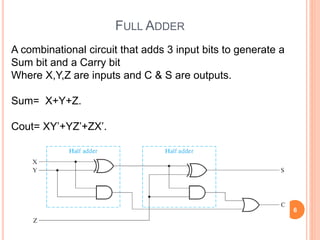

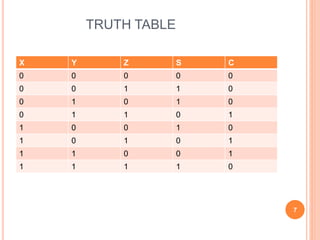

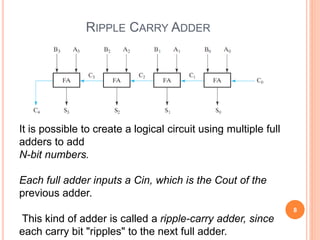

This document discusses different types of digital adders. It defines an adder as a digital circuit that performs addition of numbers. It describes half adders, full adders, ripple carry adders, and look ahead carry units. For half adders, it provides the logic equations for sum and carry outputs. For full adders, it gives the logic equations for sum and carry outputs and includes the truth table. It explains that ripple carry adders use multiple full adders in sequence to add N-bit numbers, with each carry bit "ripplying" to the next full adder.