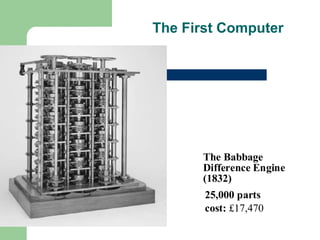

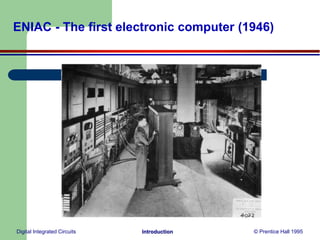

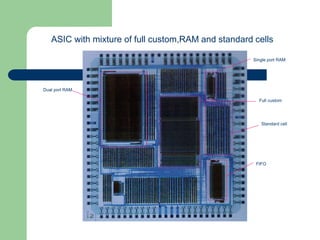

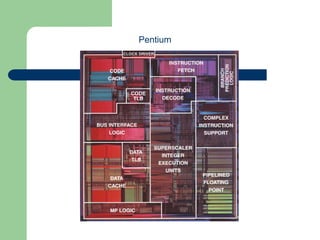

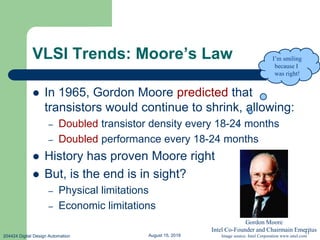

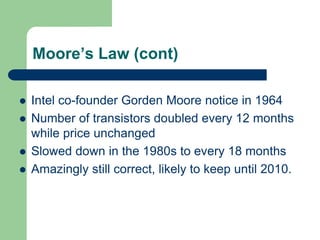

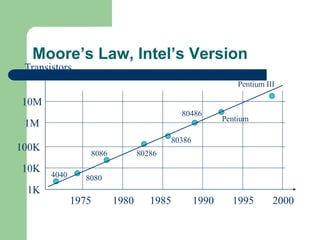

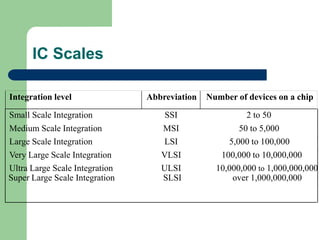

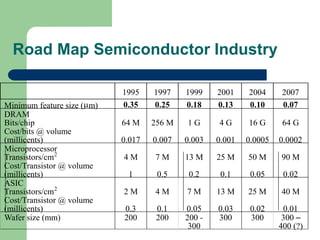

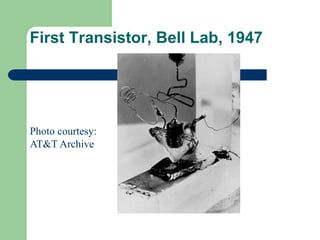

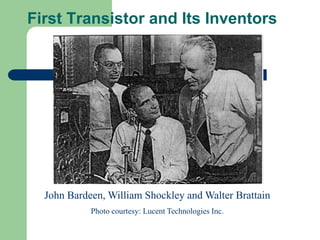

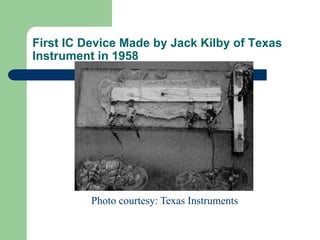

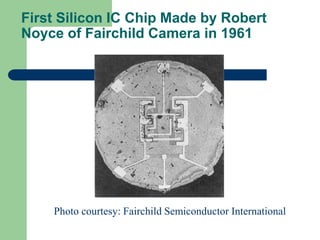

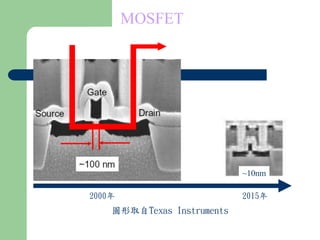

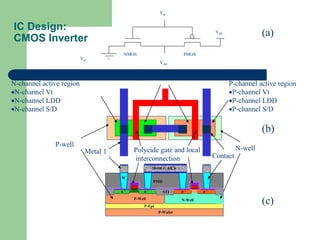

The document provides an overview of VLSI circuit design, including IC products such as processors, memory chips, and embedded systems, alongside the theoretical foundations of MOS transistors and CMOS inverters. It discusses the processes involved in CMOS fabrication, transistor sizing, and VLSI trends like Moore’s Law, which predicts the doubling of transistor density over time. Additionally, it includes a historical perspective on the evolution of transistors and integrated circuits, along with details of the author's research interests and publications.