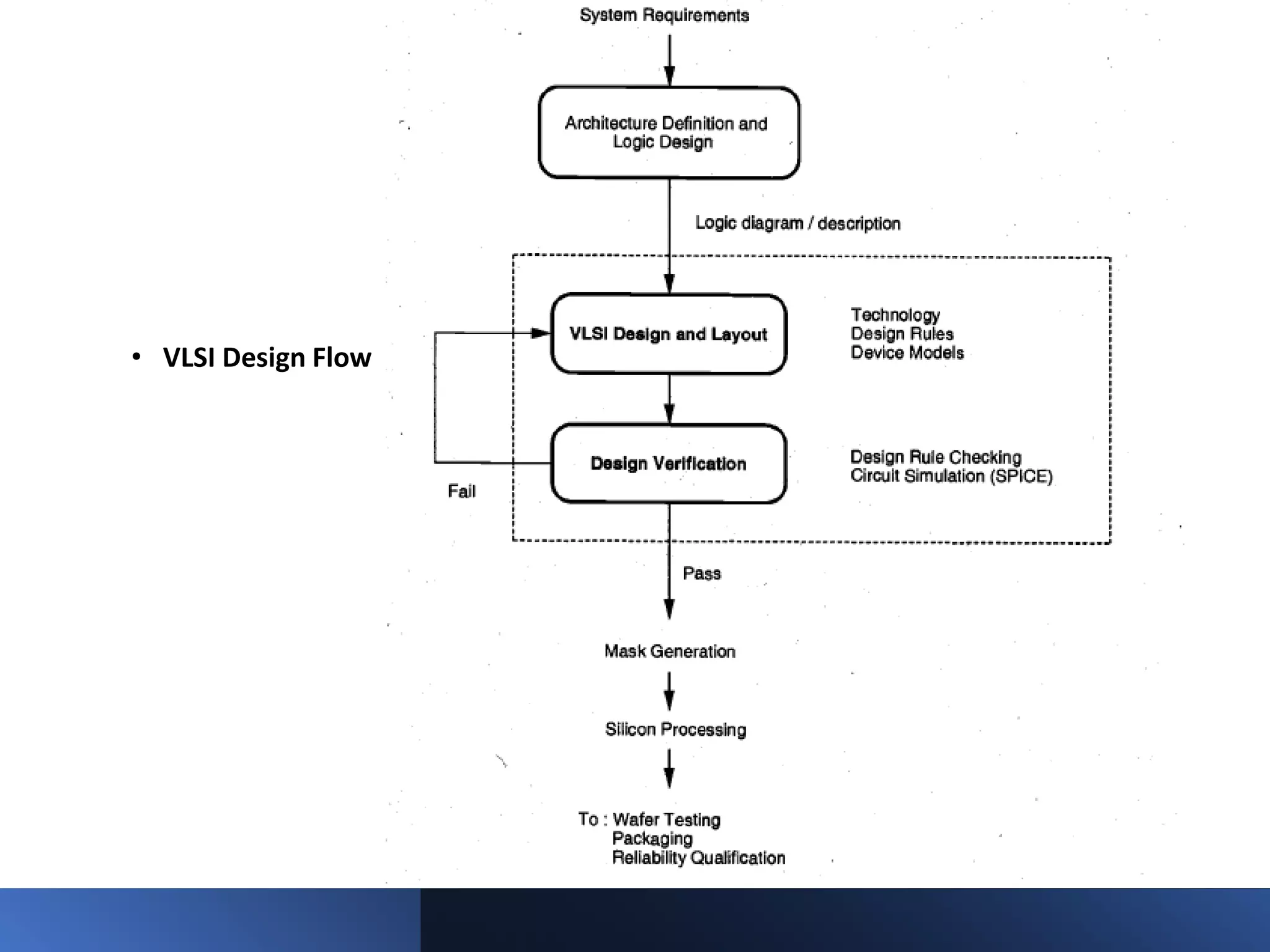

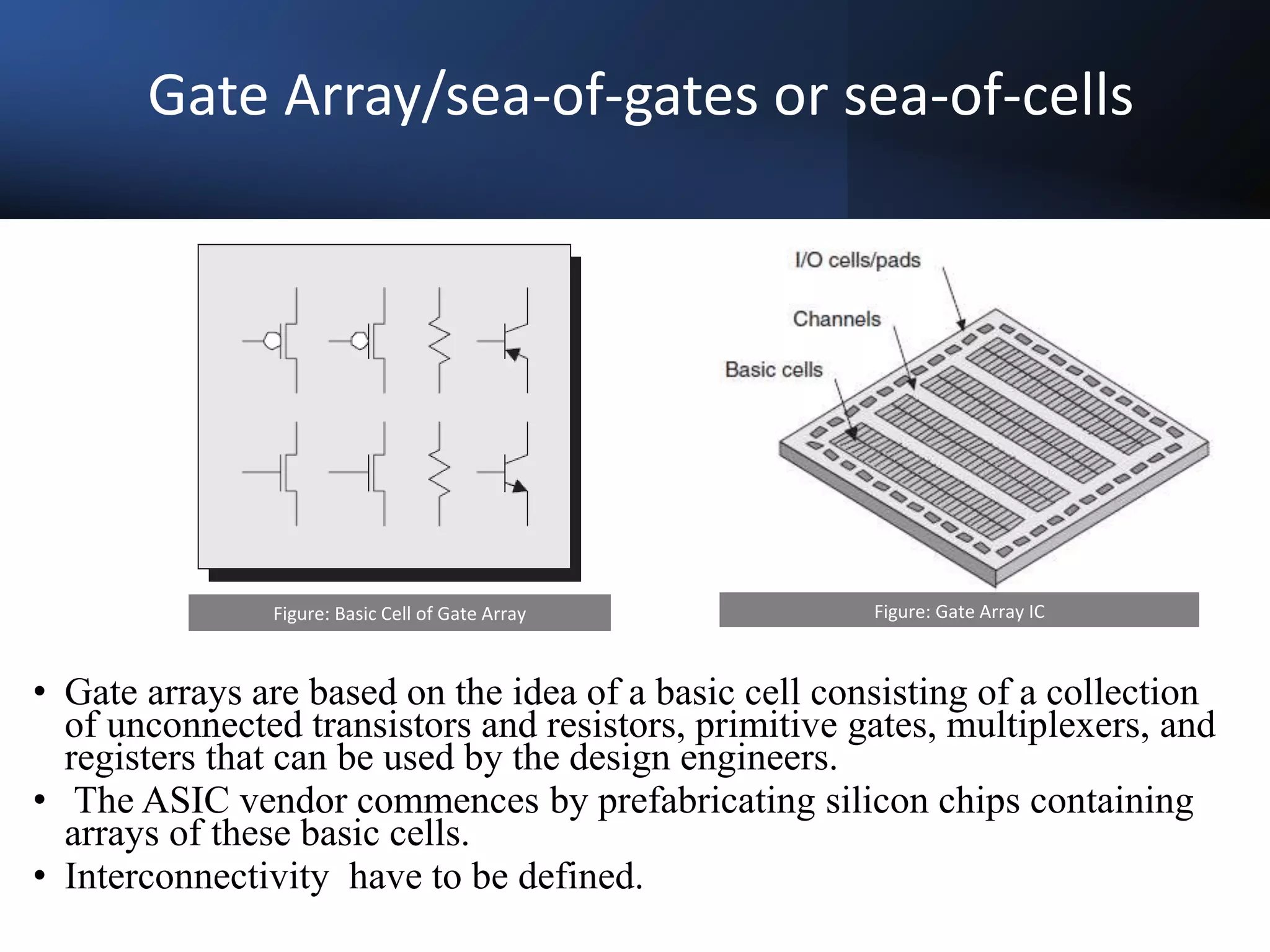

The document discusses the history and structure of MOSFET transistors. It begins with the conception of transistors in 1947 and integrated circuits in 1958. MOSFETs became important building blocks as they require almost zero control current when idle. The document outlines the development of MOSFET logic gates in 1963, and the scaling of integration from SSI to VLSI. It describes full custom and gate array ASIC design approaches using prefabricated cells.

![MOSFETs

The original idea of FET dated back to the German scientist Julius Lilienfield in

1925 [US patent 1,745,175] and a structure closely resembling the MOSFET

was proposed in 1935 by Oskar Heil [British patent 439,457], but materials

problems foiled early attempts to make functioning devices.

By the 1960s, Metal Oxide Semiconductor Field Effect Transistors (MOSFETs)

began to enter production.

MOSFETs offer the compelling advantage that they draw almost zero control

current while idle.

Metal Oxide Semiconductor Field Effect Transistors (MOSFETs)](https://image.slidesharecdn.com/lecture2sp23-230611062410-a1723d09/75/VLSI-Trends-pptx-11-2048.jpg)

![Key Developments

In 1963, Frank Wanlass at Fairchild described the first logic gates using

MOSFETs [Wanlass63].

Fairchild’s gates used both nMOS and pMOS transistors, earning the

name Complementary Metal Oxide Semiconductor, or CMOS.

The circuits used discrete MOSFET’s but consumed only nanowatts of

power, six orders of magnitude less than their bipolar counterparts.

With the development of the silicon planar process, MOS integrated

circuits became attractive for their low cost because the fabrication process

was simpler](https://image.slidesharecdn.com/lecture2sp23-230611062410-a1723d09/75/VLSI-Trends-pptx-12-2048.jpg)