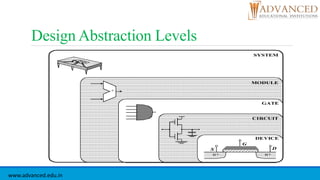

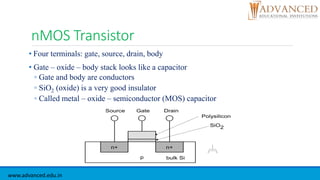

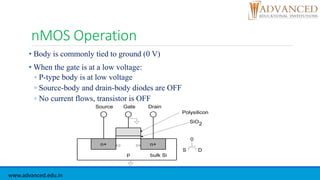

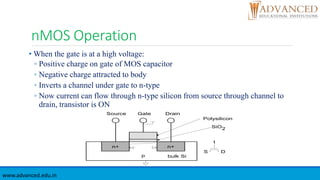

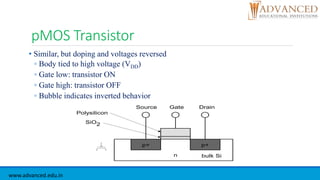

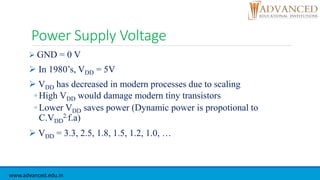

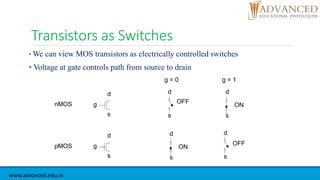

The document provides an overview of VLSI (Very Large Scale Integration) technology, detailing its design process, semiconductor properties, and the operation of different transistor types like NMOS and PMOS. It highlights the advantages of VLSI, such as improved performance, lower power consumption, and cost-effectiveness, in the context of modern electronics. Key topics include fabrication technology, CMOS technology, and various applications of VLSI in microprocessors and memory systems.