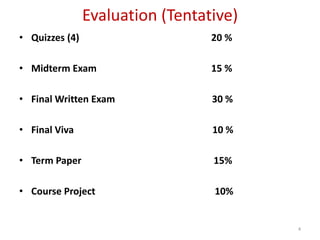

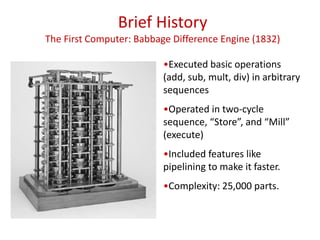

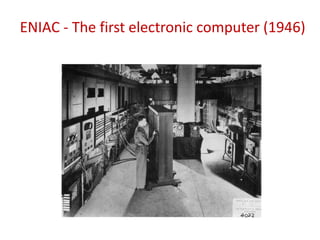

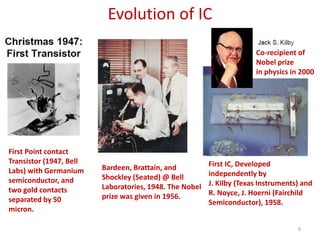

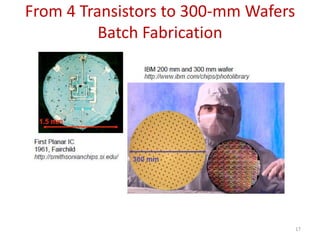

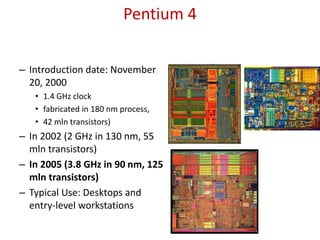

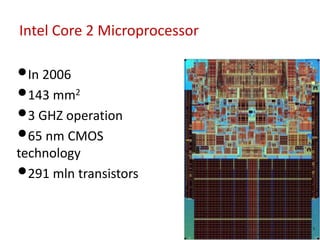

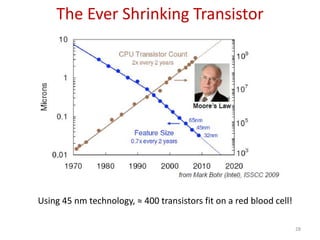

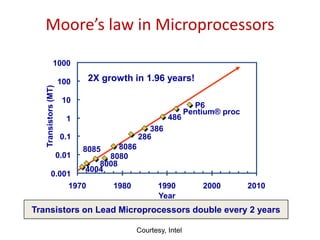

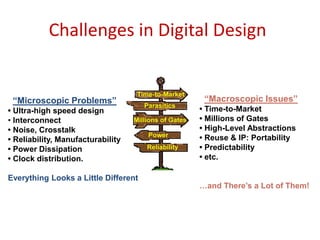

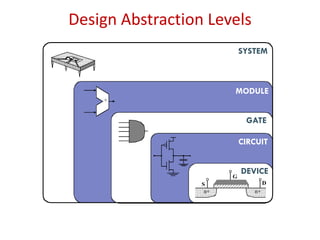

This document provides an introduction to the VLSI Design course EEL3320. It discusses the evolution of integrated circuits from early computers to modern microprocessors containing billions of transistors. The course will cover CMOS device operation, circuit design, sequential elements, and design methodologies. Students will learn how to design and optimize digital circuits for cost, speed, power, and reliability. The document outlines the course content, textbooks, evaluation criteria, and instructor details.