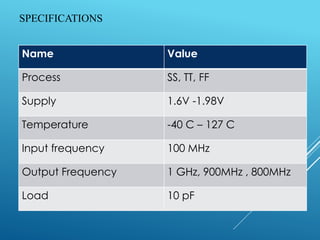

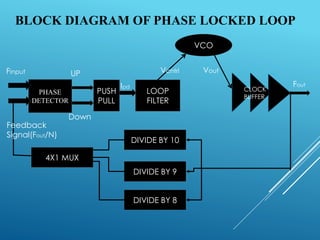

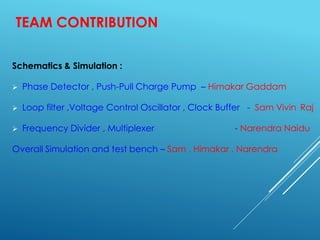

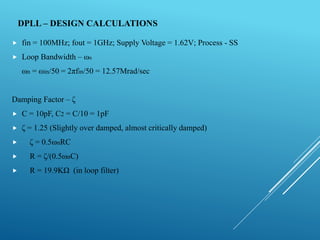

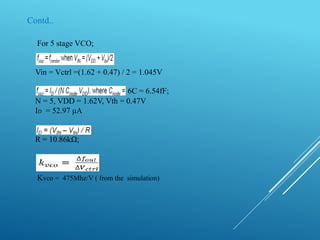

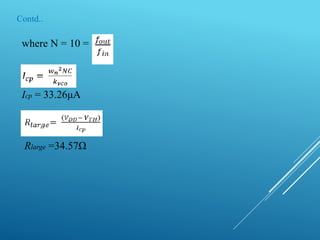

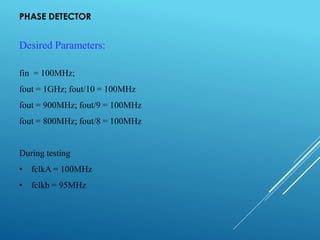

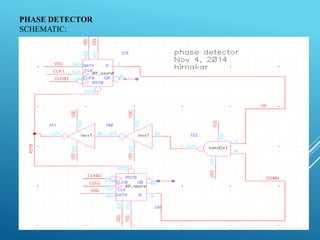

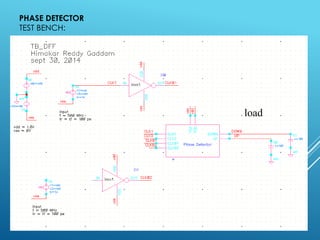

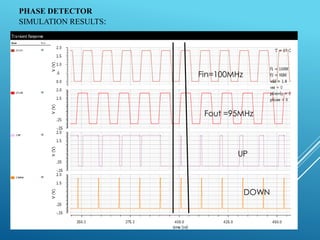

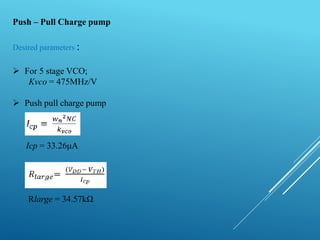

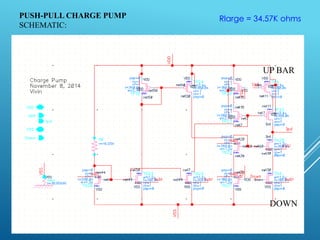

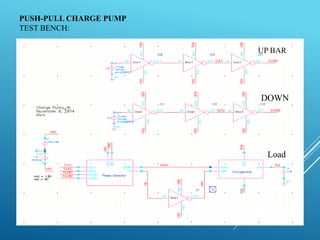

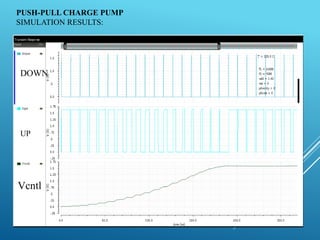

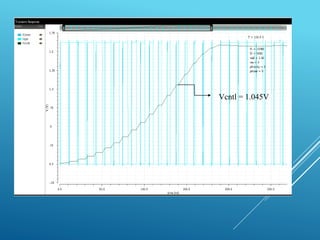

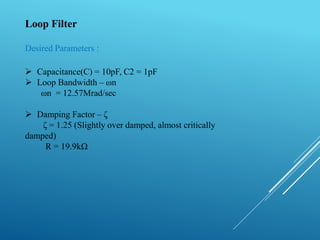

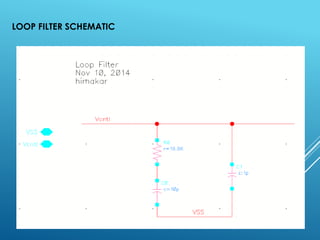

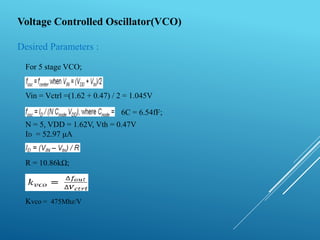

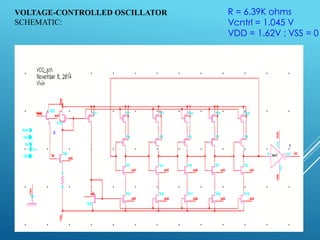

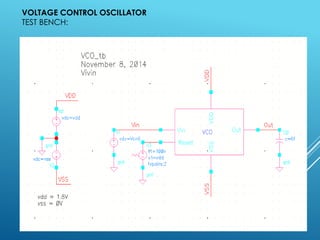

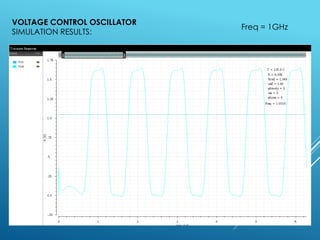

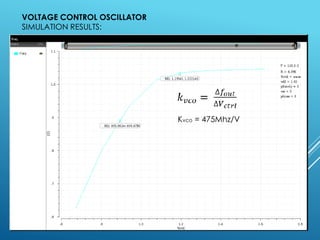

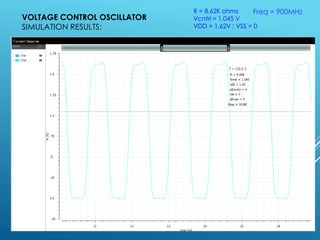

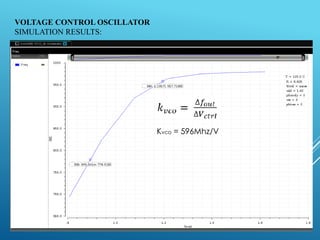

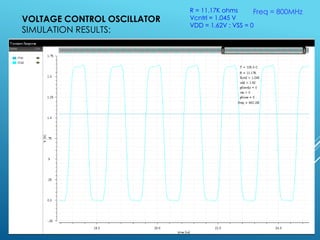

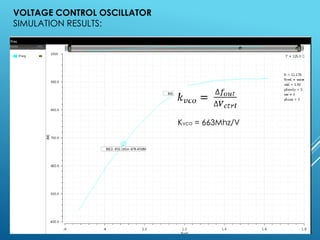

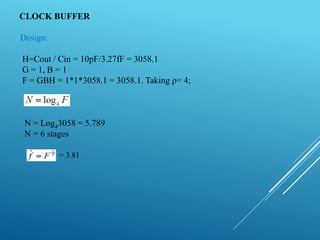

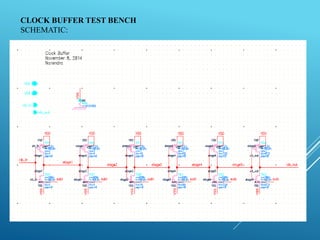

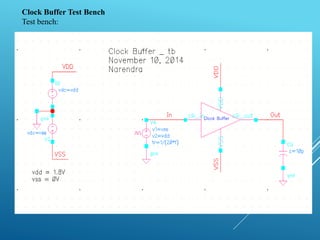

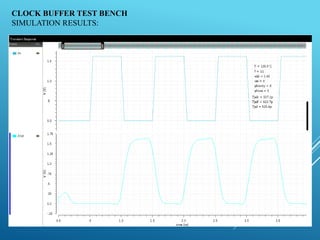

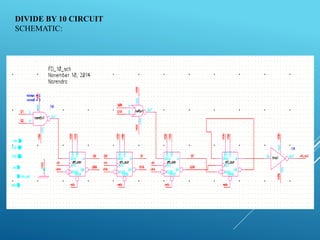

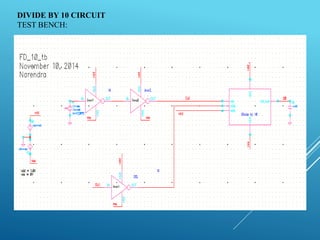

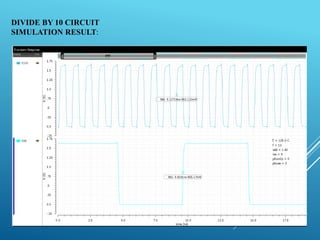

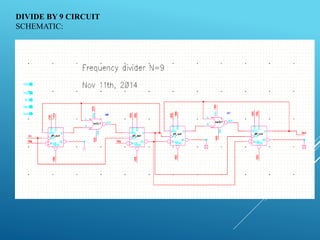

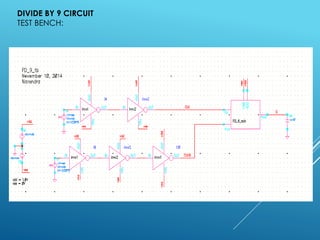

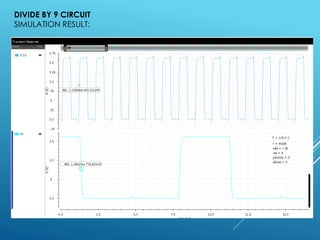

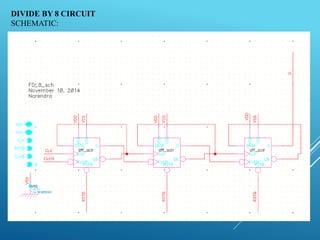

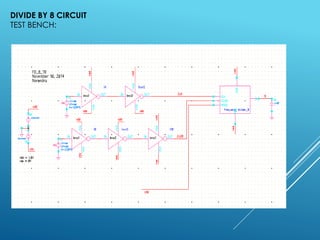

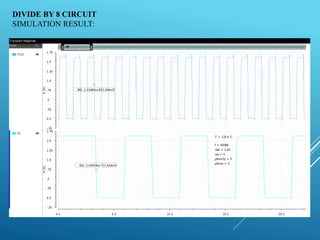

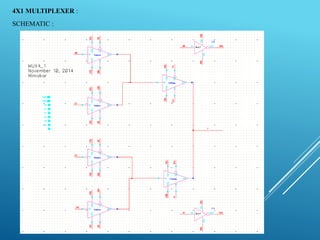

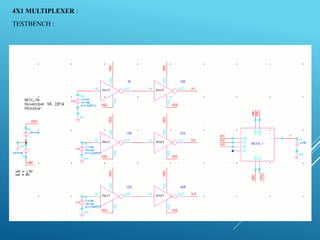

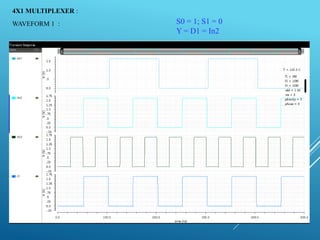

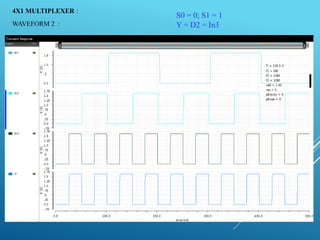

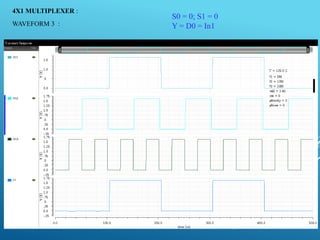

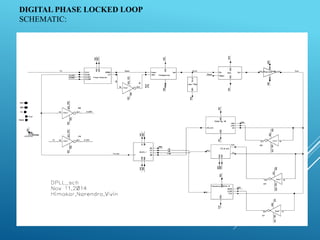

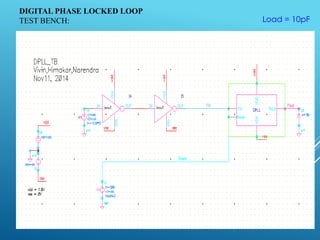

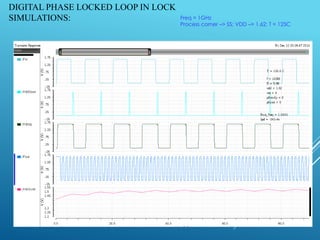

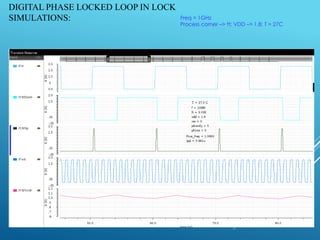

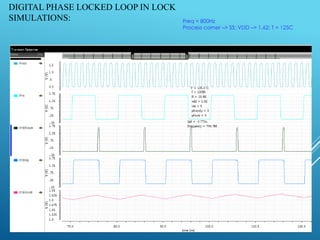

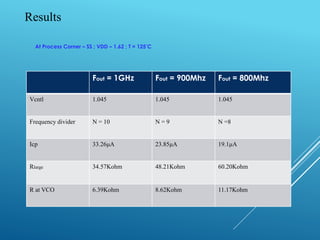

This document describes the design of a digital phase locked loop (DPLL) circuit. It includes specifications for operating frequency ranges from 100MHz to 1GHz, block diagrams of the major components, schematics and test benches of the phase detector, charge pump, loop filter, voltage controlled oscillator (VCO), frequency dividers, and multiplexer. Simulation results show the DPLL locking at output frequencies of 1GHz, 900MHz and 800MHz for different control voltages and component values. The team contributions and challenges in designing and simulating the full DPLL are also noted.