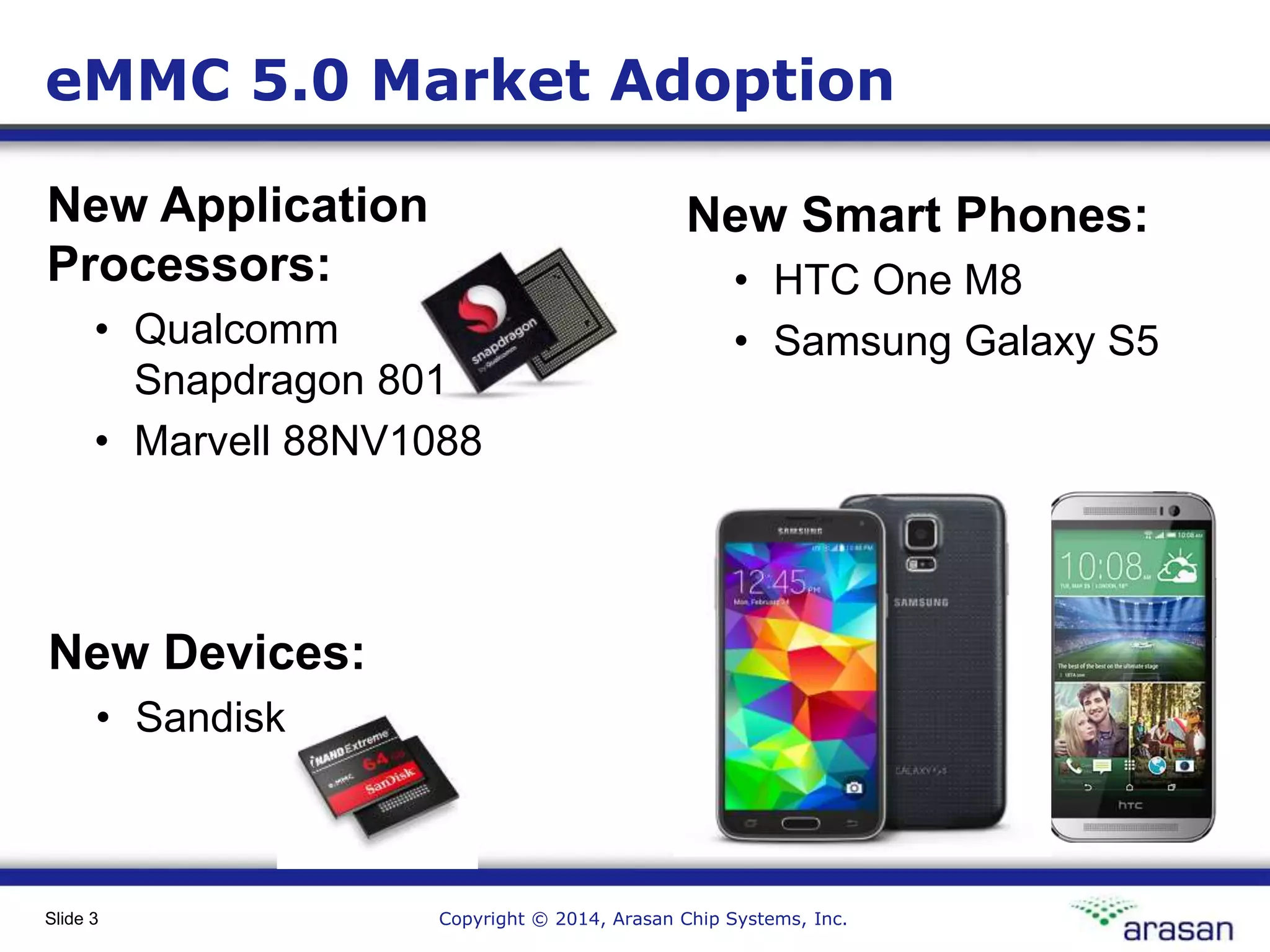

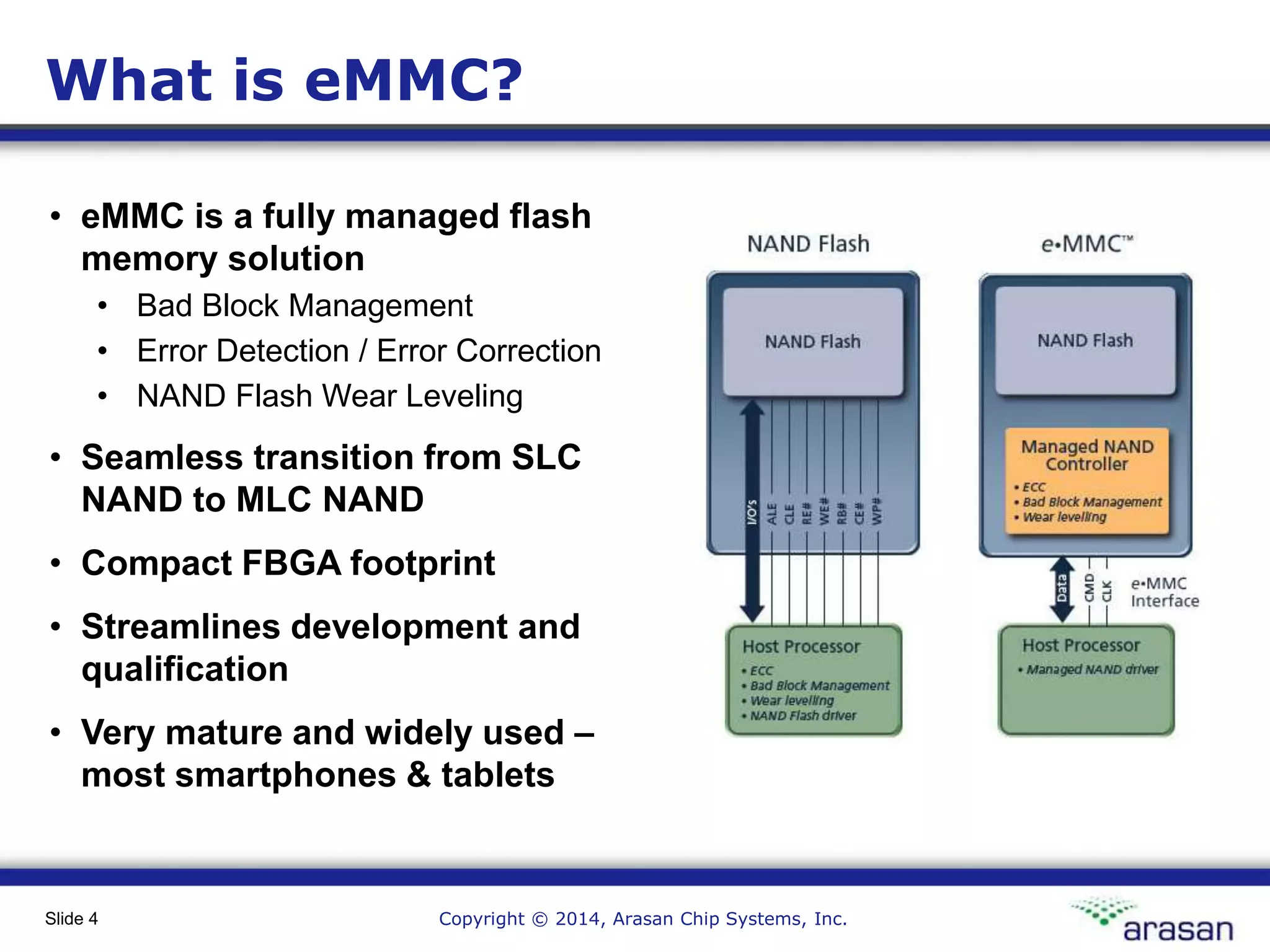

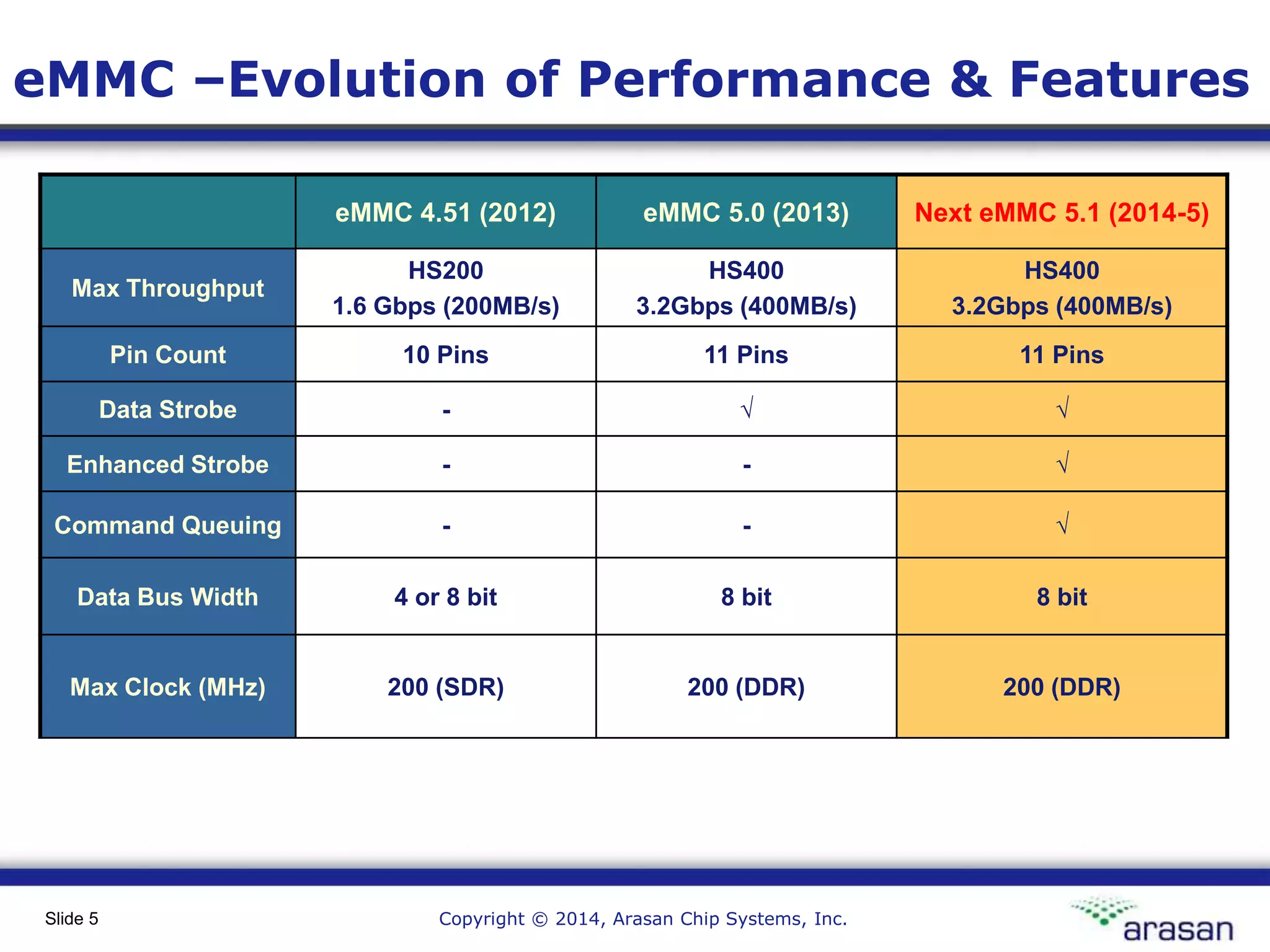

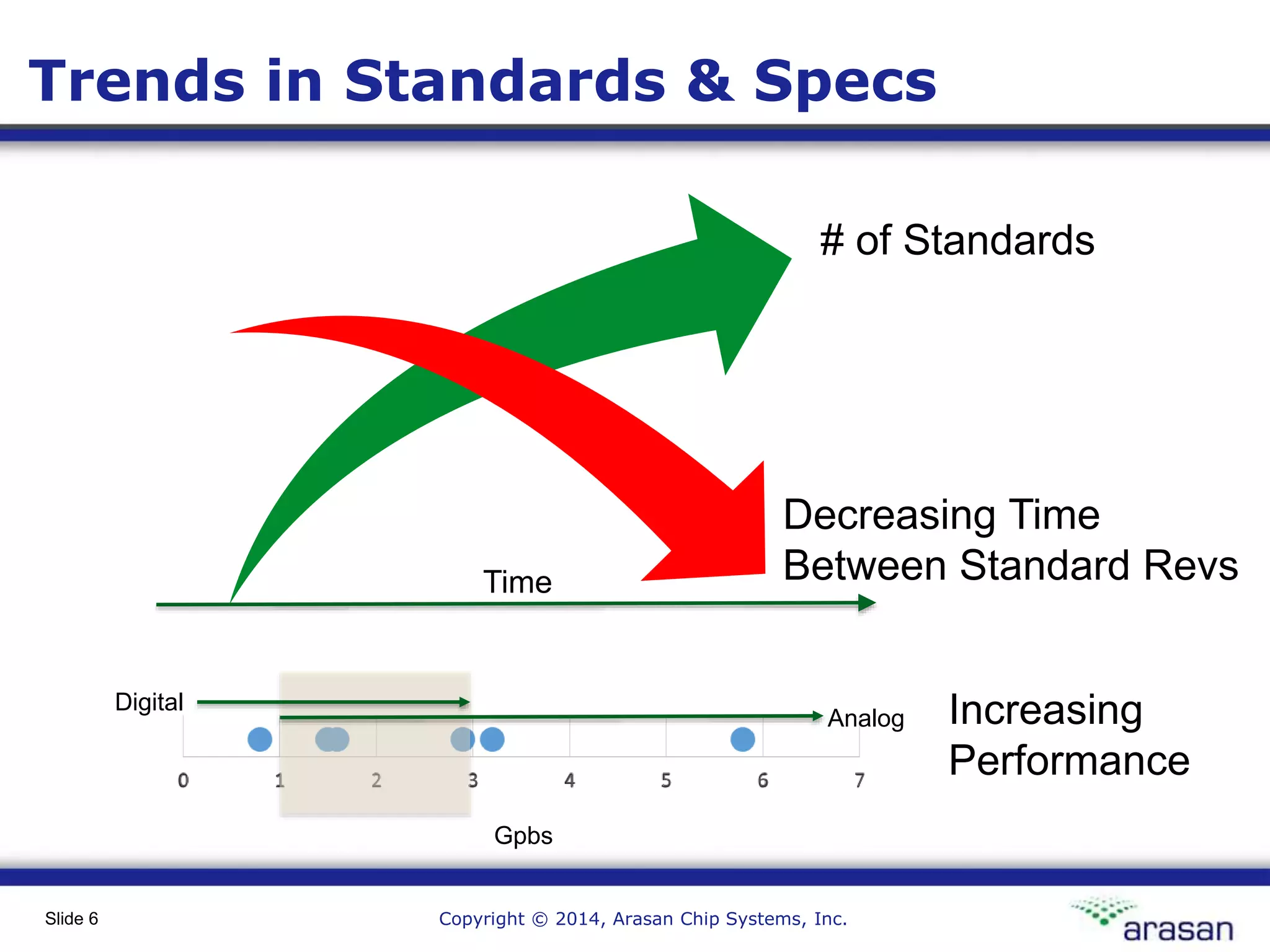

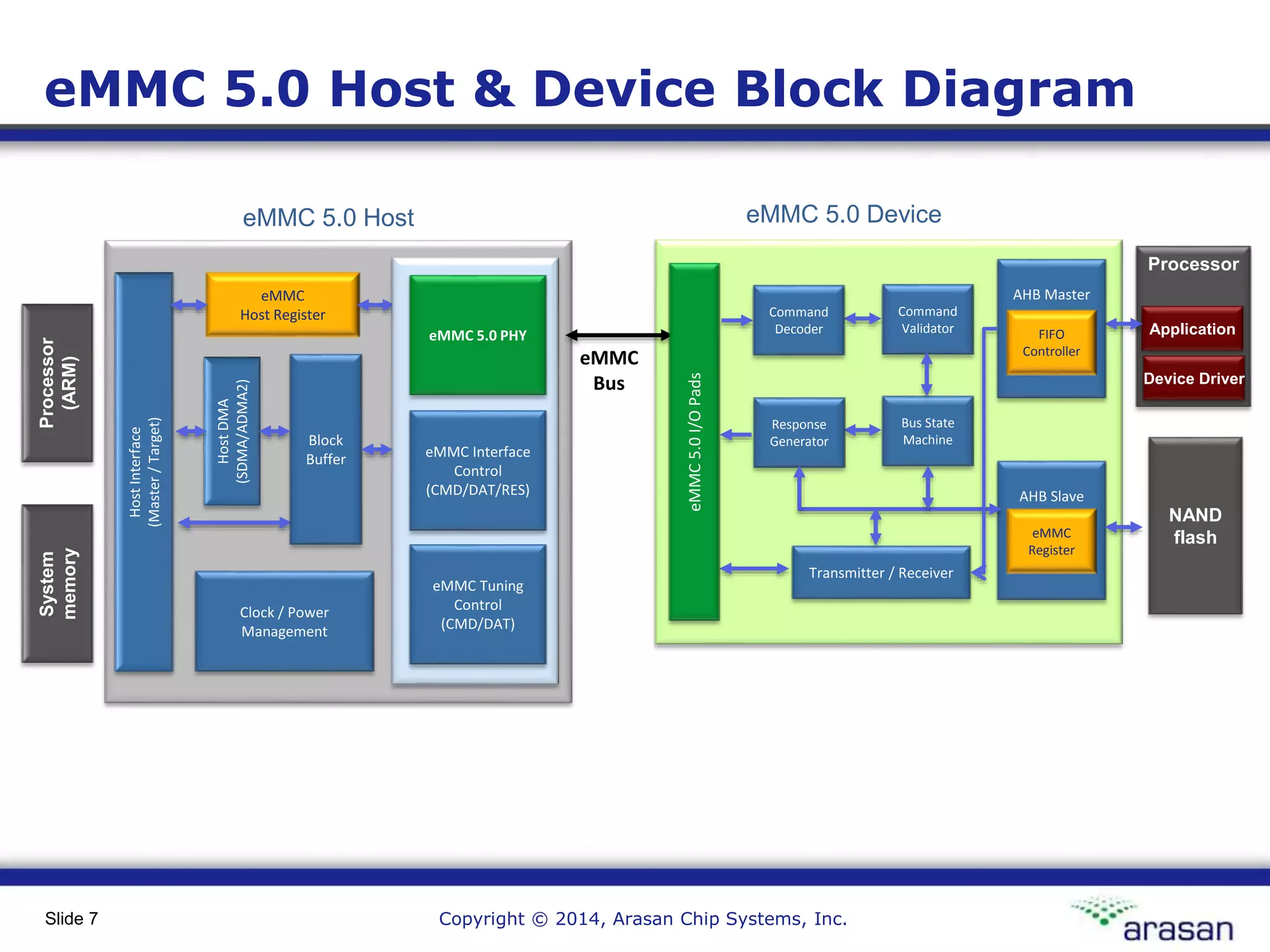

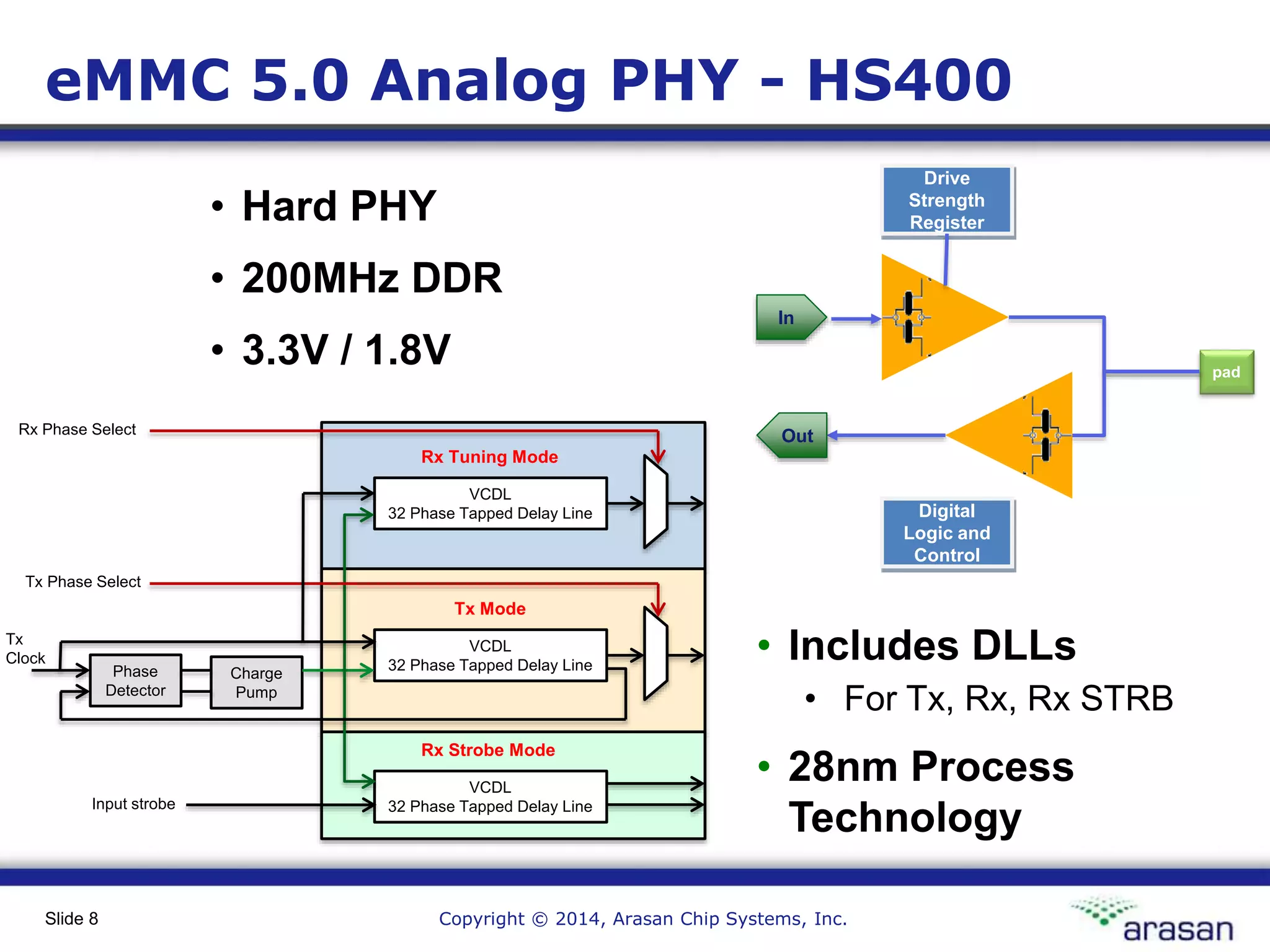

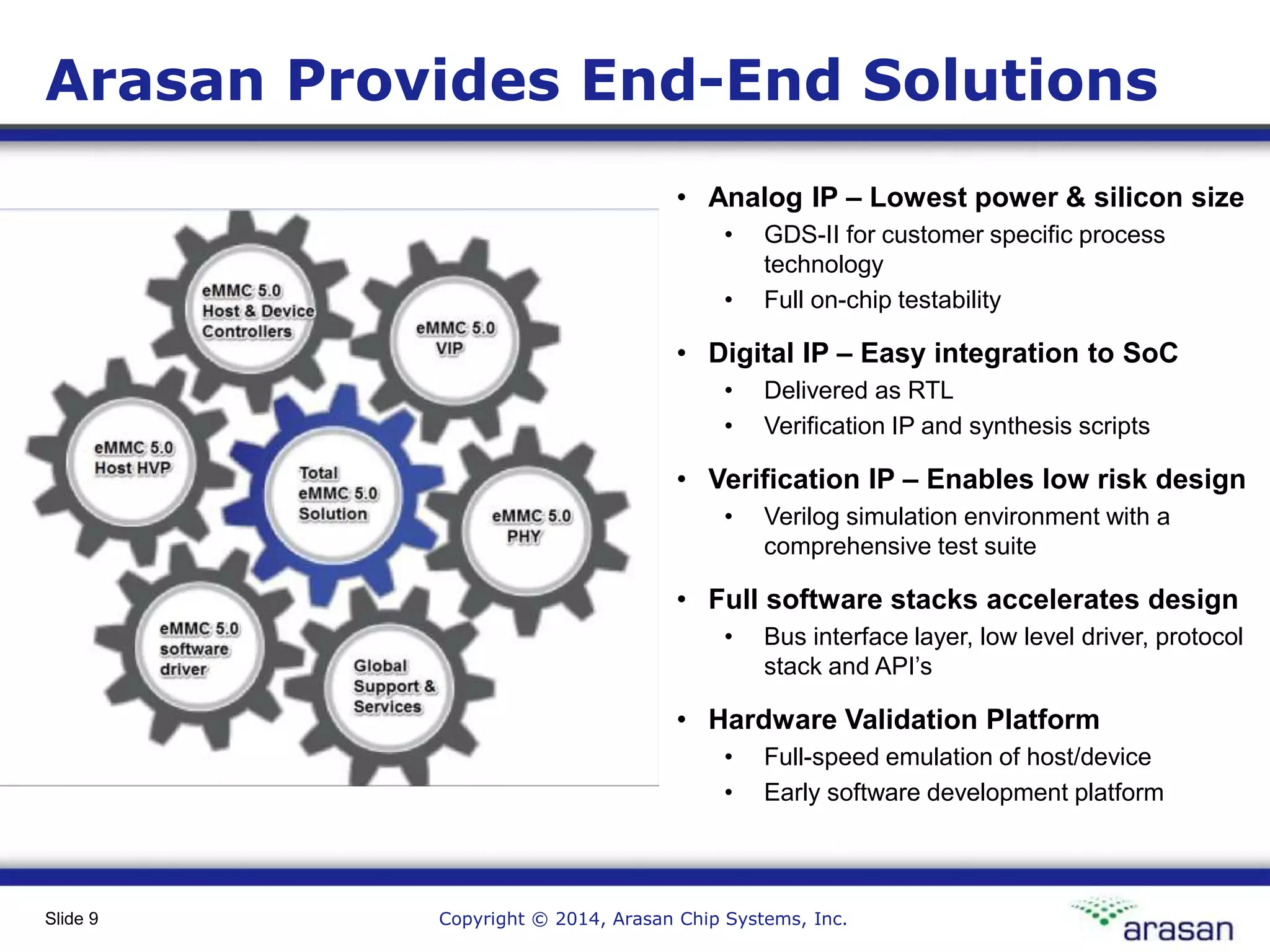

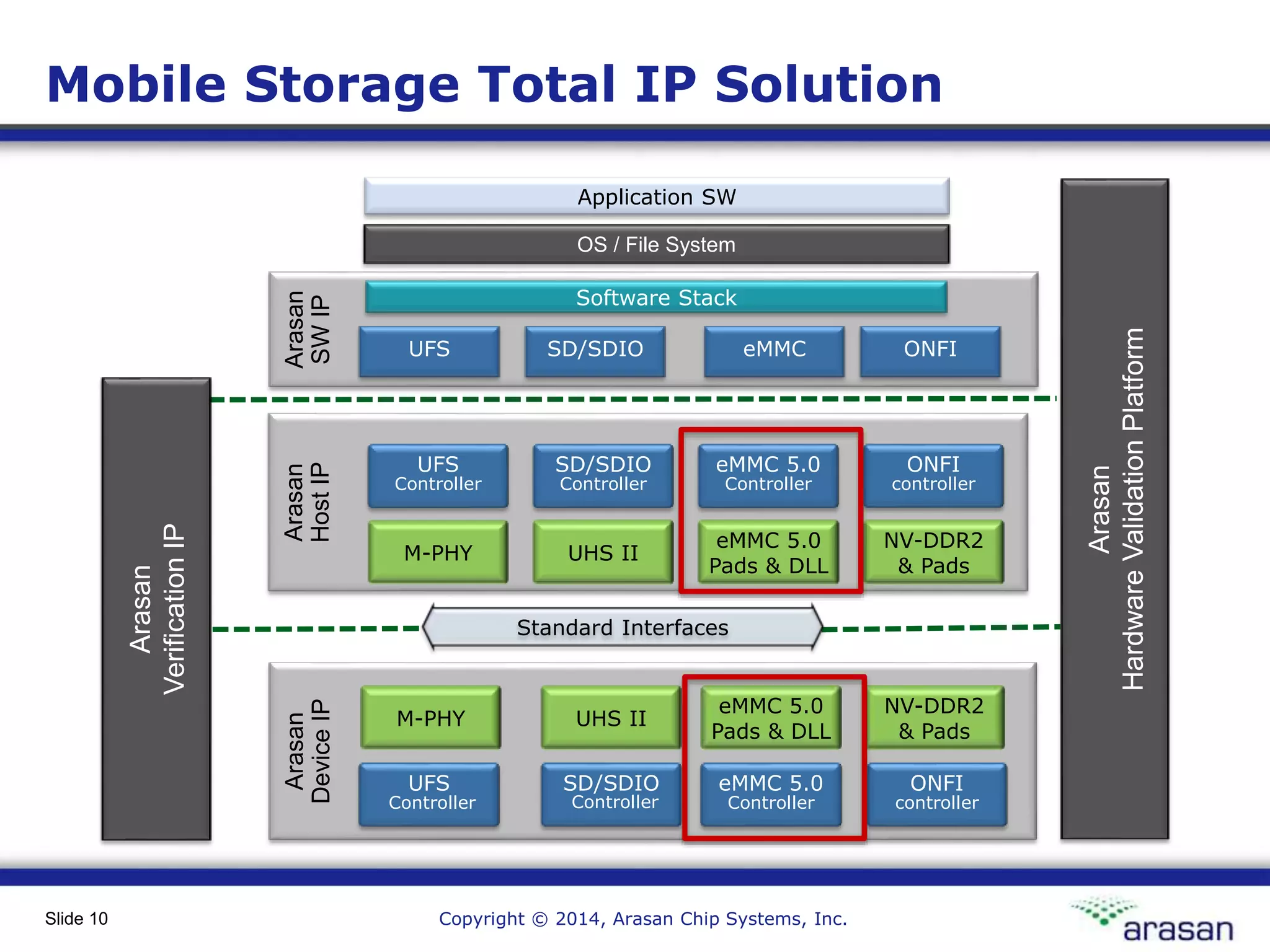

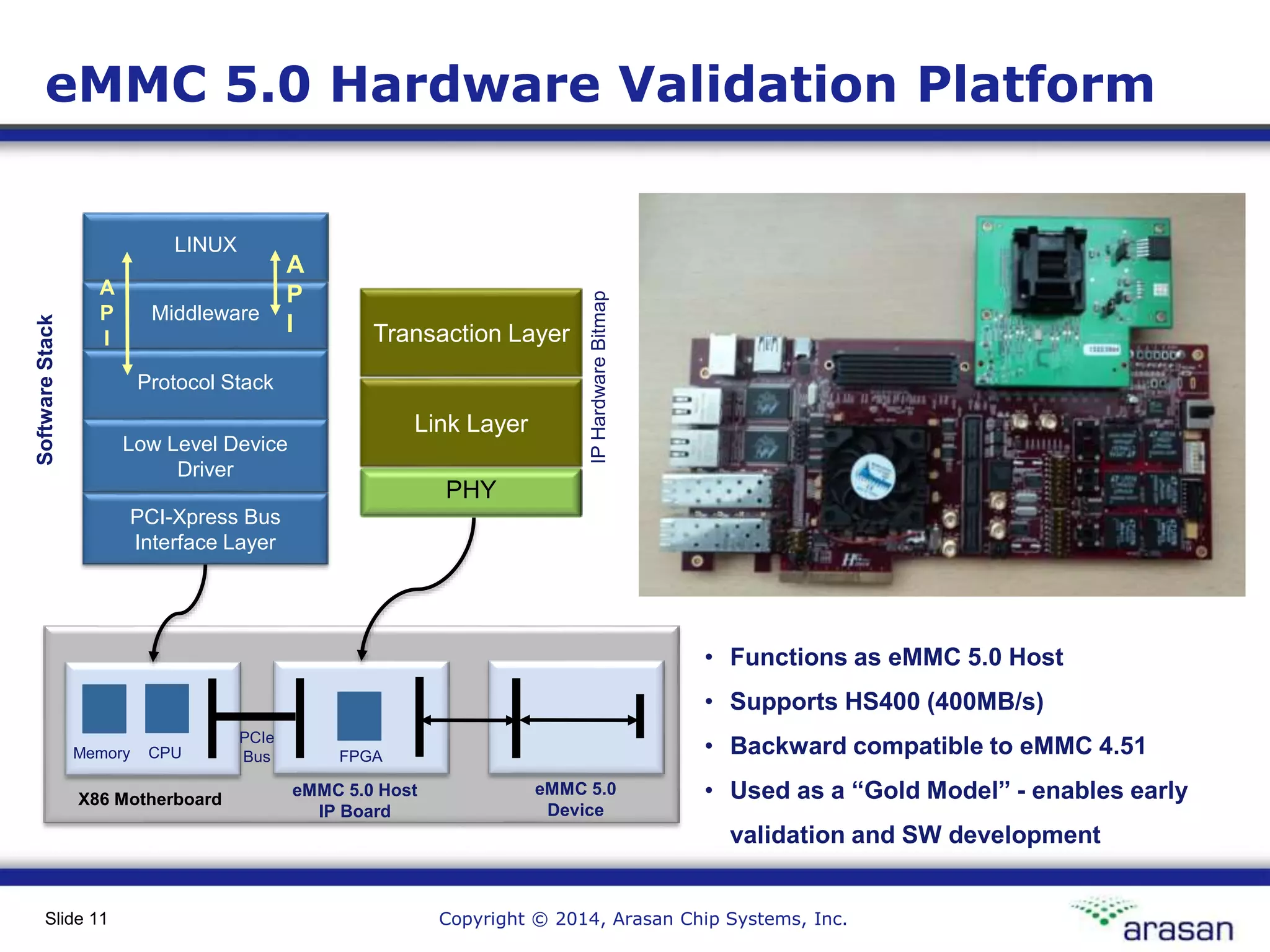

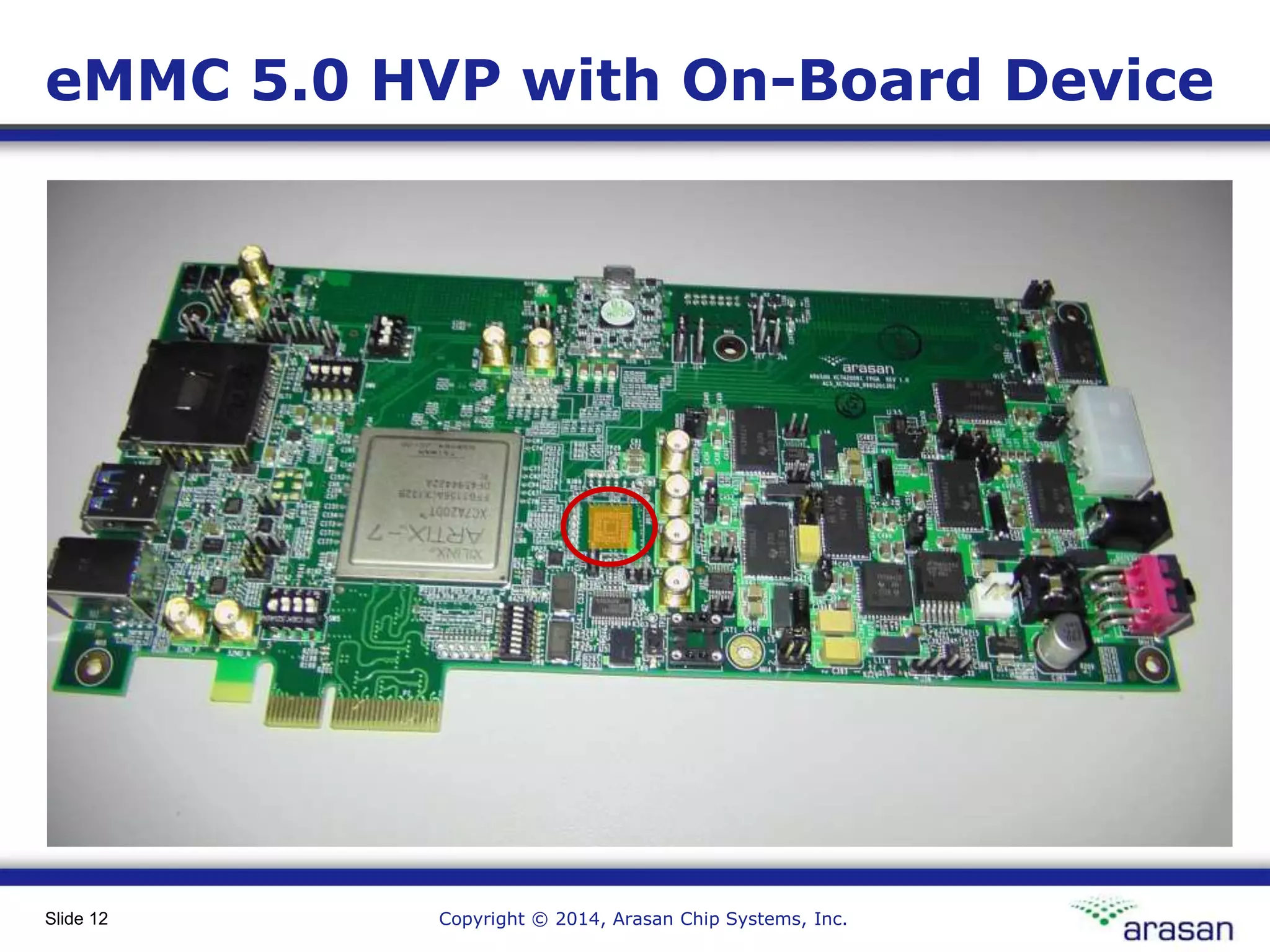

The document presents an overview of eMMC 5.0, highlighting its market adoption with new processors and smartphones, and its evolution in performance and features compared to previous versions. It details Arasan's total IP solution for eMMC 5.0, including analog and digital IP offerings, hardware validation platforms, and support for various applications. Arasan is positioned as a leading provider in the space, with ongoing commitments to standards and a robust shipping portfolio for eMMC 5.0 technologies.