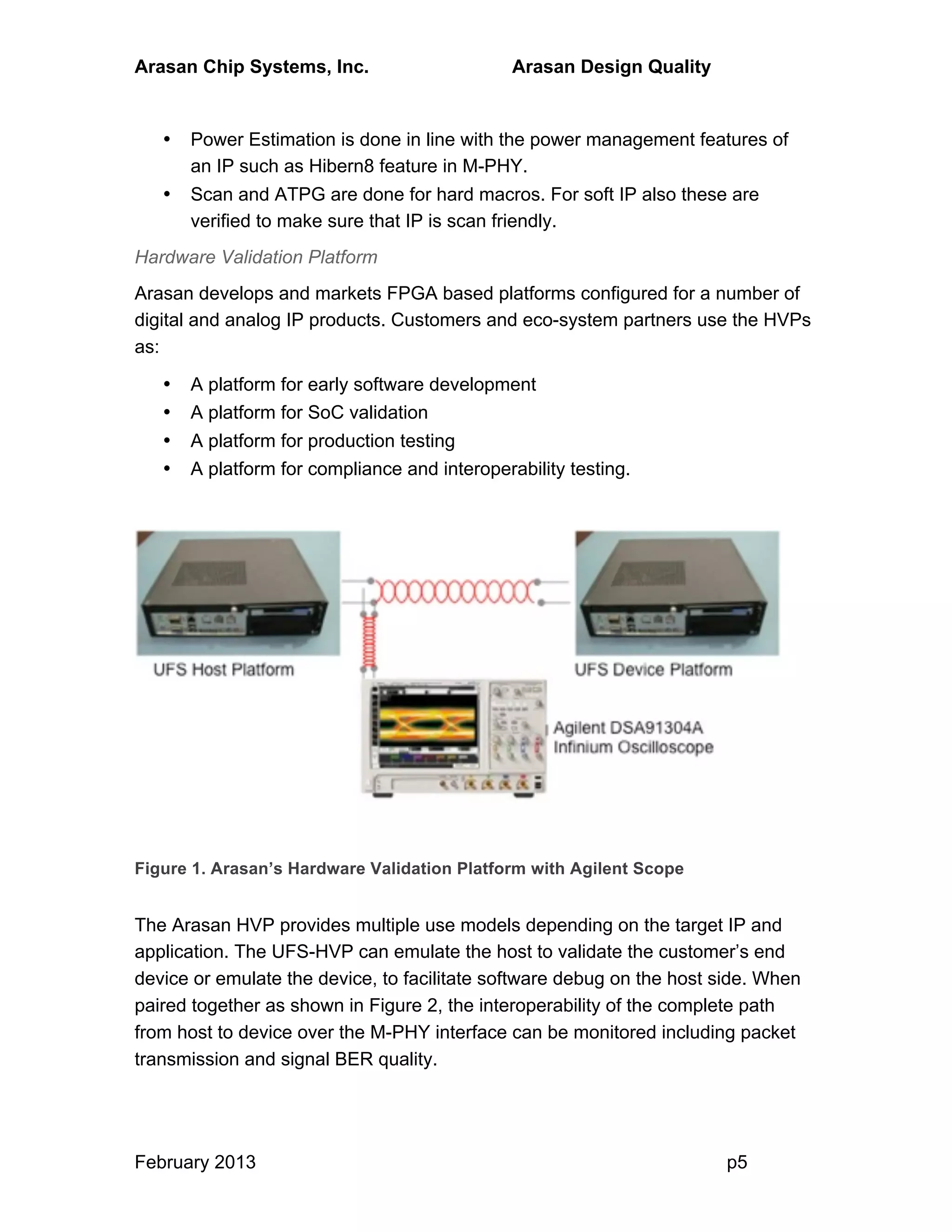

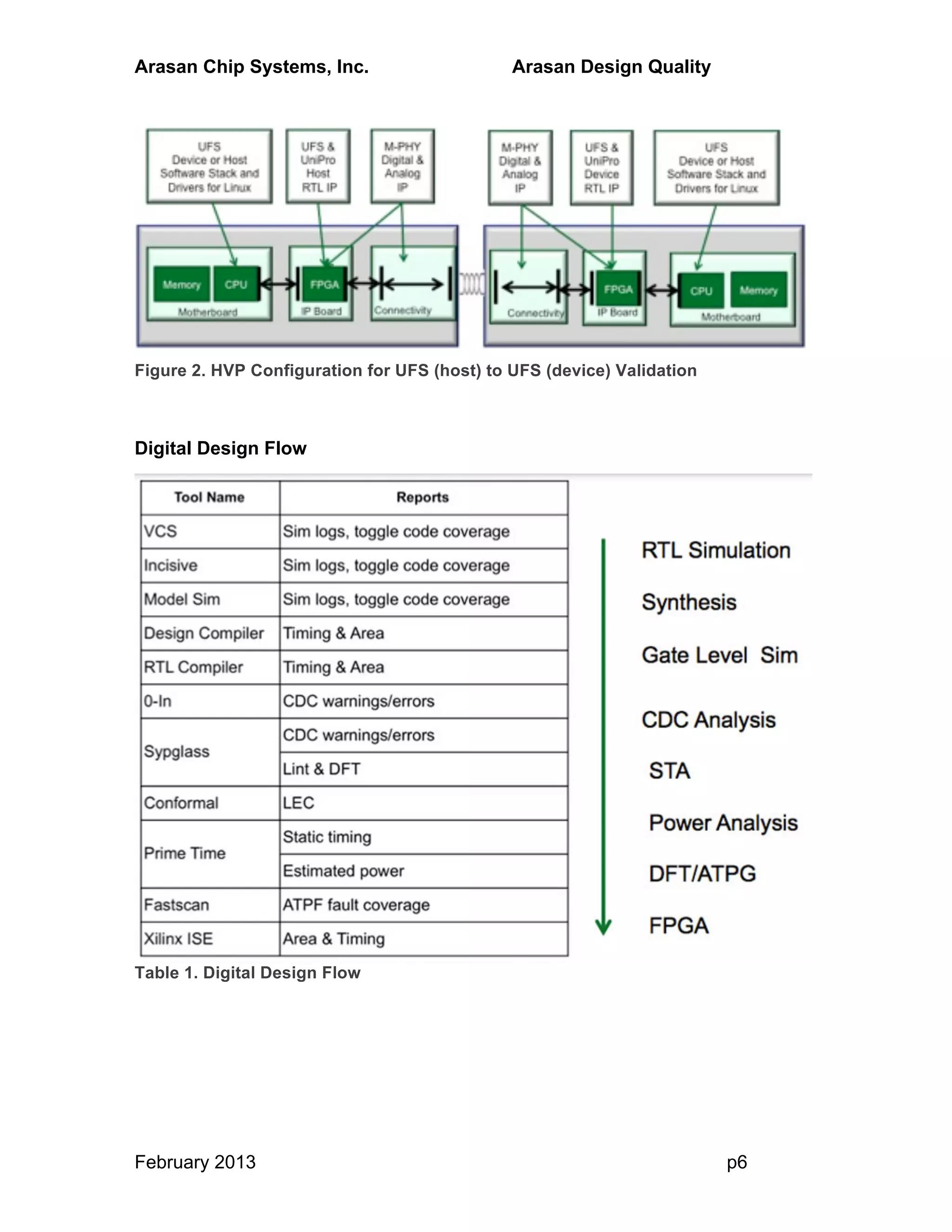

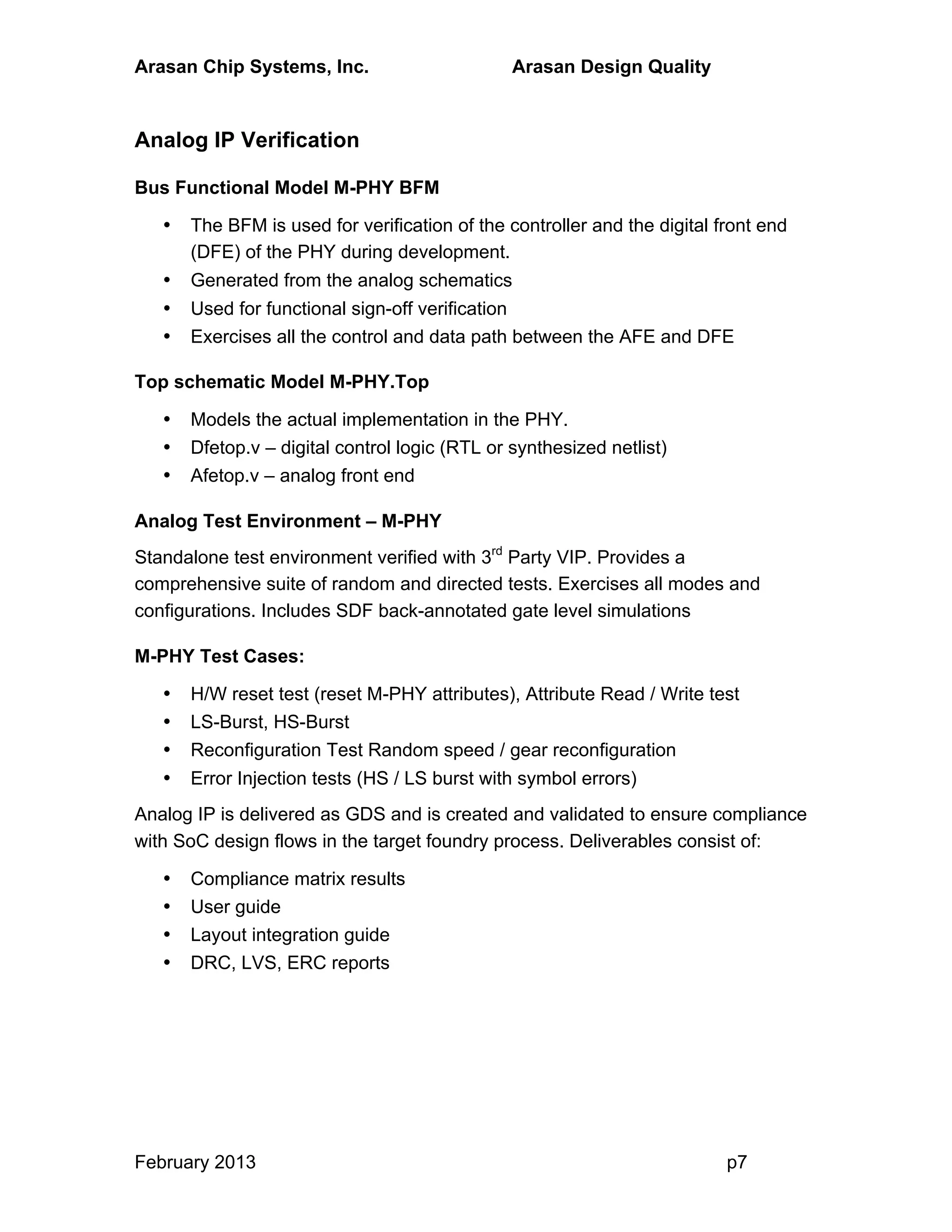

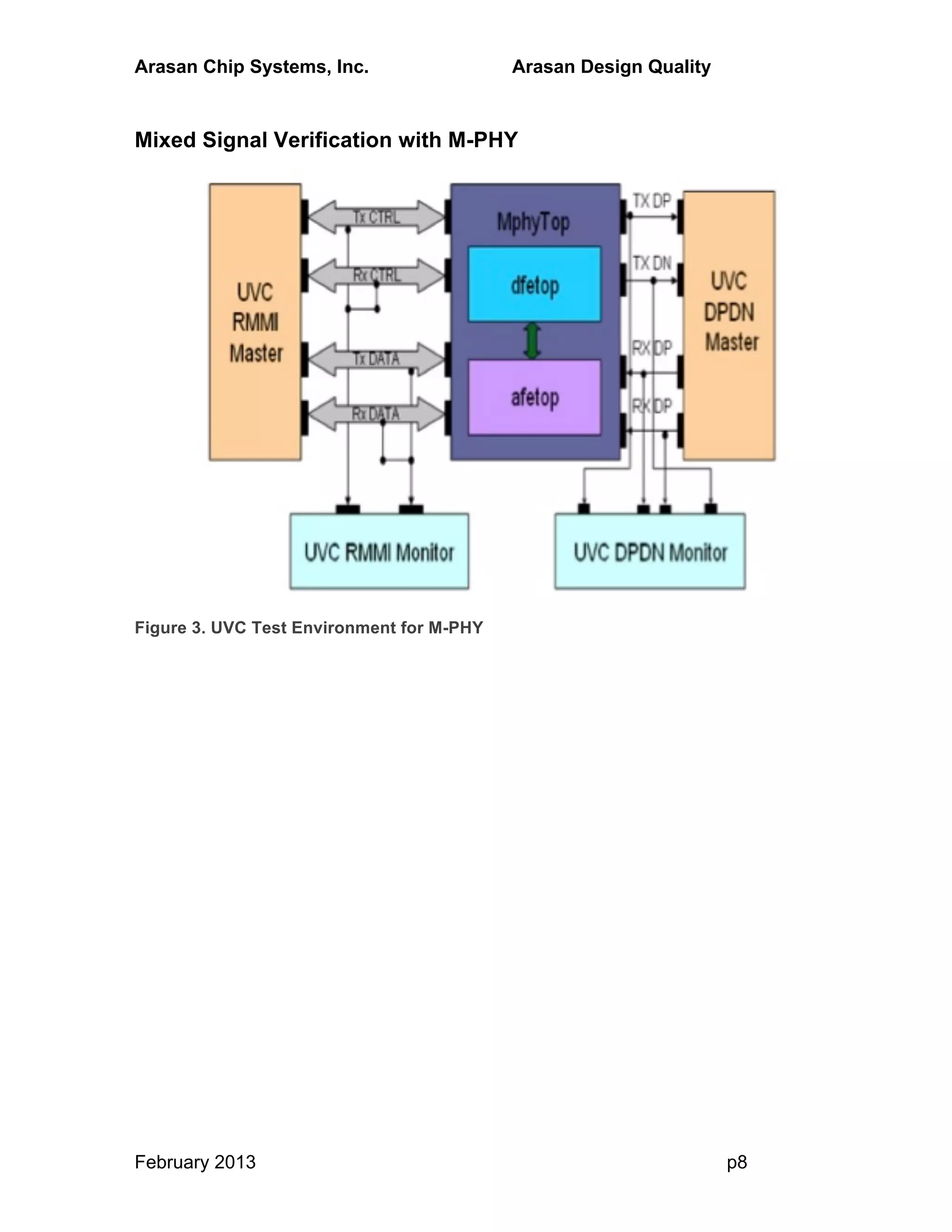

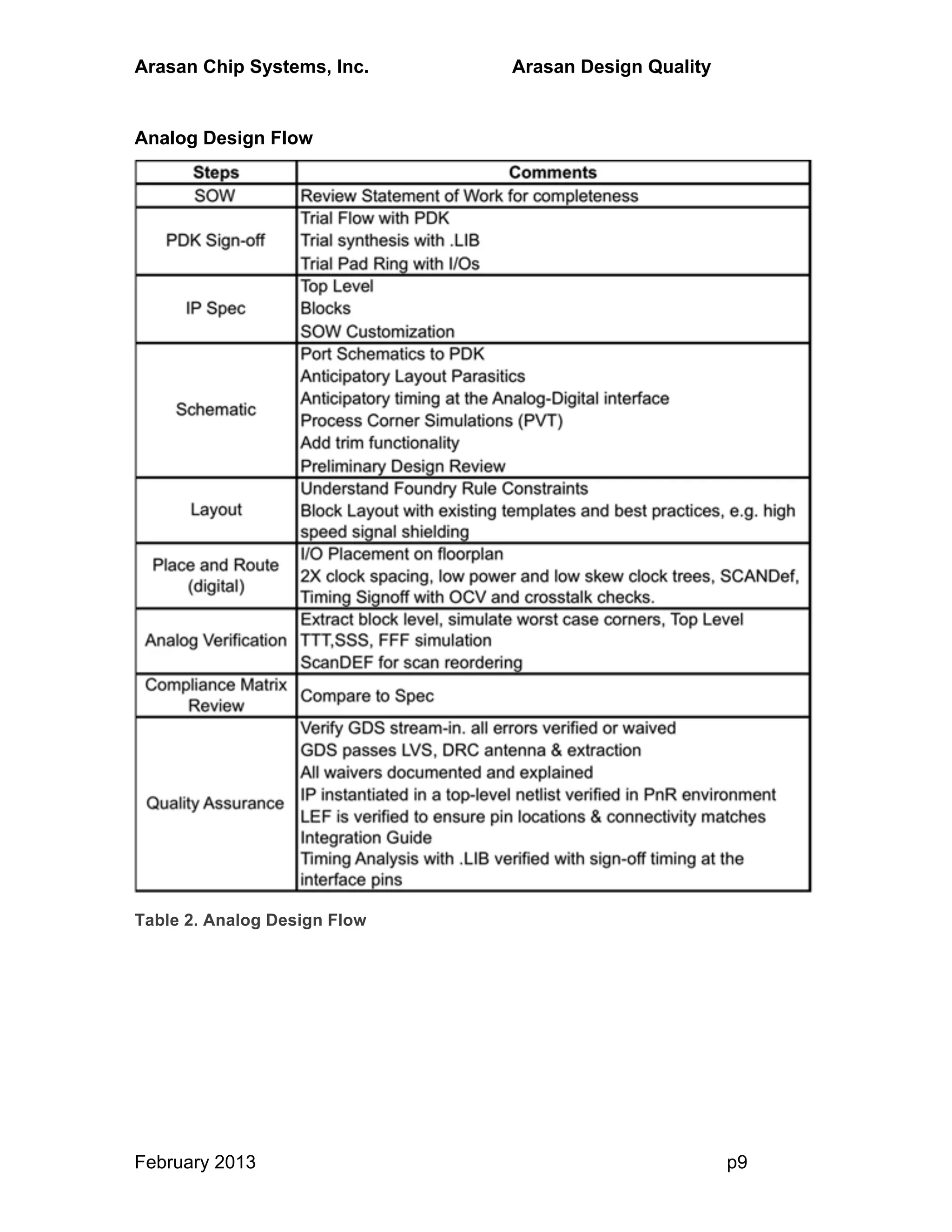

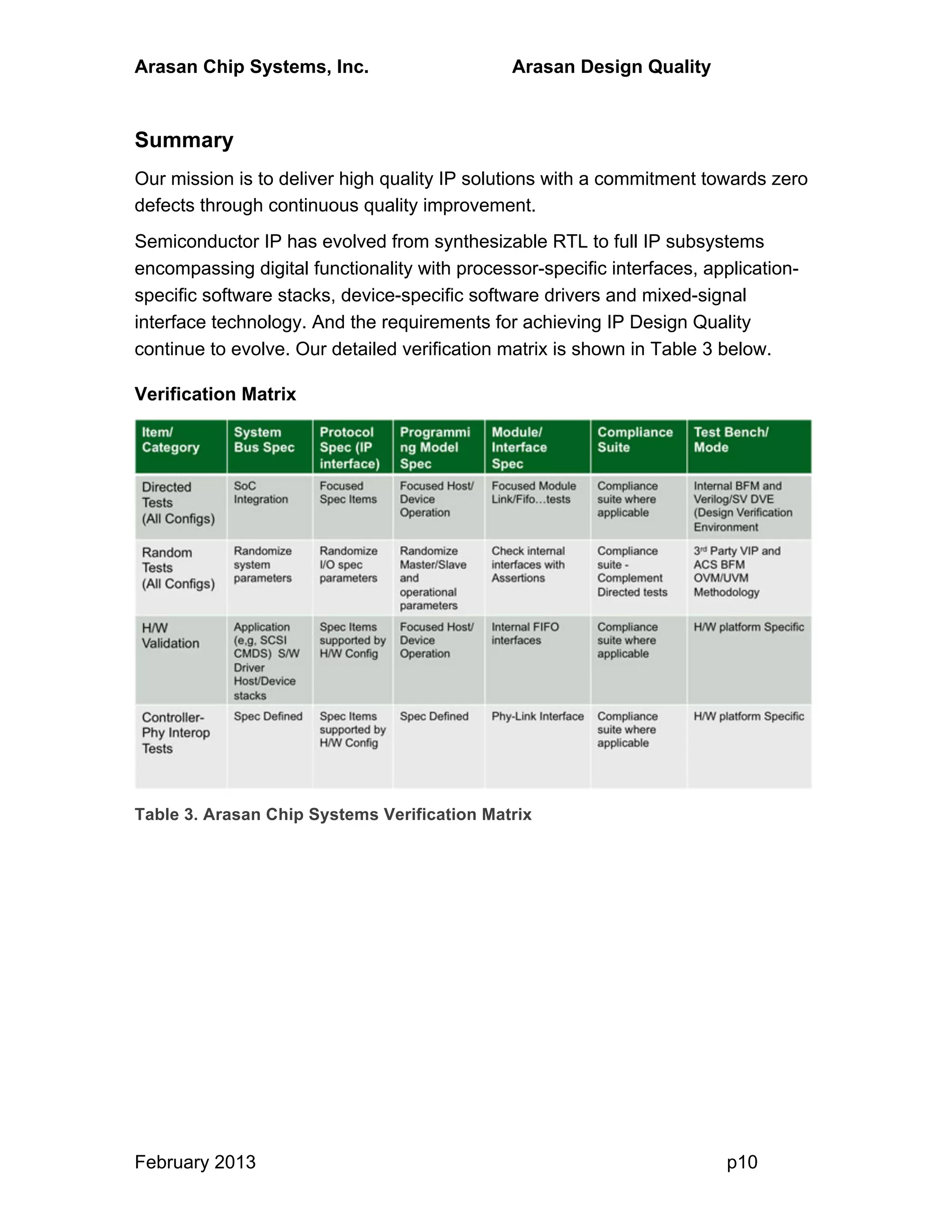

Arasan Chip Systems provides high quality IP solutions through a rigorous verification process. They verify digital IP through functional coverage, system simulations, and hardware validation. They also verify analog IP compliance and mixed-signal operation. Their process involves verifying IP at the subsystem level across digital, analog, and software domains to ensure everything works together seamlessly for customers.