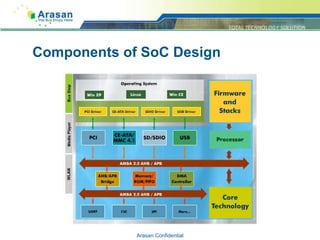

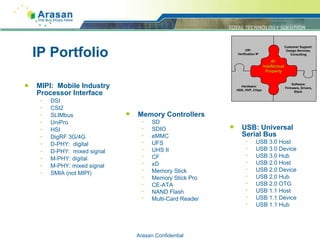

The document discusses the need for total IP solutions in modern SoC design. It describes how SoC complexity requires the use of third-party IP cores, analog front-ends (PHYs), and complete solutions including RTL IP, PHY IP, verification IP, software stacks, and hardware platforms. It provides Arasan Chip Systems as a case study, outlining their portfolio of standards-based IP, verification tools, hardware development kits, and design services to deliver comprehensive IP solutions.