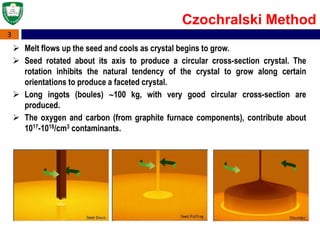

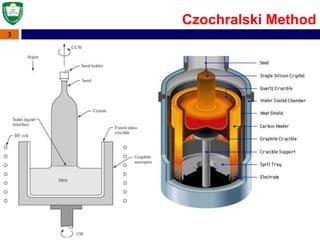

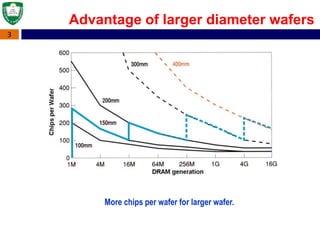

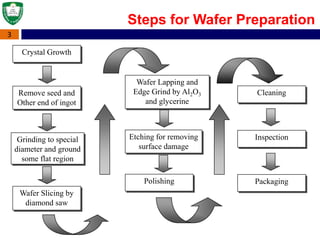

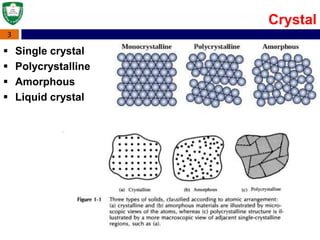

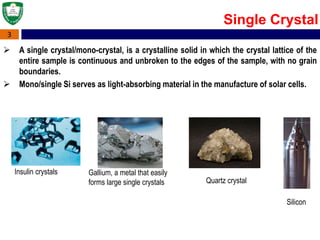

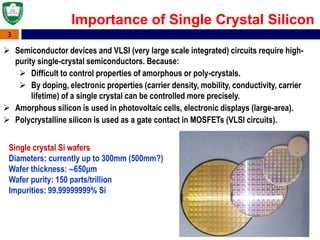

Crystal structures can be single crystal, polycrystalline, or amorphous. Single crystal silicon is used to manufacture solar cells and semiconductors due to its precise electronic properties. The Czochralski method is commonly used to grow large single crystal silicon ingots from melted, purified silicon in quartz crucibles. The ingots are sliced, polished, and cleaned to produce thin round wafers for semiconductor fabrication. Larger diameter wafers allow more chips to be produced from each wafer, increasing manufacturing efficiency.

![3

Crystals are

characterized by a unit

cell which repeats in the

x, y, z directions.

Planes and directions

are defined using an x,

y, z coordinate system.

[111] direction is defined

by a vector having

components of 1 unit in

x, y and z.

Planes are defined by

Miller indices -

reciprocals of the

intercepts of the plane

with the x, y and z axes.

Crystallography](https://image.slidesharecdn.com/1550462065ee4121lecture-2-190527091359/85/Wafer-Fabrication-CZ-Method-ABU-SYED-KUET-11-320.jpg)