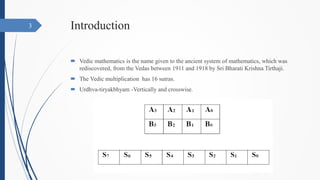

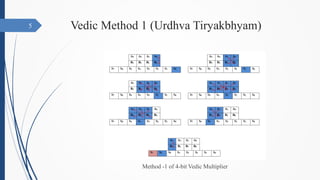

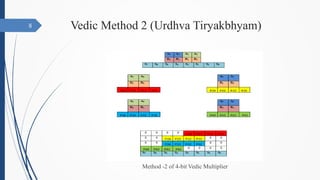

This document presents VHDL code for a Vedic multiplier with minimum delay architecture. It introduces the Vedic multiplication method of Urdhva-tiryakbhyam, which means vertically and crosswise. Two architectures are presented based on this method, with the second architecture aimed at reducing hardware. Delay calculations are shown for both architectures, with Architecture 1 of Method 1 having the lowest delay. In conclusion, the architecture of Method 1 with reduced hardware is found to have the lowest delay.