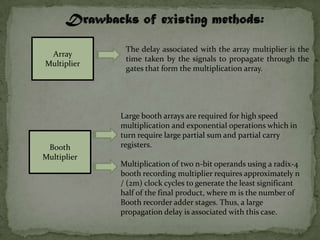

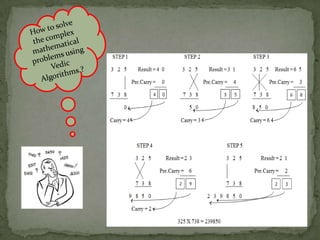

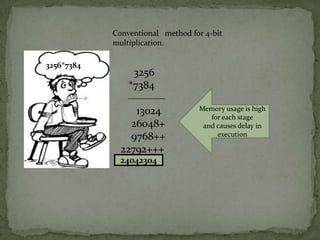

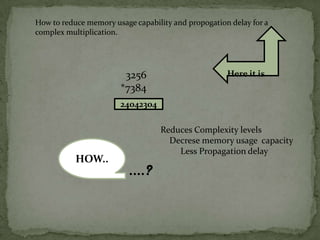

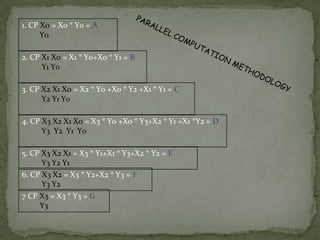

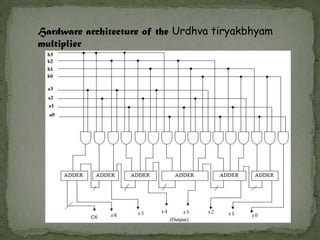

The document discusses different methods for multiplication and their associated delays. It introduces the concept of Vedic mathematics as an ancient methodology for calculations based on 16 formulas. It then describes the Urdhva Tiryakbhyam multiplier technique, which reduces complexity, memory usage, and propagation delay for multiplication by calculating partial products in parallel rather than sequentially. This technique can be implemented in hardware to create an efficient complex multiplier with improved speed and lower power consumption compared to other architectures.